新型氧化铪材料是如何将存储容量提升100倍的

存储技术

描述

材料工程前沿领域的新研究为计算设备性能的真正提高带来了希望。由马库斯-海尔布兰德(Markus Hellbrand)等人领导、与剑桥大学相关的研究小组认为,这种新材料由氧化铪层通过电压变化的钡尖峰隧穿而成,融合了存储器和处理绑定材料的特性。这意味着这种设备可以用于数据存储,其密度是现有存储介质的 10 到 100 倍,也可以用作处理单元。

这项研究发表在《科学进展》(Science Advances)杂志上,为我们提供了一条道路,通过这条道路,我们的计算设备的密度、性能和能效可能会大大提高。事实上,基于这种技术(被称为 "连续范围")的典型 USB存储盘可容纳的信息量是我们目前使用的USB存储盘的 10 到 100 倍。

正如 JEDEC 所指出的,RAM 的密度每四年翻一番,RAM 制造商需要几十年的时间才能最终达到这项技术目前所显示的密度水平。

该设备也是神经形态计算隧道中的一盏明灯。就像我们大脑中的神经元一样,这种材料(被称为电阻开关存储器)有望同时用作存储和处理介质。这在我们目前的半导体技术中是根本不可能实现的:存储单元和处理单元所需的晶体管和材料设计安排是如此不同(主要是在耐久性方面,即不出现性能衰减的能力),以至于目前还没有办法将它们融合在一起。

无法合并意味着信息必须在处理系统和各种缓存(现代 CPU)以及外部内存池(市场上最好的 DDR5 套件)之间不断流动。在计算领域,这被称为冯-诺依曼瓶颈,意思是具有独立内存和处理能力的系统将从根本上受到它们之间带宽(通常称为总线)的限制。这就是为什么所有半导体设计公司(从英特尔到 AMD、Nvidia 以及其他许多公司)都设计了专用硬件来加速这种信息交换,例如 Infinity Fabric 和 NVLink。

问题是,这种信息交换需要付出能量成本,而这种能量成本目前限制了可实现性能的上限。请记住,当能量循环时,也会产生固有损耗,从而导致功耗增加(这是目前硬件设计的硬性限制,也是半导体设计中日益优先考虑的问题)以及热量增加(这是另一个硬性限制,导致人们开发出越来越多奇特的冷却解决方案,试图让摩尔定律继续向前发展一段时间)。当然,还有可持续发展因素:预计在不远的将来,计算所消耗的能源将高达全球能源需求的 30%。

"第一作者、剑桥大学材料科学与冶金学系的马库斯-海伦布兰德(Markus Hellenbrand)博士说:"在很大程度上,能源需求的激增是由于当前计算机内存技术的缺陷造成的。"在传统计算中,一边是内存,一边是处理过程,数据在两者之间来回切换,既耗费能源又耗费时间。

正如你所想象的那样,将内存和处理功能合二为一所带来的好处是相当惊人的。传统的存储器只有两种状态(一或零,即 "二进制 "术语的由来),而电阻开关存储器件可以通过一系列状态改变其电阻。这使它能在更多电压下工作,从而可以编码更多信息。在足够高的水平上,这与 NAND 领域的过程大致相同,每个单元比特的增加与存储器单元设计中解锁的更多可能电压状态相对应。

区分处理和存储的一种方法是,处理意味着信息正在进行写入和改写(加法或减法、变换或重组),其速度与要求的开关周期一样快。存储意味着信息需要在较长时间内保持静态,例如,可能因为它是 Windows 或 Linux 内核的一部分。

为了制造论文中提到的这些 "突触 "设备,研究团队必须找到一种方法来解决材料工程学中的一个瓶颈,即均匀性问题。由于氧化铪(HfO2)在原子层面上不具备任何结构,因此能决定其绝缘性能的铪原子和氧原子是杂乱无章地沉积在一起的。原子结构越有序,电阻就越小,速度和效率就越高。但研究小组发现,在无序氧化铪薄膜中沉积钡(Ba)会产生高度有序的钡桥(或尖峰)。由于其原子结构更加合理,这些桥可以更好地让电子流动。

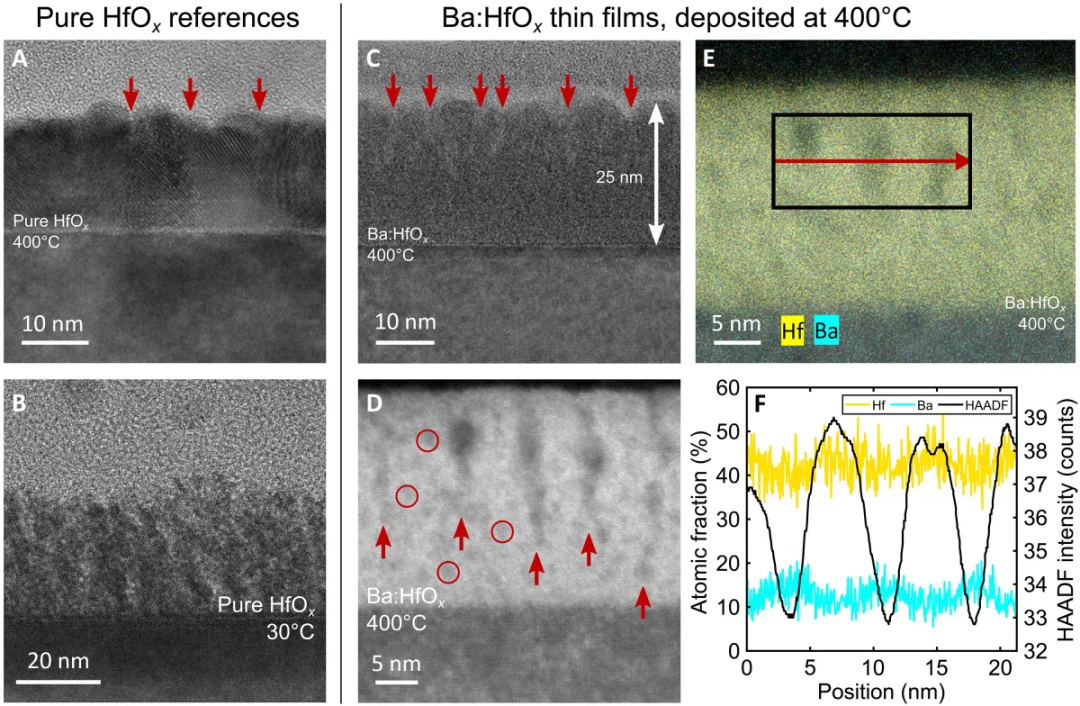

这些照片是用透射电子显微镜(TEM)拍摄的,展示了氧化铪沉积(无序和自然沉积,如图 A)在可动态变化的钡尖峰隧道中的有序性增加。(图片来源:剑桥大学/Markus Hellbrand 等人)

但当研究小组发现他们可以动态改变钡尖峰的高度,从而对其导电性进行精细控制时,有趣的事情就开始了。他们发现,尖峰能以约 20ns 的速度提供切换能力,这意味着它们能在该窗口内改变其电压状态(从而保持不同的信息)。他们发现开关持续时间大于 10^4 个周期,记忆窗口大于 10 个。这意味着,虽然这种材料的速度很快,但它目前能承受的最大电压状态变化次数约为 10,000 次--这并不是一个可怕的结果,但也不是一个惊人的结果。

这相当于 MLC(多层单元)技术的耐用性,这自然会限制它的应用--将这种材料用作处理介质(快速改变电压状态以存储计算及其中间结果)。

粗略地计算一下,大约 20 ns 的切换导致工作频率为 50 MHz(转换为每纳秒的周期数)。当系统全速处理不同状态时(例如,作为 GPU 或 CPU 工作),这意味着钡桥将在 0,002 秒左右停止运行(达到其耐用极限)(请记住,它仅以 50 MHz 运行)。对于处理单元来说,它的性能似乎不够。

但为了存储?好吧,这就是存储容量“密度高 10 到 100 倍”的 U盘的用武之地。这些突触设备可以访问比当今最宽敞的 U盘中最密集的 NAND 技术更多的中间电压状态 - 是其 10 或 100 倍。

谁不想拥有一个 10 TeraByte 甚至 100 TeraByte 的 "USB 7"?

在钡桥的耐久性和开关速度方面还有一些工作要做,但该设计似乎已经是一个诱人的概念验证。更妙的是,半导体行业已经在使用氧化铪,因此需要解决的工具和物流问题就更少了。

不过,这里有一个特别巧妙的产品可能性:想象一下,如果这项技术改进到可以制造并用于设计 AMD 或 Nvidia GPU(这些 GPU 目前的工作频率约为 2 GHz)。在这个世界上,显卡可以重置出厂状态,完全作为内存运行(现在想象一下,显卡有 10 TB 的内存,与我们假设的 U盘相同)。

想象一下,在这个世界上,AMD 和 Nvidia 提供的基本上都是可编程 GPU,基于连续范围的 GPU 芯片在最大存储能力方面进行了产品堆叠(请记住,比当前 USB 密度高 10 到 100)。如果你是一名人工智能爱好者,正试图构建自己的大型语言模型(LLM),那么你可以对 GPU 进行编程,使这些合成设备、这些神经形态晶体管恰到好处地运行处理功能--随着模型复杂度的增加,不知道最终会有多少万亿个参数模型,因此内存将变得越来越重要。

能够决定显卡中的晶体管是完全用作内存还是完全用作养眼放大器以将图形设置提高到 11 个,这完全取决于最终用户;从休闲游戏玩家到高性能计算 (HPC) 安装人员。即使这意味着我们芯片部件的寿命会明显缩短。

无论如何,我们总是在升级它们,不是吗?

不过,我们还是不要妄自菲薄了。尽管这并不像人工智能的发展和监管那样危险,但妄想如此长远也没什么好处。就像所有的技术一样,当它准备好的时候,它就会到来。

审核编辑:刘清

-

索尼半导体激光器技术实现大容量机械硬盘存储容量翻番2024-02-19 1947

-

磁盘存储器的存储容量怎么算2022-01-29 14705

-

DSP--如何计算DDR存储容量2020-09-16 2232

-

估算存储容量2016-03-18 3494

-

存储容量疑问2015-09-01 3119

-

什么是U盘的存储容量2010-01-30 1887

-

磁带机的存储容量2010-01-09 2517

-

数码相机伴侣的存储介质/存储容量2009-12-23 988

-

电脑辞典存储容量2009-12-22 1064

全部0条评论

快来发表一下你的评论吧 !