Clock时钟电路PCB设计布局布线要求

描述

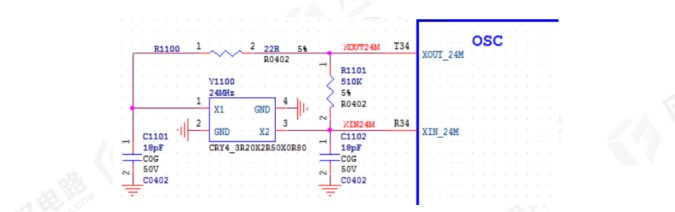

时钟电路就是类似像时钟一样准确运动的震荡电路,任何工作都是依照时间顺序,那么产生这个时间的电路就是时钟电路,时钟电路一般是由晶体振荡器、晶振、控制芯片以及匹配电容组成,如图1所示。

图1 时钟电路

针对时钟电路PCB设计有以下注意事项:

1、晶体电路布局需要优先考虑,布局整体紧凑,布局时应与芯片在同一层并尽量靠近放置,以避免打过孔,晶体走线尽可能的短,远离干扰源,尽量远离板边缘;

2、如果出现晶体电路在布局过程中与芯片放置在不同层的情况,应尽可能的让靠近芯片,让走线变短,并需要将晶体走线全程进行包地处理,以避免被干扰;

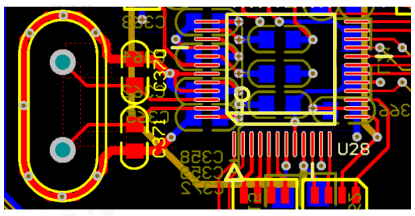

3、晶体以及时钟信号走线需要全程包地处理,包地线每隔200-300mil至少添加一个GND过孔,并且必须保证邻层的地参考面完整,如图2所示;

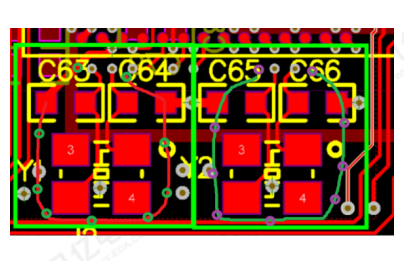

4、晶体的当前层可围绕其进行GND走线形成地环,在地环放置GND过孔,连接到相邻的GND平面层,用以隔离噪声,如图3所示。

图2 晶体布局布线

图3 晶振布局布线

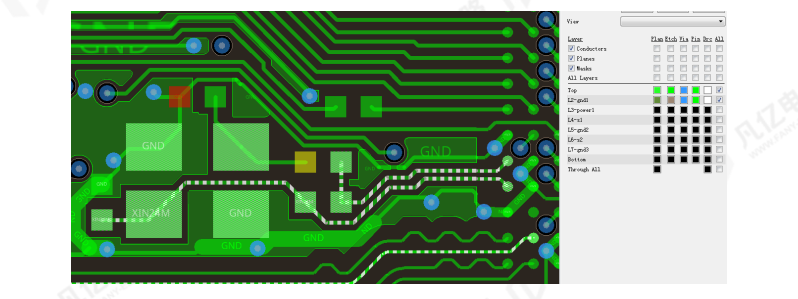

4、时钟走线Xin与Xout以及晶体下方投影区域禁止任何走线,避免噪声耦合进入时钟电路;

6、晶体下面相邻层必须保证完整的参考平面,避免出现跨分割现象,有助于隔离噪声,保持晶体输出,如下图4所示。

图4 第二层为完整的参考平面

声明: 本文凡亿教育原创文章,转载请注明来源!投稿/招聘/广告/课程合作/资源置换 请加微信:13237418207

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- pcb

-

pcb设计布局布线原则及规则2024-01-22 3294

-

Clock时钟电路PCB设计布局布线要求2023-11-16 1193

-

【PCB设计干货】DDR电路的PCB布局布线要求2023-08-24 2782

-

DDR电路的PCB布局布线要求2023-08-18 1382

-

【华秋干货铺】DDR电路的PCB布局布线要求2023-08-17 1846

-

DDR电路PCB布局布线技巧2023-08-16 3875

-

Reset复位电路的PCB布局布线要求2023-08-03 2319

-

PCB设计差分布线要求及操作技巧2023-07-07 7675

-

PCB布局布线技巧104问2023-05-05 1041

-

PCB详细布局、布线设计概述2023-01-09 3826

-

PCB设计布局几个常见的问题你能解决吗2021-11-08 1791

-

pcb设计中的图布线有哪些要求2019-09-02 2906

-

PCB设计布局布线技巧分享2018-09-13 11806

全部0条评论

快来发表一下你的评论吧 !