半导体行业之ICT技术的工艺流程

描述

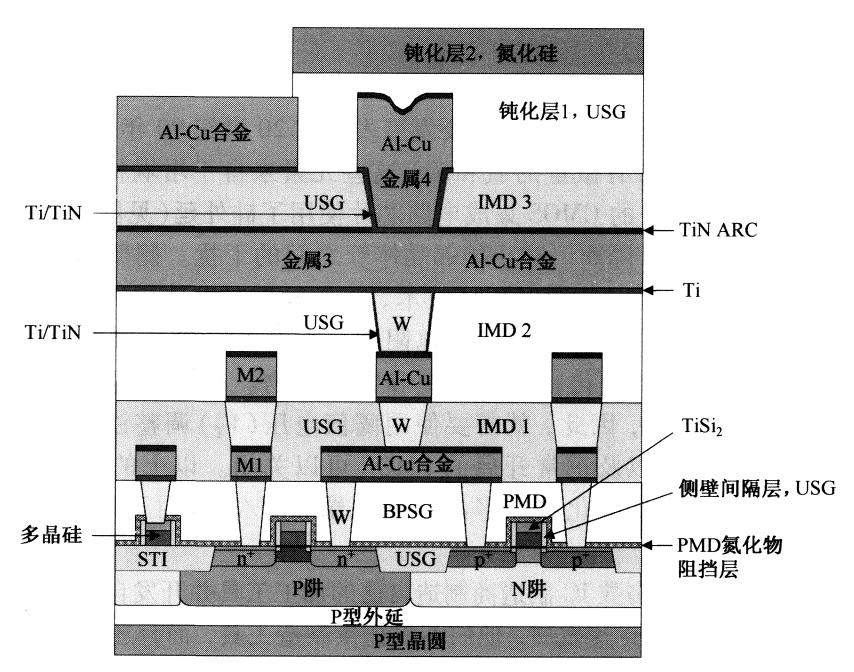

CMOS集成电路芯片加工技术的几个主要发展发生在20世纪90年代。从CZ法单晶硅晶棒上切割下来的硅晶圆都含有微量的氧和碳,这些元素来自于坩埚材料。为了消除这些杂质并提高芯片的性能,先进的CMOS集成电路芯片使用了硅外延(见下图)。浅沟槽隔离(见下图)取代了LOCOS隔离以防止相邻晶体管之间的干扰。侧壁间隔层用于形成抑制亚微米器件热电子效应的轻掺杂漏(LDD)技术,并形成自对准硅化物以减少栅极和局部连线的电阻。由于硅化物具有比多晶硅低的电阻率,所以可以提高器件的速度并降低功耗。20世纪90年代最常用的硅化物是硅化钙和钛硅化物。在此期间,IC芯片的电源电压逐渐从12V降低到3.3V,因此,就需要使用阈值电压调整注入过程,以确保正常关闭的NMOS可以打开,以及正常开启的PMOS可以关闭。以上的工艺流程显示了一个自对准硅化物工艺过程,钛硅化物在多晶硅栅顶端和源/漏同时形成。源/漏硅化物降低了接触电阻。

20世纪90年代以前,大多数IC制造商制造自己的加工工具并开发自己的IC工艺。半导体设备公司在20世纪90年代迅速发展,他们不仅提供制造工具,而且还给IC制造厂提供整合的工艺流程。能够在同一主机下运行不同工艺的配套工具在IC产业界非常受欢迎。因为单晶圆处理系统有更好的晶圆对晶圆均匀性控制,所以被广泛使用。而批处理系统具有较高的产量,所以现在仍然用在许多非关键性工艺中。

20世纪90年代,光刻技术的曝光波长从紫外光(UV)降低到248nm的深紫外光(DUV)范围。因为负光刻胶无法将小于3um的线条图形化,所以光刻中使用了正光刻胶。步进机取代了其他的对准和曝光系统,而整合的晶圆轨道机一步进机系统可以在一个工艺流程中执行光刻胶涂敷、烘烤、对准曝光以及显影。所有的图形刻蚀都是等离子体刻蚀过程,而湿法刻蚀仍然广泛应用于整面全区薄膜去除、测试晶圆的刻蚀和清洗,以及CVD薄膜的质量控制工艺中。立式高温炉因为占据更小的面积和更好的污染控制而成为主导。快速热处理(RTP)系统因为有更好的热积存控制而应用于离子注入后退火和金属硅化物的形成工艺中。溅射取代了蒸发成为金属沉积工艺的一种选择,直流磁控溅射系统是现在最常见的金属物理气相沉积(BVD)系统。

由于晶体管的数量显著增加,单层金属已不再足以连接硅表面上的微电子元器件,因此使用了多层金属互连。常用CVD钨沉积填充狭窄的接触窗和金属层间接触孔,并以栓塞的形式连接不同的导电层。钛和氮化钛被广泛用于阻挡层和钨的附着层。钛也同时用于铝铜合金的焊接层以减少接触电阻,而且氮化钛也成为抗反光薄膜(ARC)的一种选择。

BPSG普遍用于金属沉积前的电介质(PMD)。通过添加硼的硅酸盐玻璃,玻璃化再流动温度可以从约1100摄氏度降低到800摄氏度。这有助于减小热积存,因为当特征尺寸缩小时,热积存也必须减小。PE-TEOS和O3-TEOS工艺广泛用于STI电介质CVD、侧壁间隔层和互连。钨栓塞工艺中,CMP工艺通常用于从晶圆表面移除大量的CVD钧金属层。CMP也广泛用于硅玻璃表面的平坦化,以达到更好的光刻分辨率使后续的金属沉积过程更容易。下图显示了20世纪90年代中期工艺技术制造的CMOSIC芯片横截面示意图。

审核编辑:刘清

-

半导体晶圆制造工艺流程2024-12-24 6031

-

半导体图案化工艺流程之刻蚀(一)2023-06-26 3567

-

半导体行业芯片封装与测试的工艺流程2023-05-29 4205

-

功率半导体分立器件工艺流程2023-02-24 6423

-

晶体管管芯的工艺流程?2019-05-26 3439

-

泛林集团自维护设备创半导体行业工艺流程生产率新纪录2019-05-15 1594

-

半导体知识 芯片制造工艺流程讲解2019-01-26 41629

-

倒装晶片的组装工艺流程2018-11-23 4930

-

半导体工艺流程图2017-01-14 5364

-

半导体封装流程2016-05-26 2165

-

简述半导体超纯水设备工艺流程及标准参考分析2013-08-12 7131

-

PCB工艺流程详解2013-05-22 10141

-

半导体材料的工艺流程2010-03-04 2955

-

仿真技术在半导体和集成电路生产流程优化中的应用2009-08-20 3209

全部0条评论

快来发表一下你的评论吧 !