基于Digilent basys 3开发板的FPGA示波器设计

可编程逻辑

描述

今天给大侠带来基于 FPGA Vivado 示波器设计,开发板实现使用的是Digilent basys 3,话不多说,上货。

需要源工程可以在以下资料获取里获取。

资料汇总|FPGA软件安装包、书籍、源码、技术文档…(2023.07.09更新)

原理介绍

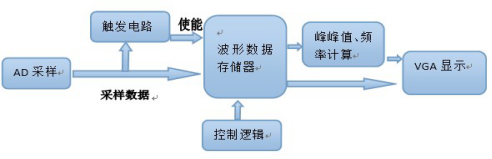

数字存储示波器能够将模拟信号进行采样、存储以及显示。本系统在DIGILENT Basys3上构建了一个简易数字存储示波器,简化框图如下:

原理:首先,AD模块对模拟信号进行采样,触发电路根据采样信号判断触发条件(例如:上升沿触发)。满足触发条件后,连续采样一定数量的点(本系统中为640个点),存储到RAM中。峰峰值、频率计算模块对RAM中储存的波形数据进行计算,得到波形的频率以及峰峰值;VGA模块将波形显示出来,并显示计算得到的峰峰值和频率数值。

本篇通过调用DIGILENT Basys3板上芯片中的ADC模块,对外部电压信号进行采样、存储,并通过VGA显示器将波形显示出来。在DIGILENT Basys3上电之前,需要提前将DIGILENT Basys3与VGA连接好,并准备好一台信号发生器。

操作步骤

一、基于添加文件和IP

1. 新建工程项目

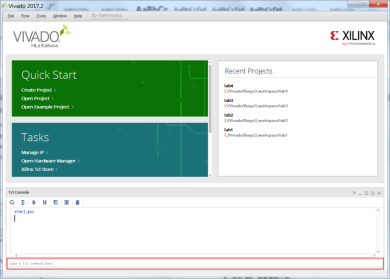

1) 双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2) 点击‘Create Project’,或者单击File>New Project创建工程文件;

3) 将新的工程项目命名为‘lab4’,选择工程保存路径,勾选‘Create project subdirectory’,创建一个新的工程文件夹,点击Next继续;

4) 选择新建一个RTL工程,勾选Do not specify sources at this time(不指定添加源文件),先不添加源文件。点击 Next继续;

5) 选择目标FPGA器件:xc7a35tcpg236-1或Basys3;

6) 最后在新工程总结中,检查工程创建是否有误。没有问题,则点击Finish,完成新工程的创建。

2. 添加已经设计好的IP和源文件

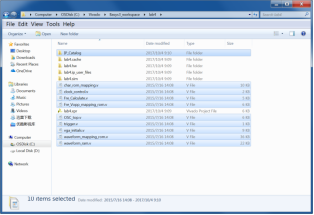

工程建立完毕,我们将设计所需的IP文件夹(IP_Catalog)和实验需要使用的HDL(Verilog)文件复制到已经创建的工程文件夹根目录下:

源文件位于Basys3_workshopsourceslab4SrcHDL_source

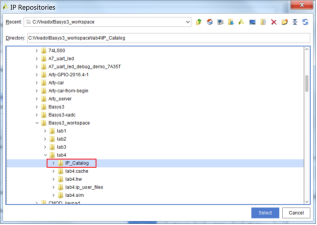

复制完成后,如下图所示:

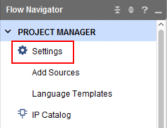

1) 在Vivado界面左侧Flow Navigator中展开PROJECT MANAGER,选择‘Settings’;

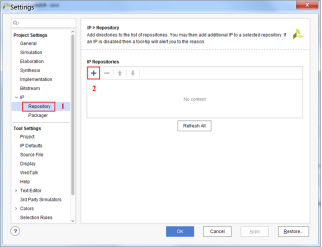

2) 弹出窗口中,在左侧Project Settings中展开IP一项,选择‘Repository’,点击右侧的添加IP;

3) 选择复制到工程文件夹根目录下的IP文件夹;

4) 点击OK完成添加。

5) 添加IP至工程

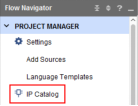

5.1 在Flow Navigator中展开PROJECT MANAGER,选择IP Catalog;

5.2 在右侧IP Catalog窗口的搜索框中搜索‘clocking’,双击‘Clocking Wizard’开始配置IP;

5.3 配置IP

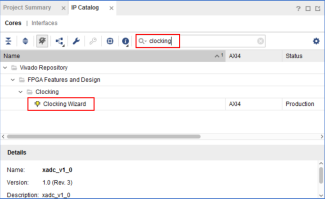

5.3.1 将IP的名字由‘clk_wiz_0’修改为‘clock’

5.3.2 选择‘Output Clocks’,设置7路输出时钟(100MHz、25MHz、12.5MHz、25MHz、50MHz、75MHz、100MHz)

5.3.3 在Enable Optional I/O for MMCM/PLL一项中取消勾选‘reset’和‘locked’选项

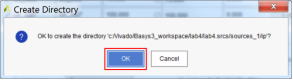

5.3.4 Vivado会创建新的文件夹保存配置完成的IP,点击OK继续

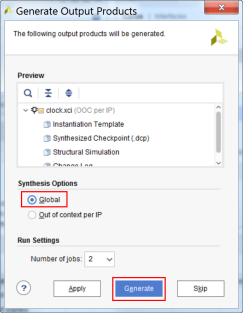

5.3.5 弹出Generate Output Products窗口,在Synthesis Options中选择‘Global’,点击‘Generate’继续。

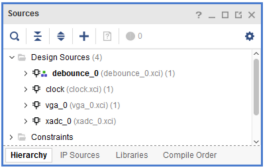

5.4 同样的,依次在IP Catalog窗口中添加debounce、vga和xadc三个IP,使用默认IP设置,无需另外配置,并且Generate Output Products,完成后Sources窗格中如下图所示:

6) 添加HDL文件至工程

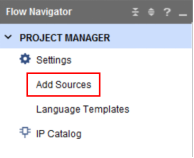

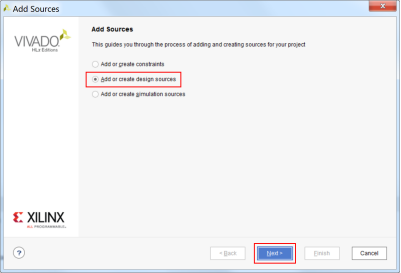

6.1 在Flow Navigator中展开PROJECT MANAGER,选择Add Sources

6.2 在导向窗口中选择‘Add or create design sources’,点击Next继续

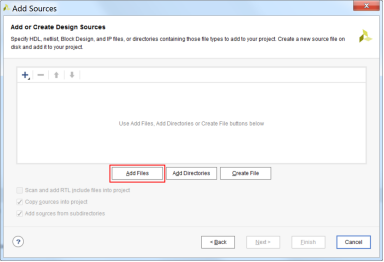

6.3 在Add or Create Design Sources页面中选择‘Add Files’

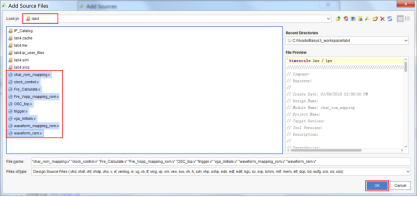

6.4 找到lab4根目录,选中添加所有9个Verilog文件。

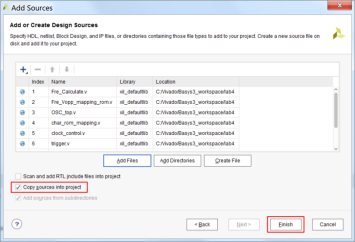

6.5 勾选‘Copy sources into project’,点击Finish完成添加。

6.6 完成后Sources窗格中如下图所示:

7) 添加物理约束(XDC)文件

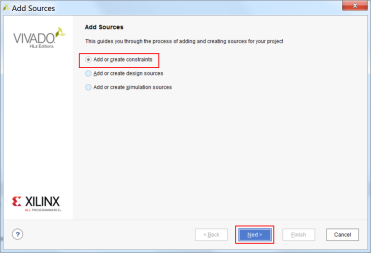

7.1 在Flow Navigator中展开PROJECT MANAGER,选择Add Sources;

7.2 在导向窗口中选择‘Add or create constraints’,点击Next继续;

7.3 在Add or Create Design Sources页面中选择‘Add Files’;

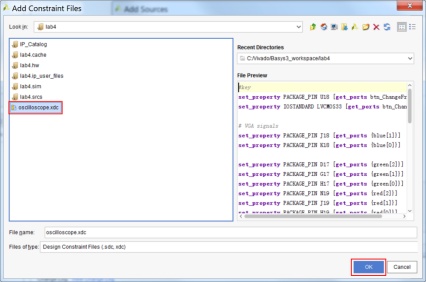

7.4 找到约束文件路径Basys3_workshopsourceslab4SrcConstraint,选中并添加‘oscilloscope.xdc’文件;

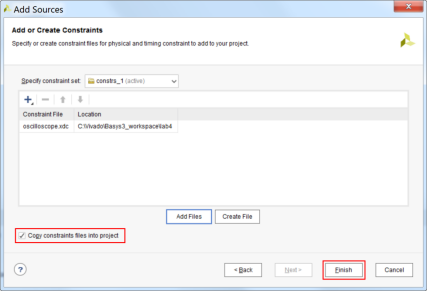

7.5 勾选‘Copy sources into project’,点击Finish完成添加。

3. 综合、实现、生成比特流文件

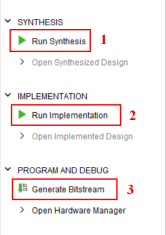

1) 在左侧Flow Navigator中依次点击‘Run Synthesis’、‘Run Implementation’和‘Generate Bitstream’执行综合、实现和生成比特流文件操作。或者,可以直接点击‘Generate Bitstream’,Vivado工具会提示没有已经实现的结果,点击‘Yes’,Vivado工具会依次执行综合、实现和生成比特流文件。

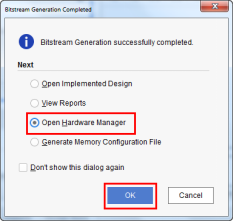

2) 完成后,选择‘Open Hardware Manager’打开硬件管理器。

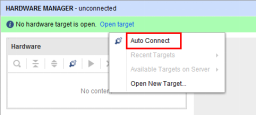

3) 连接Basys3开发板,点击‘Open target’,选择‘Auto connect’。

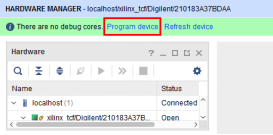

4) 连接完成后,点击‘Program device’。

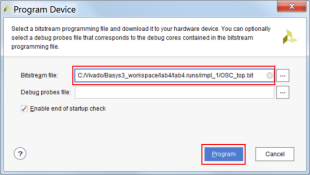

5) 检查弹出框中所选中的bit文件,然后点击Program进行下载。

二、 基于Tcl

1. 运行Tcl,创建新的工程

1) 打开Vivado 2017.2,在界面底部Tcl命令框输入命令;

2) 使用‘cd’命令,进入Oscilloscope.tcl文件所在路径。参考路径:C:Basys3_workshopsourceslab4SrcTcl,在Tcl命令框输入:cd C:/Basys3_workshop/sources/lab4/Src/Tcl (注意:Vivado使用‘/’);

3) 在Tcl命令框中,输入命令:source ./ Oscilloscope.tcl。输入完毕按回车,运行Tcl;

4) 等待Tcl综合、实现、生成比特流文件;

5) 在Flow Navigator中,展开PROGRAM AND DEBUG,点击Open Hardware Manager,点击Open target>Auto Connect 连接Basys3;

6) 点击Program device,选择生成的比特流文件开始下载。

设计验证

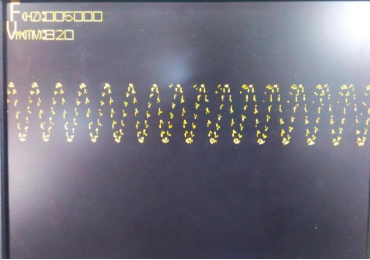

待比特流文件下载完成后,可以将信号发生器的探头连接至Basys3 的JXADC的P极,并将JXADC的N极连接信号发生器的地。本实验,简易示波器的可测电压范围为 0-1V,频率为 4KHz 以下。可以在VGA上观测波形。如果波形显示比较密集,那就需要更改采样时钟,通过按Basys3开发板上的BTNC按键来改变采样时钟,以此来改变波形显示密集程度。

1. 基于Analog Discovery2

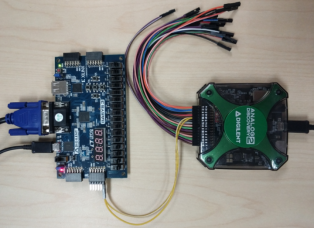

按照下图连接方式,将Analog Discovery2的波形发生器的输出引线W1(黄色)和W2(黄白色)与Basys3的JXADC的pin1和pin7相连接。

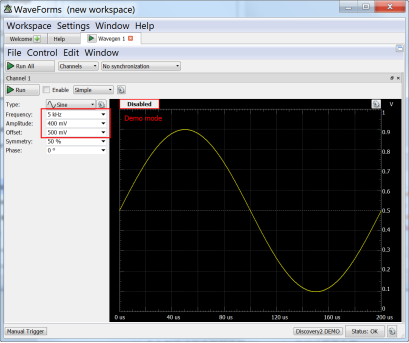

1) 打开WaveForms软件,连接Analog Discovery2设备

2) 在左侧的功能选择栏选择‘Wavegen’,使用波形发生器。

3) 根据本实验示波器设计的输入标准,将波形幅值设置为400mV,直流偏移量设置为500mV,输入的频率可以选择为100H~5kHz之间

4) 点击左上角‘Run All’开始运行。按下Basys3开发板上BTNC按钮进行采样频率调节,在VGA显示器上观察输出结果

2. 基于OpenScope

按照下图连接方式,将OpenScope的波形发生器的输出引线W1(黄色)与Basys3的JXADC的pin1相连接。

1) 打开Digilent Agent

2) 在Windows工具栏右侧,右键Digilent Agent图标,选择‘Launch WaveForms Live’,在浏览器中打开WaveForms Live。

3) 选择在实验二中已经添加的设备,点击连接该设备

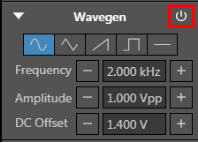

4) 在右侧找到并展开Wavegen(波形发生器),按以下参数进行配置:

选择正弦波

Frequency:2 kHz

Amplitude:1 Vpp

DC Offset:1.4 V

5) 点击右上角开关按钮,打开波形发生器。

6) 在VGA显示器上观察输出结果,可以使用Basys3开发板上BTNC按钮进行采样频率调节。

编辑:黄飞

-

basys2开发板说明书2025-06-08 540

-

BASYS 3开发板的电路原理图免费下载2020-06-18 1824

-

digilent Artix-7 FPGA训练板介绍2019-11-20 3335

-

digilent Artix-7 FPGA开发板简介2019-11-19 4331

-

digilent Spartan-3E FPGA训练板介绍2019-11-14 3873

-

Basys2 FPGA开发板主板的电路原理图免费下载2019-06-21 1961

-

基于FPGA vivado 17.2 Basys3 示波器实验设计2017-12-22 9636

-

开发者福利 一文带你了解Digilent Arty S7 FPGA开发板2017-09-27 9187

-

出手一块全新的FPGA开发板 Xilinx Basys 3 原装未拆过2017-09-10 4541

-

Digilent公司发布新款FPGA开发板2017-02-09 1847

-

基于Vivado 的Basys3开发板的解码教程2016-08-03 1815

-

Digilent公司basys2开发板的全套开发例程2016-07-29 3021

-

Xilinx 公司BASYs开发板自带的Demo程序2016-06-07 954

-

Digilent公司推出新型FPGA硬件开发平台:NEXYSTM3开发板2011-08-22 3005

全部0条评论

快来发表一下你的评论吧 !