fpga系列产品的漏洞机理分析

可编程逻辑

描述

各位亲爱的FPGAer老铁,又到了令人愉悦的周五了,作为回归后的第一篇文章,小弟我彻夜难眠,一直在想写什么精彩的内容才能对得起自己吹的牛皮。真的是翻来覆去,思绪万千,翻开有道、印象、github、PornHxx,最终决定还是给大家讲一个大家都很关心的事情——《如何守住自己的秘密》。

很多小伙伴就会问了,是什么秘密呀,《不能说的秘密》还是《维多利亚的秘密》,快点快点,小马扎已经备好了,我要吃瓜!!!

我相信作为在座的每一位FPGAer都是一名优秀的时间管理大师,毕竟时序约束那点破事(点赞转发过2000,马上安排),咱不是天天在玩嘛。我觉得既然咱们花了那么多时间管理的设计,如何能保证它的秘密更应该值得深入研究。

咱们华夏子弟个顶个的聪明,个顶个的比别人努力,如今这么卷的行业赛道里,如何保证自己辛辛苦苦堆出来的优秀设计不被别人剽窃,当然了,更不能让别人反向出咱自己写的垃圾代码,不然多丢面呀,以后还混不混了。

今天我就给大家介绍一下和一位FPGA行业大牛讨论关于加密的内容,整理出来分享给大家,希望大家都能打起100万的精神,守卫自己的秘密花园。

01

设计加密简介

很多小伙伴对于加密的概念都不陌生,小到我们日常使用的银行卡加密,手机机密(密码、生物特征加密)、门锁加密,大到国家机密等,无一不是加密技术保护着我们个人的生命和财产安全。

今天我们主要介绍一下关于FPGA加密技术的介绍:

把自己的设计封装成ip,提供license的方式保护自己的设计;

把自己的设计封装成网表,保护自己的源代码设计;

把自己的设计代码故意改的乱七八糟,增加阅读难度和可行性(恶心自己也恶心别人),主打一个刺激。

为了保护自己辛辛苦苦,熬夜掉头发搞出来的设计,能使用的手段必须统统使出来。但是,你以为这样就安全了吗?

当初小弟我也以为自己的设计经过上述的操作,基本万无一失,谁来都无法剽窃我的设计,除非给的足够多!自从和大牛聊完以后,发现自己的设计在FPGA芯片设计大牛眼里,我在裸奔!

大牛给我说,其实对于前面说到的任何一种加密内容,最后都会落盘到bit位流中,对于他们FPGA芯片设计人员,有这份位流已经足够破解我的设计。

所以,为了防止FPGA泄密,保护最终的bit位流才是关键所在。

大牛给我分享了一个链接,我这才知道,原来国际知名大厂AMD-XILINX的7系列以及之前的FPGA系列产品,在bit位流安全性存在严重的缺陷和漏洞,今天我就带着大家深度扒一扒。

1 存在StarBleed硬件漏洞

2020年4月,来自德国的研究者在论文“The Unpatchable Silicon A Full Break of the Bitstream Encryption of Xilinx 7-Series FPGAs”中披露了一个名为“StarBleed”的漏洞,它存在于赛灵思的Virtex、Kintex、Artix、Spartan等全部7系列FPGA中。通过这个漏洞,攻击者可以同时攻破FPGA配置文件的加密和鉴权,由此可以获得用户的FPGA设计同时可随意修改FPGA中实现的逻辑功能。严重的是,这个漏洞并不能通过软件补丁的方式修复。漏洞的发现者已于2019年9月将这个漏洞知会了赛灵思,并在第二天就获得了赛灵思的承认。 该漏洞攻击的成本非常低,无需特别深奥难懂的专业知识,一般的硬件工程师就能按照论文完成破解。AMD-XILINX主流产品XC7K325T仅三小时即能完成的全位流破解。

2 不抗DPA攻击

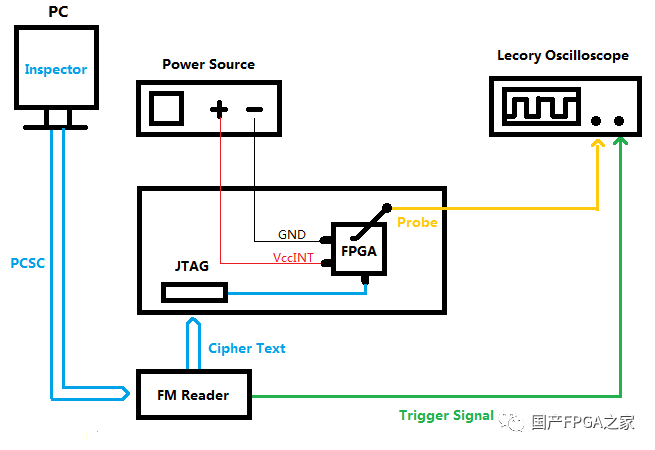

AMD-XILINX FPGA对加密位流的解密方案采用了CBC-AES,在实现中并没有加入侧信道的防护措施,因此理论上就存在被侧信道攻击的风险。早在2011年,Moradi(StarBleed漏洞的第二发现者)等就在赛灵思 Virtex-II上使用侧信道攻击获得了位流的加密密钥。接下来,他又使用功耗侧信道攻击了赛灵思 Virtex-4、Virtex-5以及Altera Stratix II的加密位流,并获得了加密密钥。2016年,他又使用电磁侧信道攻击方法,成功攻击了Virtex-5、Spartan-6、Kintex-7和Arix-7 由于大牛是国内某FPGA大厂研发中心的核心设计人员,在小弟我三番五次,不要脸的请求下,给我展示了国内某安全实验室团队完成的XILINX XC7K325T的DPA侧信道攻击。 该攻击方法为采用Langer 的电磁探头采集EM信号,采集EM信号需要对FPGA进行开盖,去除表面金属封装,发现在FPGA芯片边缘的电容上可以找到较好信噪比的波形,下图是实际的采集位置和使用的U5-2的EM Probe。

测试平台架构

FPGA芯片开盖(V4)

信号采集位置(K7)

上文给兄弟们介绍了AMD-XILINX的7系列以及之前的FPGA系列产品的漏洞机理,接下来给大家展示一波,DPA攻击方法:

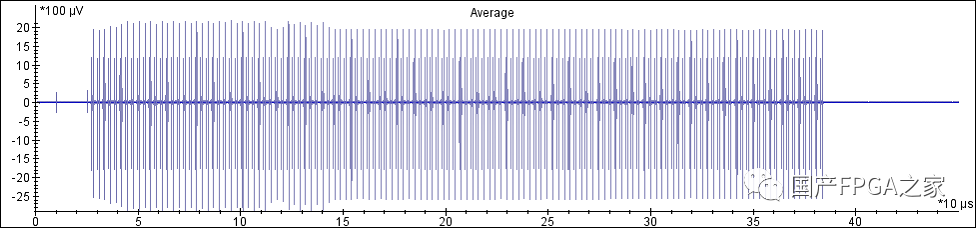

1)信号处理 使用U5-2 型号的EM探头采集8万条K7解密的曲线,采样率1G,采样数据FFT分析后进行滤波处理。 取2000条曲线进行平均,曲线如下:

在曲线下半部可以看到AES执行的26个尖峰毛刺,非常明显。 2)已知密钥分析 通过已知密钥分析,来定量密钥与泄露的关系 3)选择密钥攻击 4)攻击结论: 本次实验,使用EM Probe采集Xilinx Virtex-4和Kintex-7系列的FPGA解密比特流过程的曲线(V4:需要1.25*8=10万条左右;需要K7:15*8=120万条左右),经过信号处理后可以在黑盒测试条件下通过选择密文的方式,对解密过程进行CPA分析,从而恢复解密密钥。

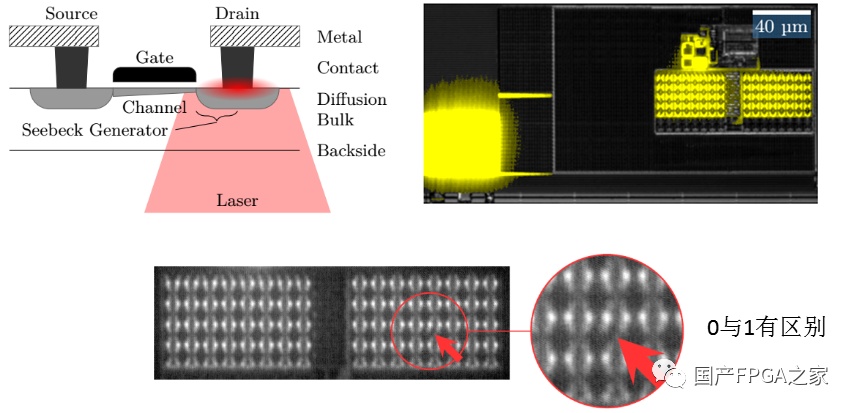

3 密钥存储方式不安全

AMD-XILINX FPGA密钥存储支持两种模式: 1)BBRAM电池供电存储 已有公开文献发表,可通过激光注入读取BBRAM中保存的明文密钥,且BBRAM需要电池供电,应用可靠性大大降低。

2)片上熔丝EFUSE存储 同样片上熔丝可通过简单的暴力逆向工程,获得密钥。

4 加密结束语

咱们说了这么多加密内容和破解加密的方法,就是为了让各位老铁知悉,一旦让别人窃取到FPGA密钥,就可以轻松破解出明文的bit位流,自然而然的是有方法反向出咱这千辛万苦设计出来的代码,从而让我们丧失商业竞争力和能动性。

加密寄语

面对这么严重的FPGA位流安全漏洞,很多AMD-XILINX FPGA的忠实粉丝却没有任何怨言,不是店大欺客,而是2020前,真的没法弥补,甚至无法替代。

话都到这份上了,各位FPGAers肯定会问,那这咋办呢,如果有加密需求的设计,那这X家又没有补丁可以把这个漏洞打上,这以后还能不能用他家的产品了。

万水千山总是情,问问本编行不行,这两年俺也不是白白下海的,随着国产化的浪潮大趋势,国内的FPGA厂家踏着集成电路法阵的浪潮来了,后续有机会可以找机会与他们交流,且看他们是如何解决加密问题!

编辑:黄飞

-

Intel FPGA系列产品详解2021-10-08 12222

-

高云半导体推出最新安全FPGA系列产品2019-07-03 1581

-

54600系列产品说明2019-01-21 1666

-

8590L便携式频谱分析仪系列产品概述2019-04-24 1978

-

客户为什么会选择3700系列产品?2021-05-07 1949

-

RX系列产品分别分为哪几种?RX系列产品具备哪些功能?2021-07-01 3624

-

硬件芯片漏洞的机理和危害2021-07-28 1871

-

分析仪系列产品选型指2010-04-02 365

-

NI FlexRIO系列产品将PXI Express技术引入2010-03-02 761

-

ASDX系列产品手册2016-04-28 863

-

AGM国产高端FPGA系列产品线发布,国产FPGA芯片市场再进一步2018-07-12 12694

-

Achronix推出Speedster7tFPGA系列产品 简化设计FPGA灵活性2019-05-27 4765

-

Intel FPGA系列产品介绍2021-09-30 5648

-

FPGA产品GW1N 1系列产品Pinout手册2022-09-14 588

-

AMD推出Spartan UltraScale+ FPGA系列产品2024-03-07 1698

全部0条评论

快来发表一下你的评论吧 !