芯片工艺的"7nm" 、"5nm"到底指什么?

描述

近几年,芯片产业越来越火热,一些行业内的术语大家也听得比较多了。那么工艺节点、制程是什么,"7nm" 、"5nm"又是指什么?

1.摩尔定律

1965年,英特尔公司(Intel)的创始人之一的戈登·摩尔应邀为《电子学》杂志35周年专刊写了一篇观察评论报告,题目是:“让集成电路填满更多的元件”。在摩尔开始绘制数据时,发现了一个惊人的趋势:每个新芯片大体上包含其前任两倍的容量,每个芯片的产生都是在前一个芯片产生后的18-24个月内。如果这个趋势继续,计算能力相对于时间周期将呈指数式的上升。

即著名的摩尔定律,归纳起来主要有3种版本:

1、集成电路芯片上所集成的电路的数目,每隔18个月就翻一番

2、微处理器的性能每隔18个月提高一倍,而价格下降一半

3、用一美元所能买到的计算机性能,每隔18个月翻两番

摩尔定律并不是一个物理或数学定律,只是一个总结。

根据摩尔定律,每隔18个月,芯片规模不变的情况下,芯片面积是原来的二分之一。

假设新工艺的良率和成本与原来一致,理论上来说,相同的晶圆,芯片的产量翻倍,成本减半。而且采用新工艺的芯片,性能、功耗、面积都更优。

制程一般按照“数字+nm”的表达形式,在早期,制程节点命名与晶体管的Gate Length和Half-pitch Size有关。

首先对于二极管和由Metal Wire组成的集成电路,Gate Length表示二极管Gate极的宽度,而Half-pitch Size代表的是芯片内部互联线间距离的一半,也即光刻间距的一半。

总的来说,制程节点越小意味着晶体管越小、速度越快、能耗表现越好。

为什么台积电、三星都有10nm,7nm,5nm这些制程节点呢,这些节点是否有一定的规律?

首先回到摩尔定律,下一代工艺的芯片面积是上一代的一半。

假设按照正方形来计算,设两代工艺的晶体管尺寸分别为x,y。可得

可知下一代工艺晶体管的尺寸基本上是上一代工艺的0.7。

下图是目前主流制程节点的半导体制造厂商情况,从180nm开始算,基本上符合这种数学关系,这就是摩尔定律的伟大之处,几十年前总结的规律和现在的芯片制程几乎吻合。

目前台积电和三星最先进的工艺节点是5nm, 那么可以推算出接下来的工艺就是3nm,2nm,1nm。

2.优化再优化

但是上图中有几个数字很显得与众不同,就是40nm、28nm、20nm、14nm。这涉及到芯片制造厂的常用手段——shrink。

芯片工艺的研发需要很大的成本,尤其是芯片制程的不断缩小,研发成本可以用恐怖来形容,比如研发28nm工艺,需要耗费5130万美元;而到了7nm节点,费用将提升到2.97亿美元。

如果说可以在当前工艺节点上持续优化,能最大程度地利用原有投入成本。

Shrink本质上就是利用MASK等比例缩小晶体管的尺寸,再通过一些方式修修补补,使其仍然能够正常工作。

这些shrink后的工艺节点,也被人称为半节点。目前shrink大约可以把晶体管尺寸缩小为原来的0.9。

那么40nm就是45nm shrink后的半节点(它们可认为是同一工艺节点,只是厂家进行了优化),以此类推。

优化后的半节点更成熟,优势更多,慢慢厂家就主推这些半节点了。所以14nm要比16nm更多地出现我们的视野中。

3.我们被“骗”了

但是,一个原子直径大约为0.1nm,那么现在的5nm工艺岂不是只有50个原子的长度,是否有些夸张了。

在前面说过制程节点与晶体管的Gate Length和Half-pitch Size有关,实际上到了28nm以下,由于采用finfet这些新技术,两者基本就匹配不上了。

在摩尔定律提出的前三十年,新工艺制程的研发并不困难,但随着特征尺寸越来越接近宏观物理和量子物理的边界,现在高级工艺制程的研发越来越困难,研发成本也越来越高。

如果工艺制程继续按照摩尔定律所说的以指数级的速度缩小特征尺寸,会遇到两个阻碍,首先是经济学的阻碍,其次是物理学的阻碍。

经济学的阻碍是,随着特征尺寸缩小,由于工艺的复杂性设计规则的复杂度迅速增大,导致芯片的成本迅速上升。至于物理学的障碍主要来源于量子效应和光刻精度。几十个原子那么厚,会产生诸多量子效应,导致晶体管的特性难以控制。

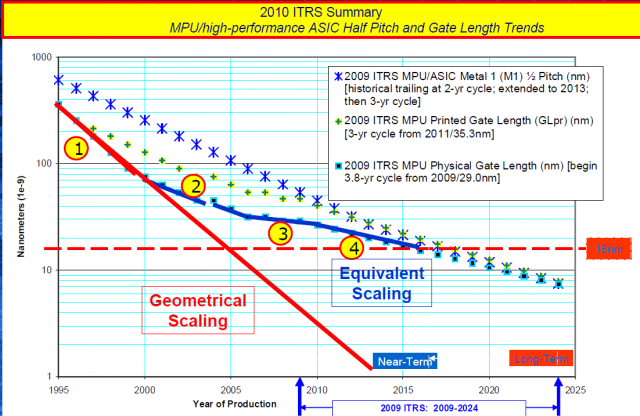

如果保持节点名称和实际特征尺寸同步,会如下图红线所示,在2015年,芯片工艺的实际尺寸就会达到1nm。

但目前的工艺曲线和蓝线更符合。

那也就是说摩尔定律早就失效了?事实上摩尔定律在不停地维护和修正,主要由ITRS(International Technology Roadmap for Semiconductor)来制定来讨论合适的制程发展速度。ITRS制定了一个节点介绍的总体路线图以及这些节点将针对的功能尺寸,这个路线图为芯片制造行业的上下游(光刻设备厂家、刻蚀设备厂家、材料厂家、大学和研究机构等)提供导引作用。

通过修正,工艺节点和晶体管尺寸并不是完全一致了。

4.营销还是营销

所以现在的7nm、5nm就是个数字,仅此而已,和技术实际没啥联系。

总的来说,这就是一种芯片制造行业面向大众一种默认“营销”手段。

早年间英特尔还是比较坚持初心的,将名称和制程尽可能联系起来(但也没有完全遵循尺寸模型),所以就有了“14nm+++”挤牙膏传说。

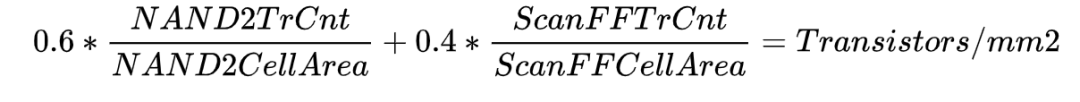

英特尔说了,大家不要瞎扯,什么7nm、5nm的,我们直接看单位面积的晶体管数量。也就是下面的公式

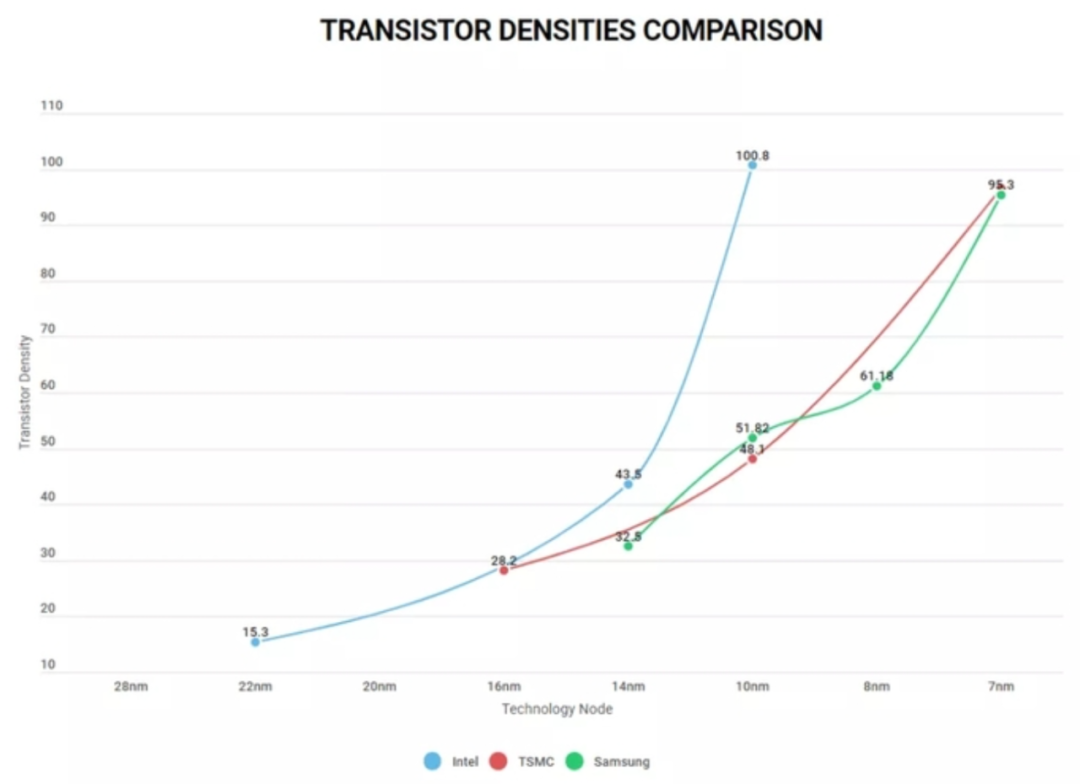

虽然英特尔的10nm和台积电的7nm看起来是两代,但晶体管密度基本一样,如下图。

但是这对消费者来说太复杂了,怎么能有5nm、3nm宣传效果好呢。

台积电7nm、5nm口号喊得十分响亮啊,眼看要领先英特尔10nm“两三代”工艺了。

再加上近两年采用了台积电工艺的AMD处理器(除晶体管密度外,还有其他的一些关键参数决定了一款处理器的性能)让广大消费者喊出了“AMD,YES!”。

英特尔也慢慢坐不住了,去年就改变了自家的命名规则,直接宣称4年内进入“埃米”时代(比小更小)。

摩尔定律通过修正依旧在发挥作用,但工艺制程的更新换代越来越慢了。

据说明年苹果的A17芯片将采用台积电的3nm工艺,但现在我们知道3nm仅仅就是个代号,比现在5nm技术更新了一代,和数字上的3nm没什么关系了。

审核编辑:刘清

-

教你如何搭建浅层神经网络"Hello world"2020-12-10 1668

-

"STM32F0 Error: Flash Download failed - ""Cortex-M0""解决"2021-12-01 5570

-

科沃斯扫地机器人通过TÜV莱茵"防缠绕"和"高效边角清洁"认证2024-03-17 1852

-

全方位精准测量技术助力:中国经济加力发展向前"进"2024-07-15 2537

-

隧道管廊变压器局放在线监测:为地下"电力心脏"装上智能听诊器2025-04-09 1012

-

电缆局部放电在线监测:守护电网安全的"黑科技"2025-04-14 1119

-

仓储界的"速效救心丸",Ethercat转PROFINET网关实战案例2025-05-11 921

-

人形机器人为什么要定制? ——揭秘工业场景的"千面需求"2025-06-10 1506

-

为什么GNSS/INS组合被誉为导航界的"黄金搭档"?2025-07-09 1167

-

光耦合器:电子世界的 "光桥梁"2025-08-22 1175

-

"Access violation" 错误,复位位置,重新打印2025-11-08 757

-

L3试点落地,和芯星通如何成为车企突围的"隐形守护者"?2026-01-04 769

-

机械臂越复杂越"卡顿"?别让控制器拖了后腿2026-02-02 771

-

选EtherCAT模块,别只看价格,先看"体检报告"2026-02-04 483

-

从"替代人力"到"智能协同":履带式巡检机器人的产业跃迁2026-02-05 436

全部0条评论

快来发表一下你的评论吧 !