如何实现基于FPGA Vivado的74系列IP封装呢?

可编程逻辑

描述

操作步骤

1. 新建工程项目

1) 双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2) 点击‘Create Project’,或者单击File>New Project创建工程文件;

3) 将新的工程项目命名为‘lab3’,选择工程保存路径,勾选‘Create project subdirectory’,创建一个新的工程文件夹,点击Next继续;

4) 选择新建一个RTL工程,勾选Do not specify sources at this time(不指定添加源文件),先不添加源文件。点击 Next继续;

5) 选择目标FPGA器件:xc7a35tcpg236-1或Basys3;

6) 最后在新工程总结中,检查工程创建是否有误。没有问题,则点击Finish,完成新工程的创建。

2. 添加源文件

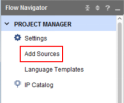

1) 在左侧Flow Navigator中展开PROJECT MANAGER,选择‘Add Sources’;

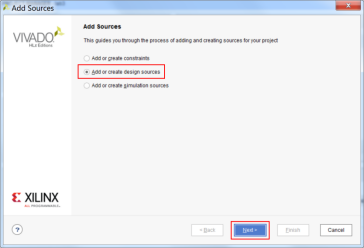

2) 在Add Sources窗口中,选择‘Add or create design sources’,点击Next;

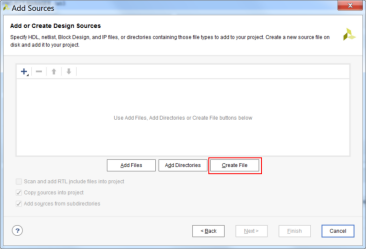

3) 点击‘Create File’,创建源文件;

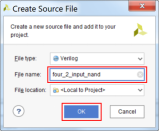

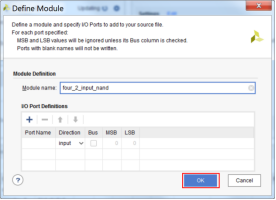

4) 将源文件命名为‘four_2_input_nand’,点击OK;

5) 点击Finish,完成源文件创建;

6) 在模块端口(I/O)定义窗口不做设置,点击OK继续;

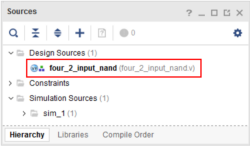

7) 在Sources窗格中,双击打开‘four_2_input_nand.v’文件,开始编辑;

8) 在右侧的文本编辑框中,编辑代码如下图所示:

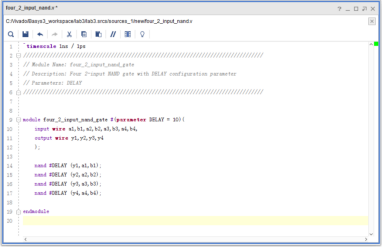

源代码如下:

`timescale 1ns / 1ps module four_2_input_nand_gate #(parameter DELAY = 10)( input wire a1,b1,a2,b2,a3,b3,a4,b4, output wire y1,y2,y3,y4 ); nand #DELAY (y1,a1,b1); nand #DELAY (y2,a2,b2); nand #DELAY (y3,a3,b3); nand #DELAY (y4,a4,b4); endmodule

9) 编辑完成后,Ctrl+S保存;

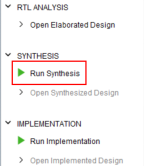

10) 在Flow Navigator中,展开SYNTHESIS,点击‘Run Synthesis’。弹出窗口使用默认选项,点击OK开始综合。

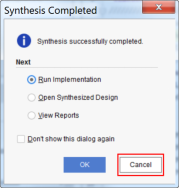

11) 综合完成后,点击‘Cancel’关闭窗口。

3. IP封装

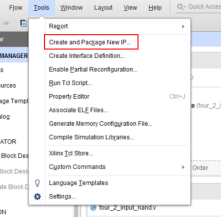

1) 在顶部工具栏中,点击Tools>Create and Package New IP;

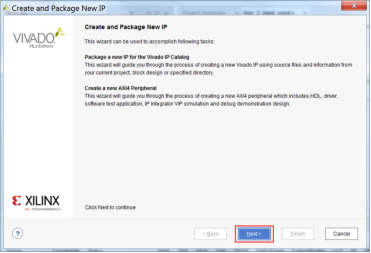

2) 弹出的向导窗口,点击Next继续;

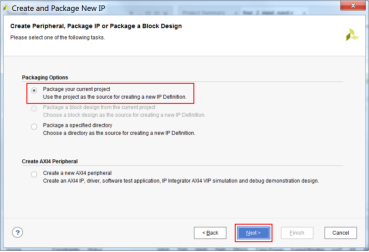

3) 选择对当前工程进行封装,点击Next继续;

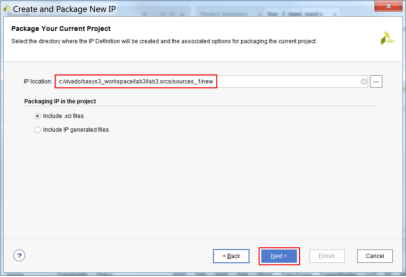

4) 选择IP保存路径,保持默认设置,点击Next继续;

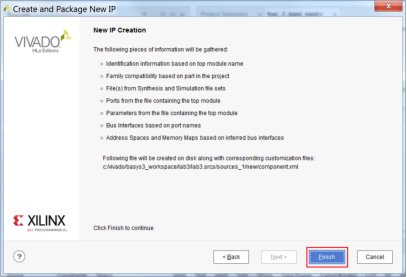

5) 点击Finish完成设置;

6) 设置IP参数;

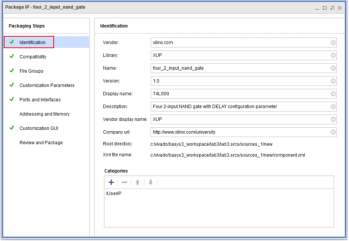

6.1 在右侧Package IP窗口中,选择Identification,按下图设置:

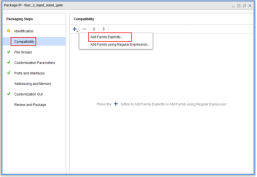

6.2 选择Compatibility,如果已经存在artix7、kintex7、spartan7和zynq可以略过此步。否则需要按以下步骤添加:

6.2.1 选择‘Add Family Explicity’

6.2.2 在弹出窗口中勾选相应的系列,Life-cycle选择‘Production’。

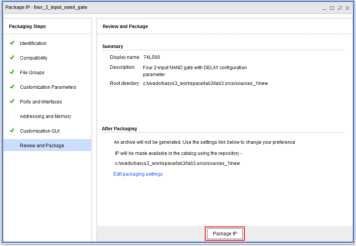

6.3 点击OK完成添加,选择Review and Package,点击‘Package IP’完成对74LS00 IP的封装。

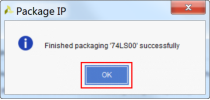

6.4 完成后,系统提示封装成功。

4. 基于Tcl的封装流程:

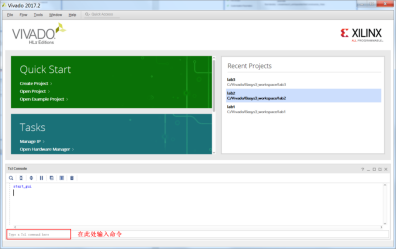

1) 打开Vivado 2017.2,在底部Tcl Console中依次执行下列步骤完成对74LS00 IP的封装;

2) 在命令框依次输入如下命令:

2.1 cd C:/Basys3_workshop/sources/lab3/

进入到工作文件夹,文件夹中包含封装IP所需的源文件

2.2 set ip_name 74LS00 设置IP名称

2.3 set source_files four_2_input_nand.v 设置源文件

2.4 set description "Four 2-input NAND gate with DELAY configuration parameter" 对IP进行功能描述

2.5 set readme_file readme.txt 添加readme文本文件

2.6 set logo_file xup_IPI.png 设置IP logo图片

2.7 source ./package_ip.tcl

运行工作目录下的Tcl文件,进行IP封装

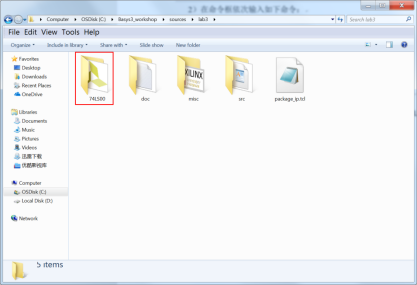

1) 完成之后,封装完成的74LS00 IP保存在C:/Basys3_workshop/sources/lab3/74LS00文件夹内

审核编辑:刘清

-

使用Python/MyHDL创建自定义FPGA IP2026-04-09 454

-

Vivado FIR IP核实现2025-03-01 3208

-

Vivado中BRAM IP的配置方式和使用技巧2023-08-29 11012

-

使用VIvado封装自定IP并使用IP创建工程2022-04-21 8302

-

一文解析Vivado的三种封装IP的方式2021-08-10 9771

-

FPGA实现基于Vivado的BRAM IP核的使用2020-12-29 13683

-

VIVADO从此开始高亚军编著2020-10-21 6053

-

怎么在Vivado HLS中生成IP核?2020-03-24 3933

-

Vivado将模块封装为IP的方法介绍2018-06-26 9177

-

基于 FPGA vivado 2017.2 的74系列IP封装2017-12-20 7375

-

在Vivado下利用Tcl实现IP的高效管理2017-11-18 6231

-

基于Vivado将verilog代码封装成IP的步骤2017-09-15 2501

-

vivado带ip核的工程封装2017-07-14 4477

-

VIVADO——IP封装技术封装一个普通的VGA IP-FPGA2017-02-28 1460

全部0条评论

快来发表一下你的评论吧 !