FPGA时序分析-建立时间和保持时间裕量都是inf怎么解决呢?

可编程逻辑

描述

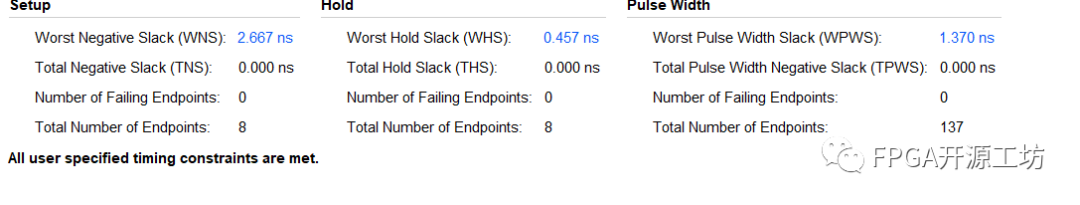

今天有个小伙伴遇到一个问题,就是在vivado里面综合后看到的建立时间和保持时间裕量都是inf,我们来看看怎么解决这个问题。

实验一:

module testMem(

input clk,

input [9:0] addr,

input we,

input [7:0] wdata,

output reg [7:0] rdata

);

reg [7:0] mem [1023:0];

reg [7:0] data;

reg [7:0] data1;

reg [7:0] data2;

reg [7:0] data3;

always@(posedge clk)begin

if(we)begin

mem[addr] <= wdata;

end

end

always@(posedge clk)begin

rdata <= mem[addr];

end

endmodule

时序约束如下:

create_clock -period 5.000 -name sys_clk [get_ports clk]

set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVCMOS33} [get_ports clk]

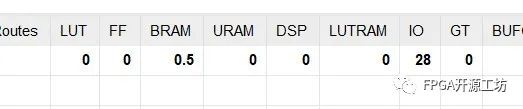

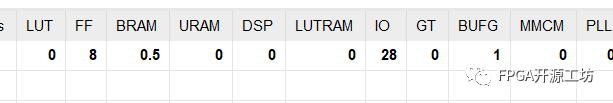

代码非常简单,大家一看就可以知道,这段代码会被映射到一个Bram上。综合后的资源报告也印证了我们的想法:

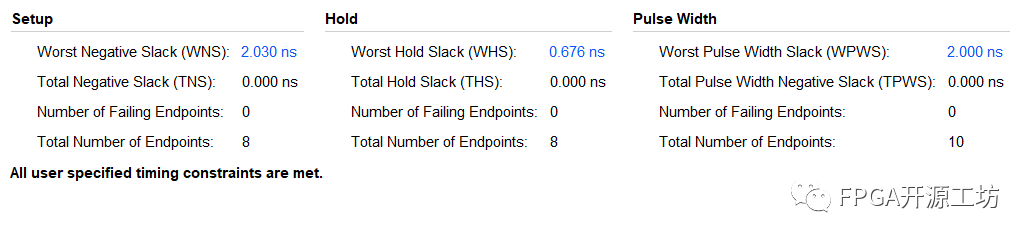

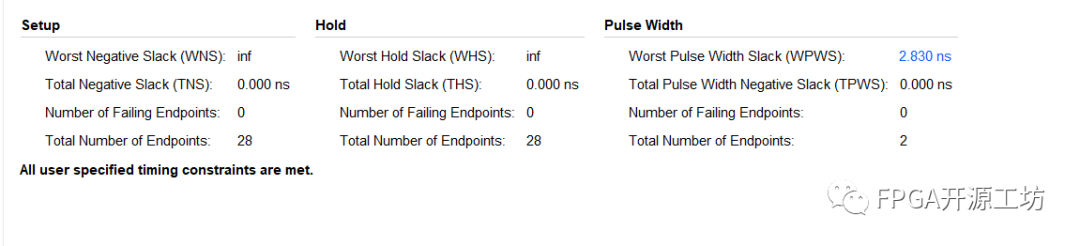

但是看时序分析:

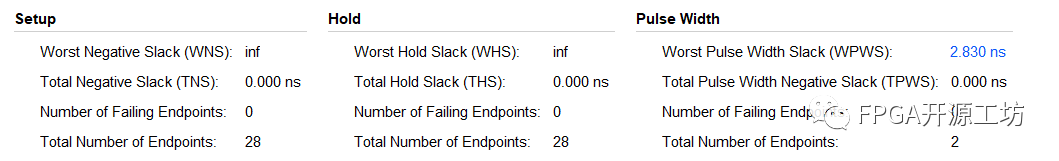

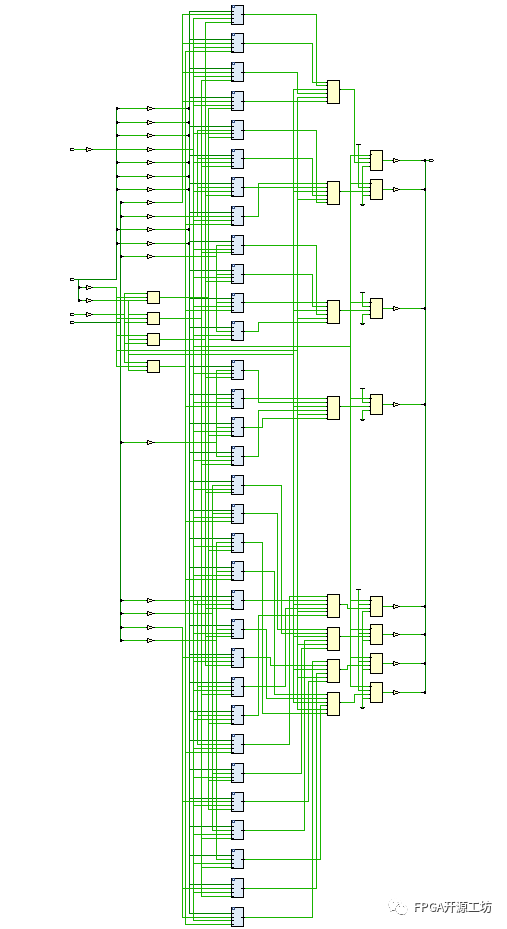

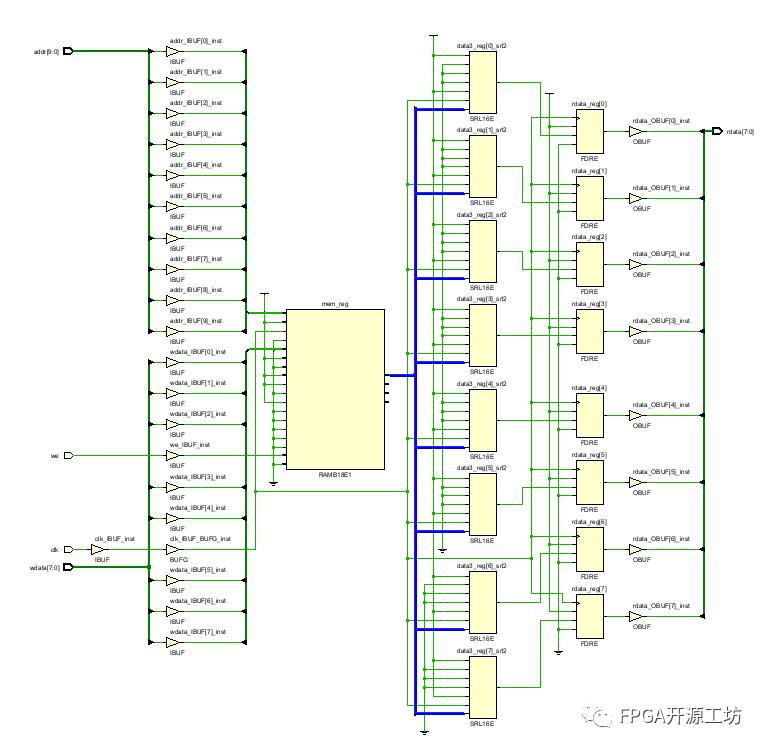

是不是感觉很奇怪明明我们约束时钟了,为什么时序分析后是inf呢,我们来看一下他综合后的框图就明白了。

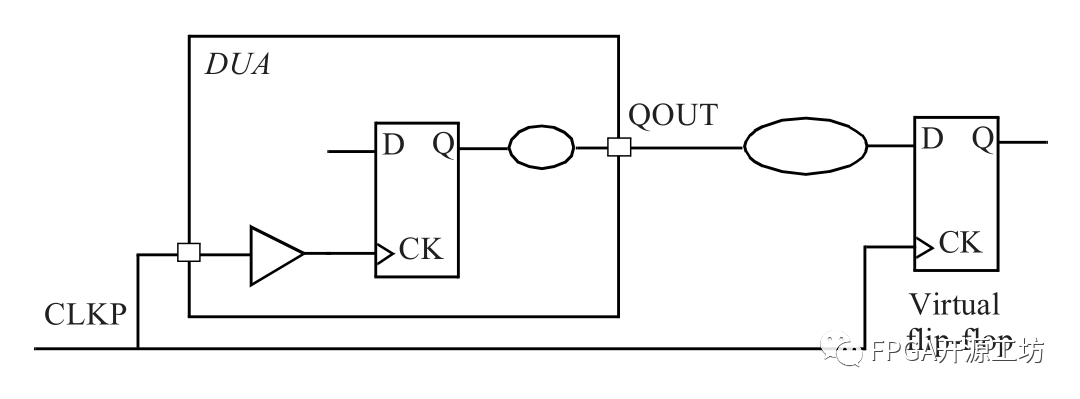

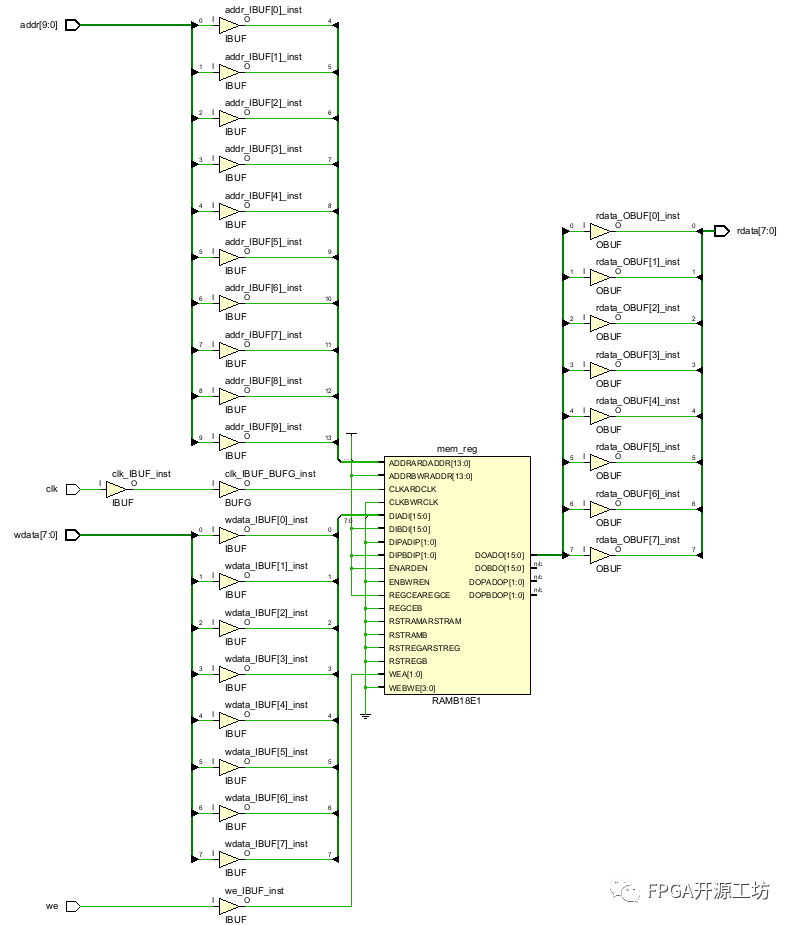

可以看到在上图里面,clk只和bram的时钟管脚相连,这种情况下怎么做时序分析嘛,一般我们在片内做的时序分析都是一个寄存器到另一个寄存器的。

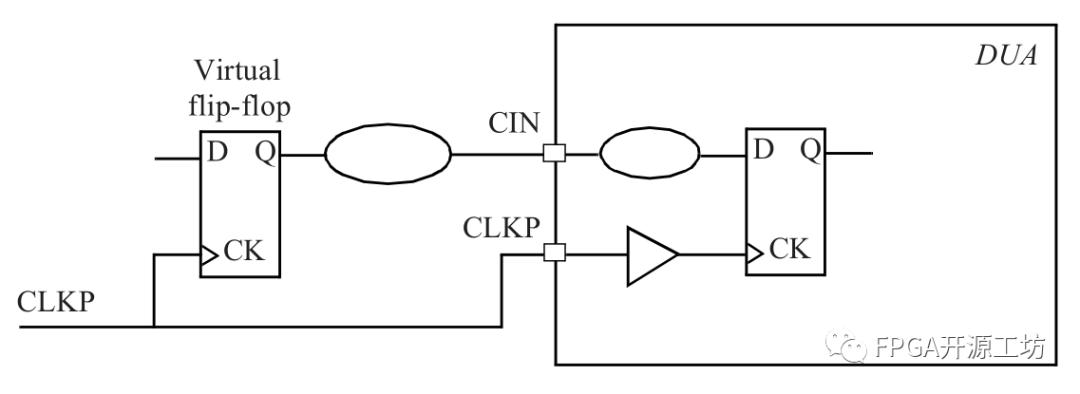

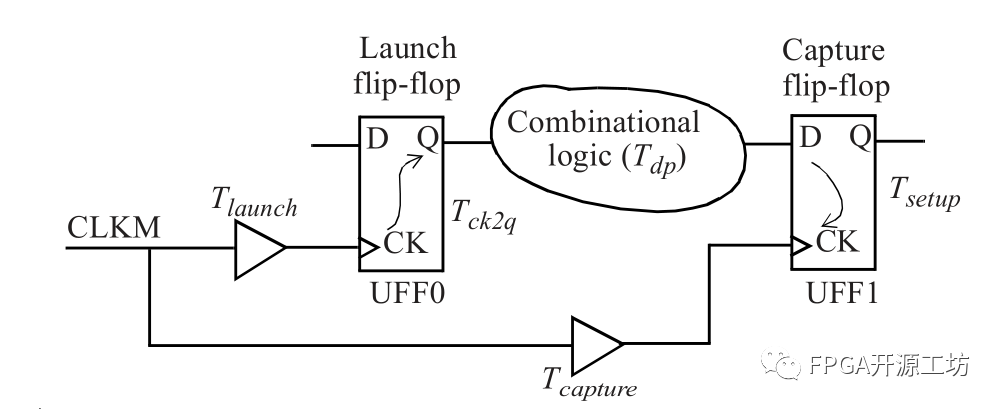

时序分析一共四种模型,可以参考下面四张图,分别是Input to Flip-flop Path,Flip-flop to Output Path,Flip-flop to Flip-flop Path,Input to Output Path图片来源于Static Timing Analysis for Nanometer Designs也就是静态时序分析圣经,这本必读哦。

实验二:

那怎么改变,vivado计算出来是inf呢,首先给输入输出加上

(*DONT_TOUCH="yes"*)

这个约束看看,代码就变成了下面这个样子

module testMem(

input clk,

(*DONT_TOUCH="yes"*)input [9:0] addr,

(*DONT_TOUCH="yes"*)input we,

(*DONT_TOUCH="yes"*)input [7:0] wdata,

(*DONT_TOUCH="yes"*)output reg [7:0] rdata

);

reg [7:0] mem [1023:0];

always@(posedge clk)begin

if(we)begin

mem[addr] <= wdata;

end

end

always@(posedge clk)begin

rdata <= mem[addr];

end

endmodule

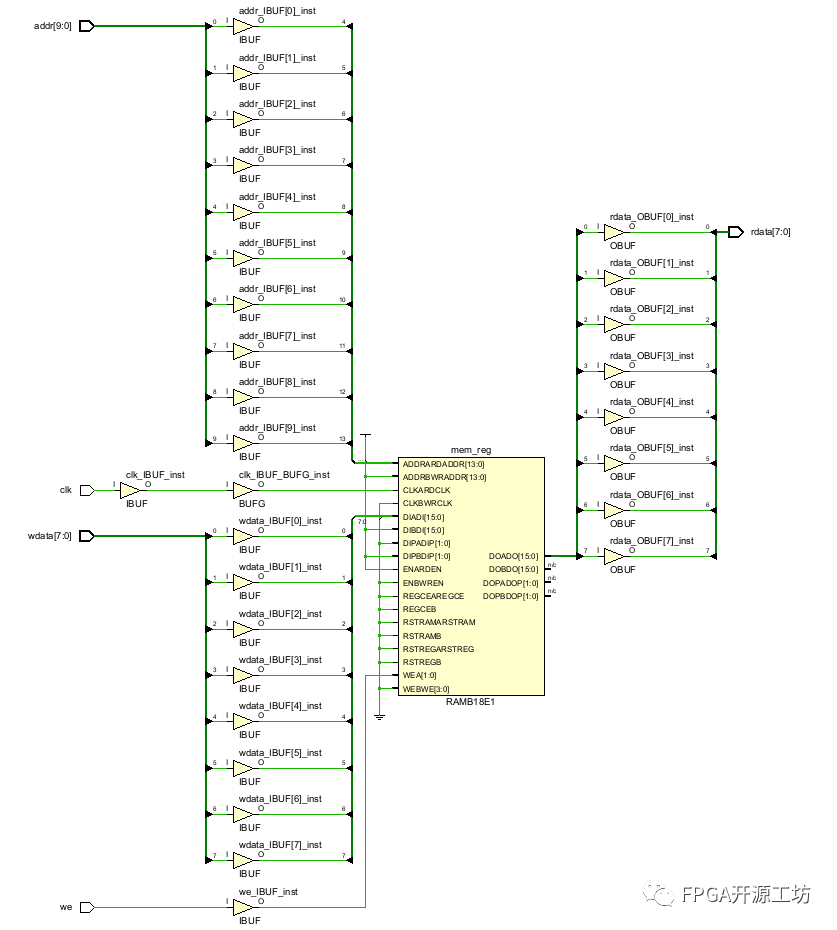

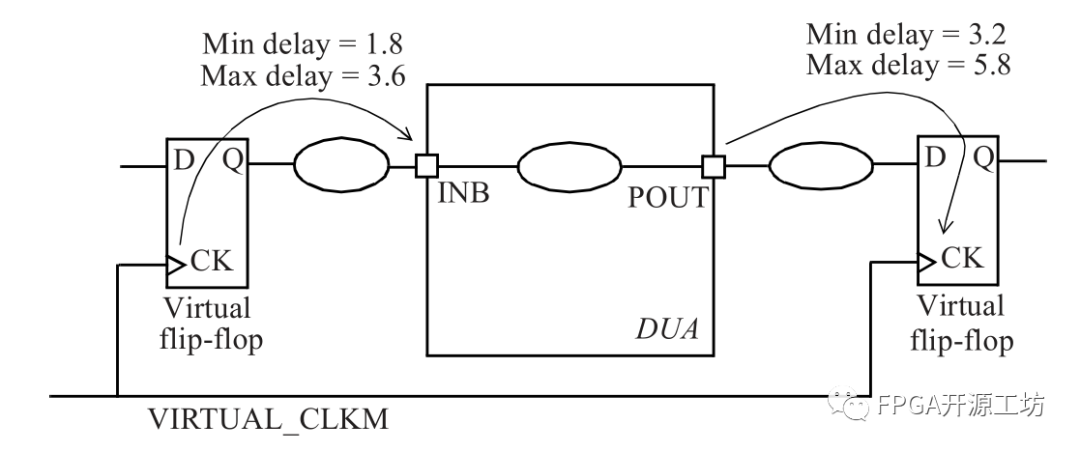

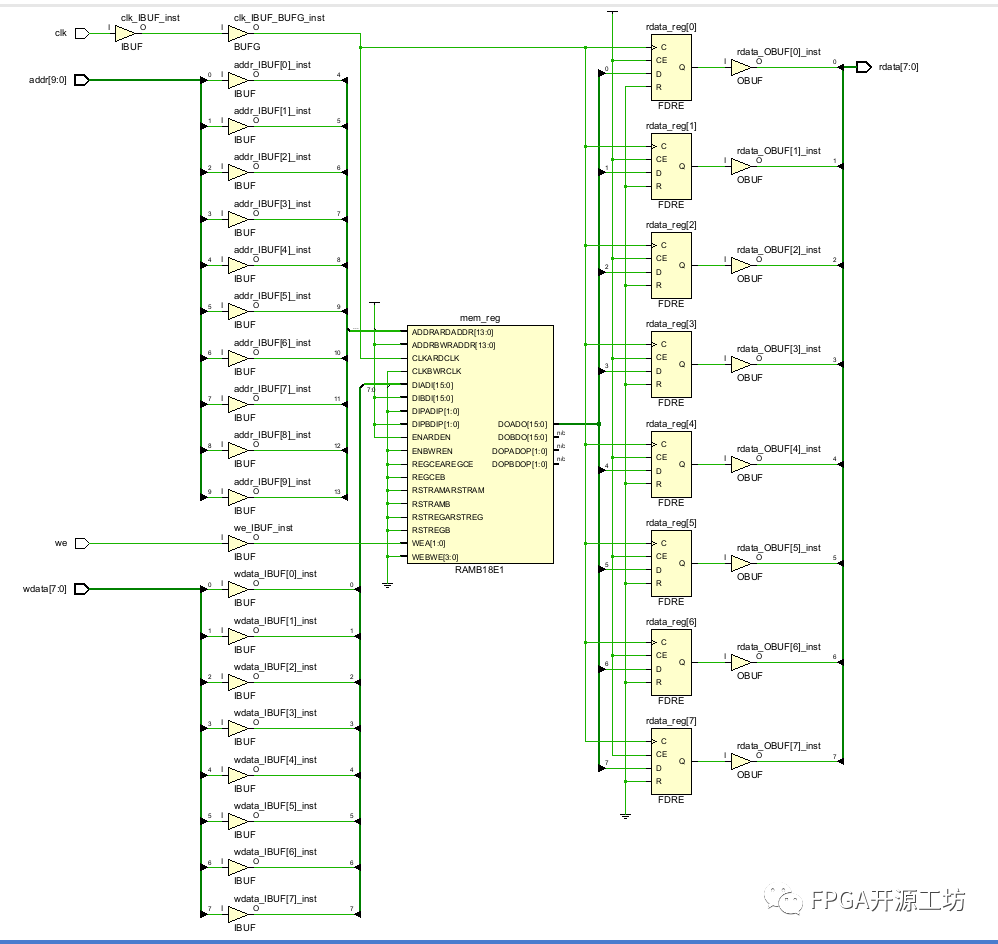

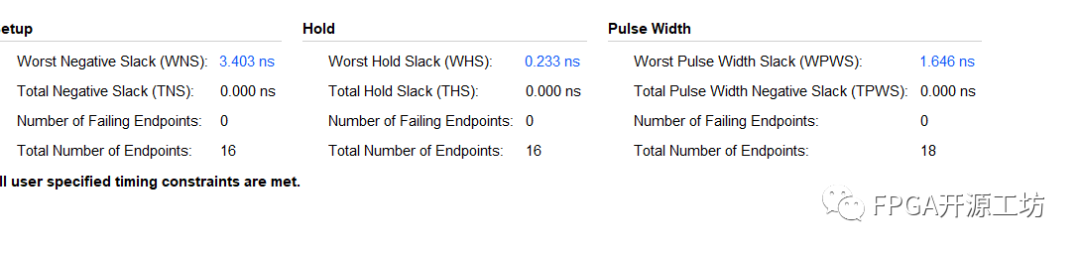

这次呢时序分析对了,我们来看一下综合后的结果,可以看到不再是孤零零的一个bram的ip了,这个就是典型的Flip-flop to Flip-flop Path的时序分析了。

但是注意到没有,实现的资源从bram变成lut和FF了,这个是因为在xilinx的器件里面,bram必须至少要有一级寄存器,那你可能又要问了,我们不是在代码里面rdata有一级寄存器吗,为啥没有被综合成bram呢,这个是因为加了dont touch的约束之后,vivado就不会再去优化这个寄存器,这样这个寄存器就不能被优化到bram里面了,这样自然就不会使用bram资源来实现上面的代码了。

实验三:

我们可以通过手动再加一级寄存器的方案,来让他使用bram资源,代码如下:

module testMem(

input clk,a

(*DONT_TOUCH="yes"*)input [9:0] addr,

(*DONT_TOUCH="yes"*)input we,

(*DONT_TOUCH="yes"*)input [7:0] wdata,

(*DONT_TOUCH="yes"*)output reg [7:0] rdata

);

reg [7:0] mem [1023:0];

reg [7:0] data;

always@(posedge clk)begin

if(we)begin

mem[addr] <= wdata;

end

end

always@(posedge clk)begin

data <= mem[addr];

end

always@(posedge clk)begin

rdata <= data ;

end

endmodule

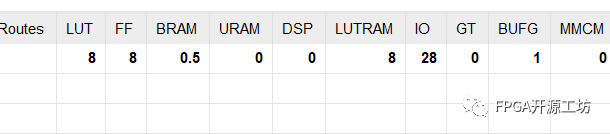

可以看到时序分析,资源分析和我们预期是一致的。

综合后的结果也和我们预期一致,可以和实验一做对比,这次在bram后面多了一级寄存器哦。

实验四:

那么我们在上面的代码里面继续去掉dont touch约束看看会发生什么。

module testMem(

input clk,a

input [9:0] addr,

input we,

input [7:0] wdata,

output reg [7:0] rdata

);

reg [7:0] mem [1023:0];

reg [7:0] data;

always@(posedge clk)begin

if(we)begin

mem[addr] <= wdata;

end

end

always@(posedge clk)begin

data <= mem[addr];

end

always@(posedge clk)begin

rdata <= data ;

end

endmodule

可以看到又变成了inf,再来看一下综合后的框图,和实验一一样,你可能会问,我们不是加了两级寄存器了吗,怎么bram的输出一个都没有呢,这是因为这两级寄存器都被bram给吸收了呢。

小提示,这样两级寄存器的方式比一级的时序会好很多哦,当然如果如果寄存器不少纯打拍的话,他是不会被吸收进去的。

实验五:

既然打两拍不行,那就多打几拍咯。

代码变成下面的样子:

module testMem(

input clk,

input [9:0] addr,

input we,

input [7:0] wdata,

output reg [7:0] rdata

);

reg [7:0] mem [1023:0];

reg [7:0] data;

reg [7:0] data1;

reg [7:0] data2;

reg [7:0] data3;

always@(posedge clk)begin

if(we)begin

mem[addr] <= wdata;

end

end

always@(posedge clk)begin

data <= mem[addr];

end

always@(posedge clk)begin

data1 <= data;

data2 <= data1;

data3 <= data2;

rdata <= data3;

end

endmodule

可以看到一切和我们的预期一致。

总之做FPGA一定要知道自己写的代码会被映射到什么资源上去哦。

审核编辑:刘清

-

关于建立时间和保持时间的测量方法2023-12-05 4053

-

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量2023-09-04 1739

-

SOC设计中的建立时间和保持时间2023-08-23 2070

-

到底什么是建立时间/保持时间?2023-06-27 19381

-

芯片设计进阶之路—从CMOS到建立时间和保持时间2023-06-21 3017

-

静态时序之建立时间和保持时间分析2022-08-22 5767

-

FPGA时序约束一如何查看具体错误的时序路径2022-08-04 1158

-

VGA驱动接口时序设计数据的建立时间和保持时间2019-04-10 2261

-

静态时序分析基础2018-12-01 4485

-

保持时间与建立时间2018-11-29 3974

-

如何利用FPGA进行时序分析设计2018-04-03 2888

-

建立时间和保持时间(setup time 和 hold time)2017-02-08 7208

-

FPGA实战演练逻辑篇57:VGA驱动接口时序设计之4建立和保持时间分析2015-08-02 5880

-

建立时间和保持时间讨论2015-03-10 4883

全部0条评论

快来发表一下你的评论吧 !