CoWoS和HBM的供应链分析

描述

CoWos是最流行的 GPU 和 AI 加速器封装技术。

人工智能正在蓬勃发展。每个人都想要更多的人工智能加速器,而主要的限制因素是将5nm ASIC 和 HBM 组合在一起的 CoWos 先进封装。这种容量不足导致 GPU 短缺,这种短缺将持续到明年第二季度。

本文主要聚焦供给侧。台积电正在向设备制造商紧急订购,以填充其位于竹南的新先进封装工厂。三星、英特尔、Amkor、JCET 和 ASE 也在扩展他们的一些竞争技术,以分得一杯羹。由于一些通用数据中心支出被生成型人工智能支出(例如内存和 CPU)所蚕食,了解仍在增长的支出对于了解供应链至关重要。在这篇文章中,我们将详细介绍 CoWos 的制造工艺流程。

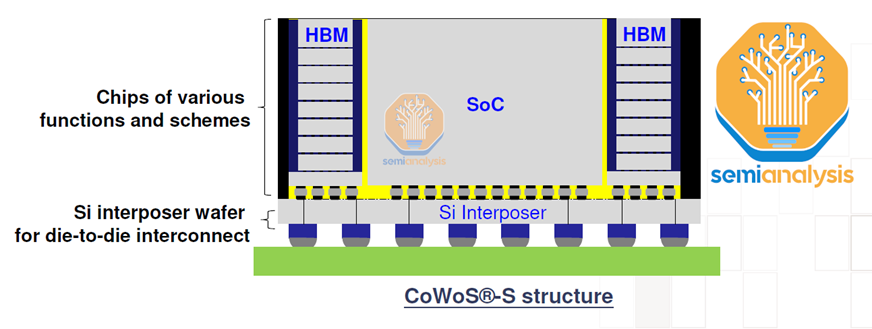

CoWoS 是台积电的一种“2.5D”封装技术,其中多个有源硅芯片(通常的配置是逻辑和 HBM 堆栈)集成在无源硅中介层上。中介层充当顶部有源芯片的通信层。然后将内插器和有源硅连接到包含要放置在系统 PCB 上的 IO 的基板上。CoWos是最流行的 GPU 和 AI 加速器封装技术,因为它是共同封装 HBM 和逻辑以获得训练和推理。

我们现在将详细介绍 CoWoS-S(主要变体)的关键制造步骤。

硅中介层关键工艺步骤

第一部分是制造硅中介层,其中包含连接芯片的“电线”。这种硅中介层的制造类似于传统的前端晶圆制造。人们经常声称硅中介层是采用 65 纳米工艺技术制造的,但这并不准确。CoWoS 中介层中没有晶体管,只有金属层,可以说它与金属层间距相似,但事实并非如此。

这就是为什么 2.5D 封装通常由领先的代工企业内部完成,因为他们可以生产硅中介层,同时还可以直接访问领先的硅。虽然 ASE 和 Amkor 等其他OSAT 已完成类似于 CoWoS 或 FOEB 等替代品的先进封装,但他们必须从 UMC 等代工厂采购硅中介层/桥接器。

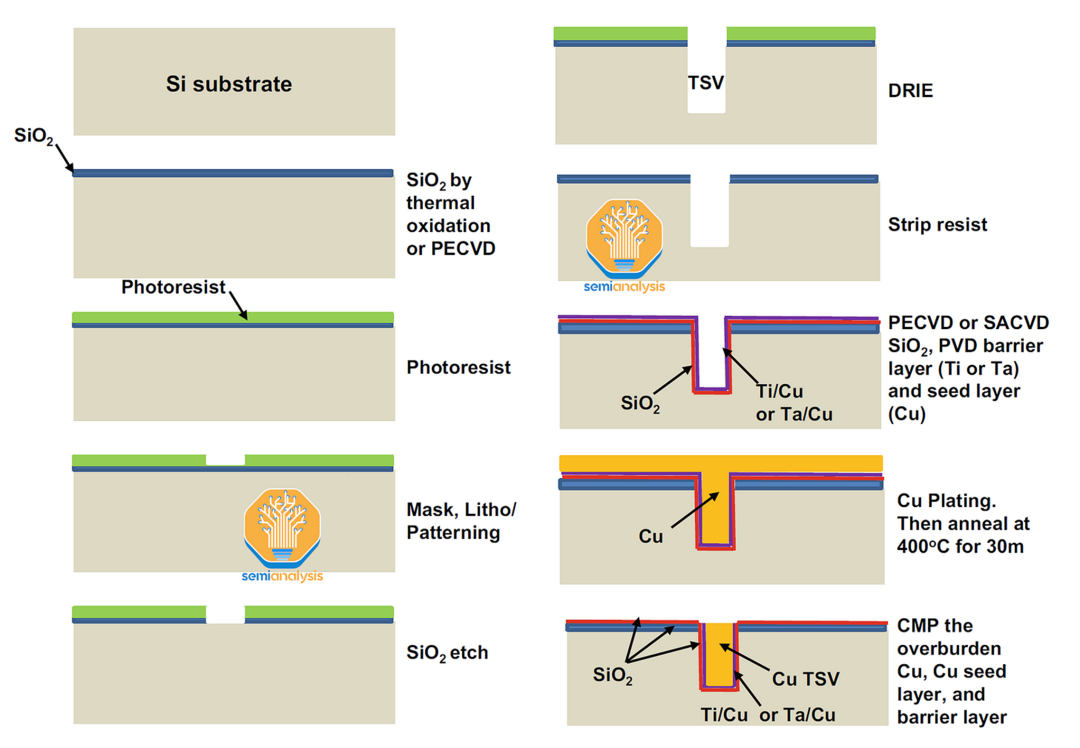

硅中介层的制造首先采用空白硅晶圆并生产硅通孔(TSV)。这些 TSV 穿过晶圆,提供垂直电气连接,从而实现中介层顶部的有源硅(逻辑和 HBM)芯片与封装底部的 PCB 基板之间的通信。这些 TSV 是芯片向外界发送 I/O 以及接收电源的方式。

为了形成 TSV,晶圆上涂有光致抗蚀剂,然后使用光刻技术进行图案化。然后使用深反应离子蚀刻 (DRIE) 将 TSV 蚀刻到硅中,以实现高深宽比蚀刻。使用化学气相沉积 (CVD) 沉积绝缘层(SiOX、SiNx)和阻挡层(Ti 或 TA)。然后使用物理气相沉积(PVD) 沉积铜种子层。然后使用电化学沉积 (ECD) 用铜填充沟槽以形成 TSV。通孔不穿过整个晶圆。

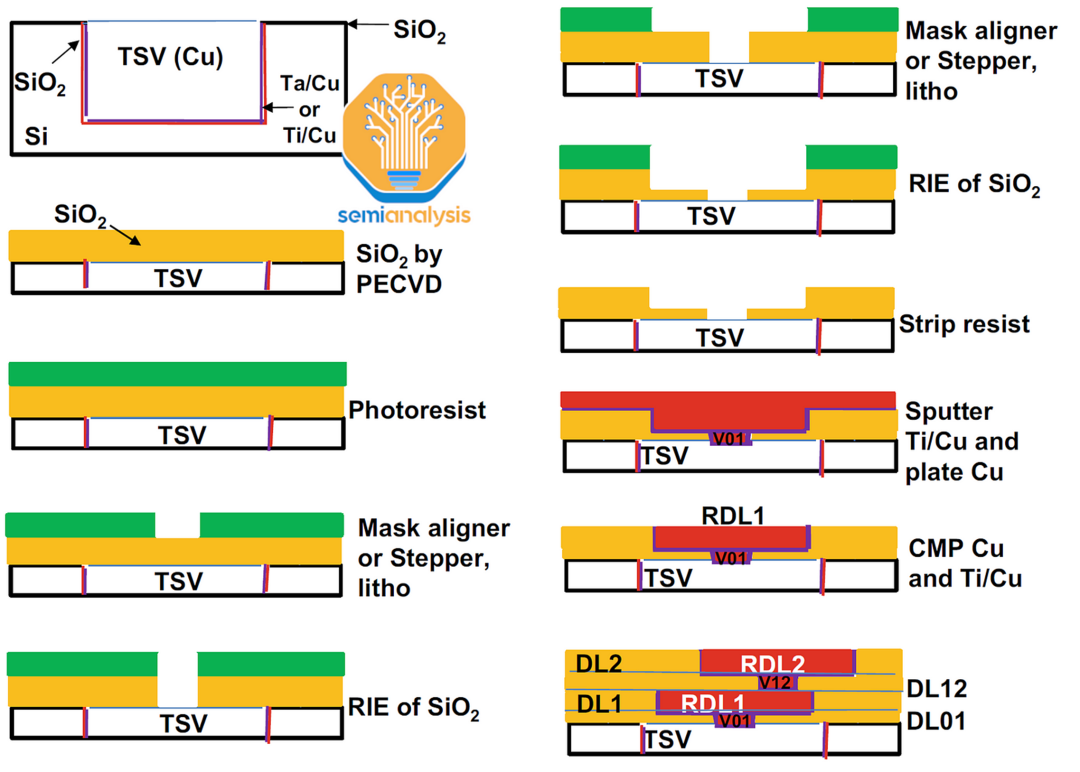

TSV 制造完成后,再分布层 (RDL) 将形成在晶圆的顶部。将 RDL 视为将各种有源芯片连接在一起的多层电线。每个 RDL 由较小的通孔和实际 RDL 组成。

通过 PECVD 沉积二氧化硅 (SiO2),然后涂覆光刻胶并使用光刻对 RDL 进行图案化,然后使用反应离子蚀刻去除 RDL 通孔的二氧化硅。此过程重复多次,以在顶部形成较大的 RDL 层。

在典型的配方中,溅射钛和铜,并使用电化学沉积(ECD) 沉积铜。然而,我们认为台积电使用极低 k 电介质(可能是 SiCOH)而不是 SiO2 来降低电容。然后使用 CMP 去除晶圆上多余的电镀金属。主要是标准的双镶嵌工艺。对于每个附加 RDL,重复这些步骤。

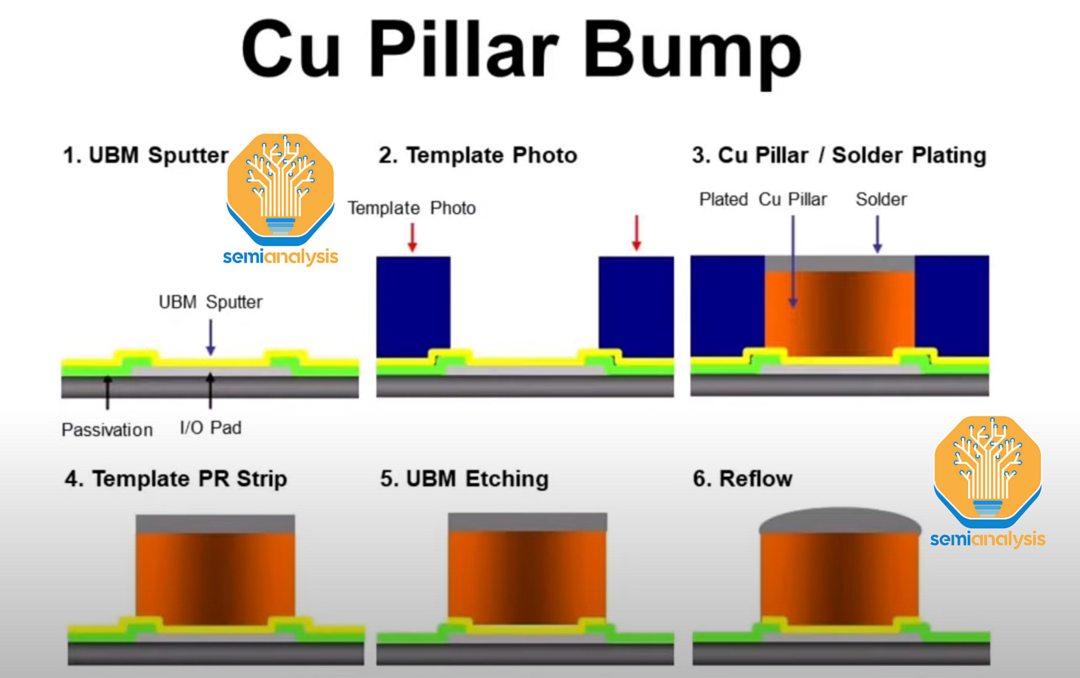

在顶部 RDL 层上,通过溅射铜形成凸块下金属化 (UBM) 焊盘。施加光致抗蚀剂,通过光刻曝光以形成铜柱图案。铜柱经过电镀,然后用焊料覆盖。光刻胶被剥离,多余的 UBM 层被蚀刻掉。UBM 和随后的铜柱是芯片连接到硅中介层的方式。

晶圆上芯片关键工艺步骤

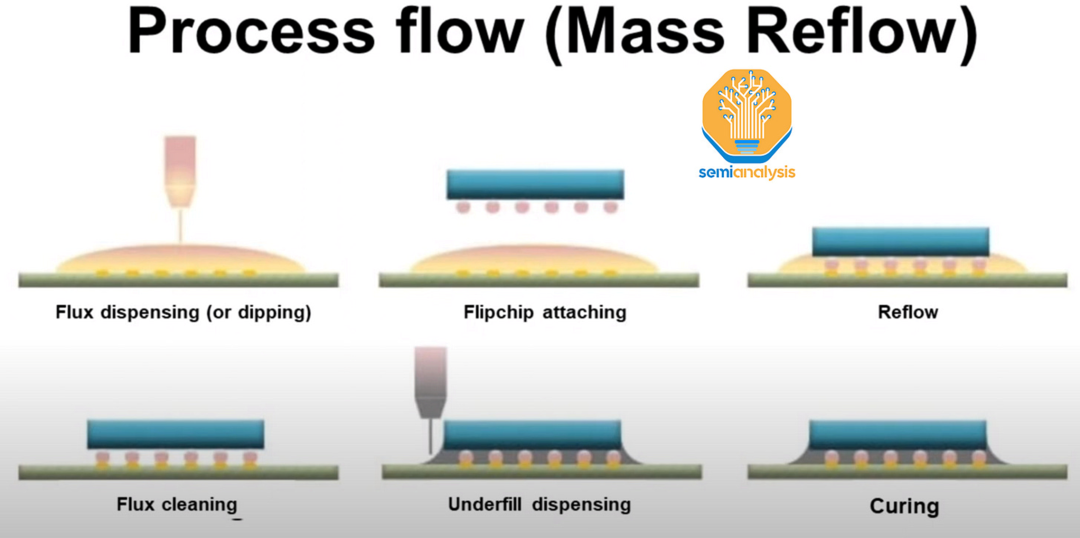

现在,使用传统的倒装芯片大规模回流工艺将已知的良好逻辑和 HBM 芯片附着到中介层晶圆上。助焊剂涂在中介层上。然后,倒装芯片接合机将芯片放置到中介层晶圆的焊盘上。然后将放置有所有芯片的晶圆放入回流焊炉中烘烤,以固化凸块焊料和焊盘之间的连接。清除多余的助焊剂残留物。

然后用树脂填充有源芯片和中介层之间的间隙,以保护微凸块免受机械应力。然后再次烘烤晶圆以固化底部填充胶。

接下来,用树脂对顶部芯片进行模制以将其封装,并使用 CMP 使表面光滑并去除多余的树脂。现在,通过研磨和抛光将模制中介层翻转并减薄至约100um 厚度,以露出中介层背面的 TSV。

尽管已变薄,但附接到中介层晶圆顶部的顶部管芯和封装可以为晶圆提供足够的结构支撑和稳定性,因此并不总是需要载体晶圆来支撑。

基板上晶圆关键工艺步骤

中介层的背面经过电镀和 C4 焊料凸点凸点处理,然后切成每个单独的封装。然后,再次使用倒装芯片将每个中介层芯片附着到增层封装基板上以完成封装。

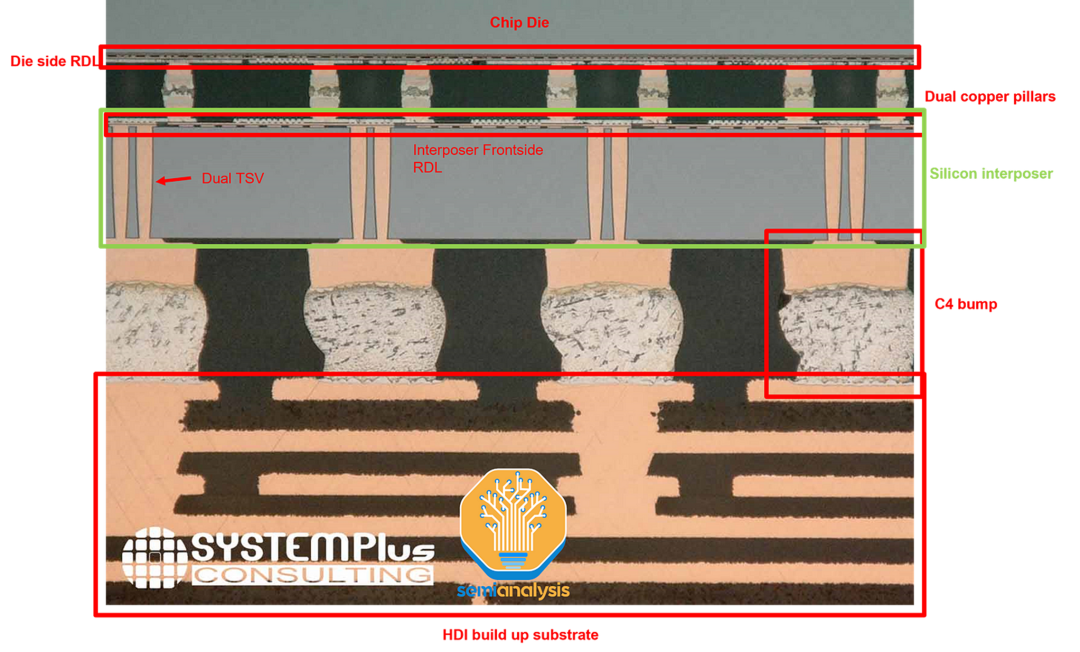

在下面英伟达 A100 的 SEM 横截面中,我们可以看到 CoWoS 封装的所有各个元素。

顶部是带有 RDL 的芯片芯片和铜柱微凸块,这些铜柱微凸块粘合到硅中介层正面的微凸块上。然后是顶部有 RDL 的硅中介层。我们可以看到 TSV 穿过中介层,下面每个 C4 凸块有 2 个 TSV。底部是封装基板。

请注意,A100 的中介层正面仅有单面 RDL。A100的架构更简单,只有内存和GPU,因此路由要求更简单。MI300由内存、CPU 和 GPU 组成,全部位于AID 之上,因此这需要更复杂的 CoWoS,从而影响成本和产量。

审核编辑:刘清

-

基于实物期权的供应链能力柔性决策研究2009-06-14 3313

-

华为的研发流程和供应链管理2012-02-02 14381

-

基于电子商务的供应链金融研究2012-10-25 2768

-

手机供应链管理2014-11-24 5117

-

区块链将改革供应链2018-08-08 3816

-

如何使用RFID建立绿色供应链系统2019-05-29 2225

-

RFID技术对供应链管理有什么影响2019-07-29 2275

-

地缘政治、产业链外迁,供应链安全对策2023-03-14 1172

-

柔性电子供应链企业的机会与挑战2023-09-15 2084

-

一个基于Fuzzy AHP的供应链风险分析模型2009-08-14 1031

-

特斯拉40%的电池供应链依赖中国2023-08-09 1927

-

Hanmi半导体与三星电子讨论HBM供应链,扩大客户群和市场份额2024-01-03 2399

-

7.行业研究及十五五规划分析报告(行业发展环境分析和行业供应链分析)2024-06-24 1069

-

HBM技术在CowoS封装中的应用2025-09-22 2691

-

紫光国芯存储芯片国产替代方案:打破DDR5/HBM芯片供应链瓶颈2025-10-10 2768

全部0条评论

快来发表一下你的评论吧 !