不同器件之间的GPIO连接为什么需要电平一致呢?

接口/总线/驱动

描述

一、问题:不同器件之间的GPIO连接为什么需要电平一致呢?

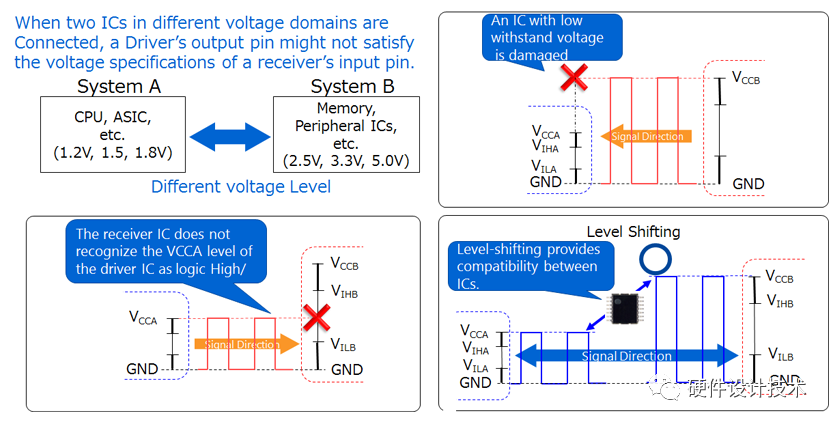

如果连接不同电平信号的I/O,驱动IC的输出电压电平可能不满足接收器的输入电压规格,从而导致接收器故障或损坏。

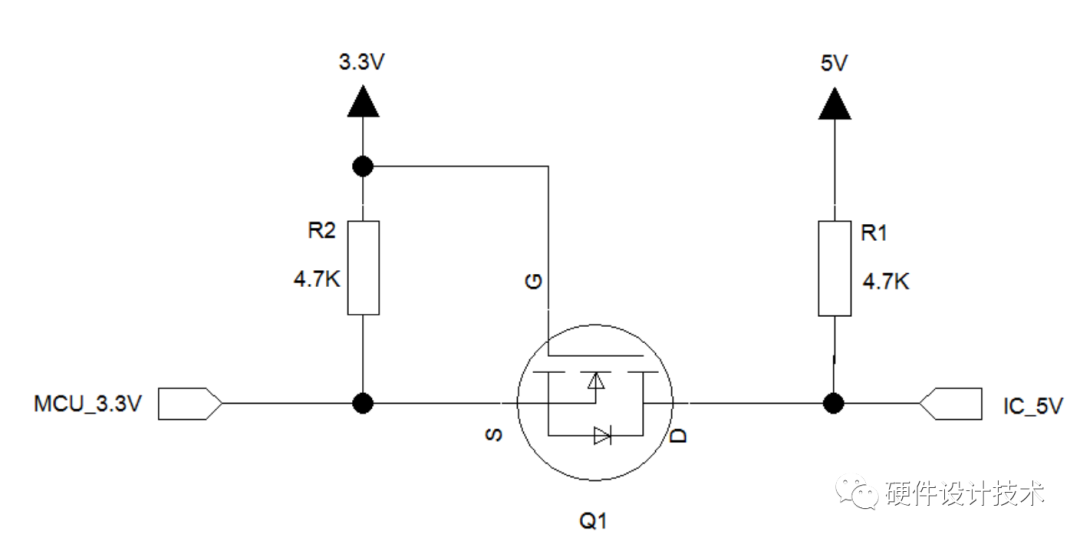

图一、电平转换

1.2、 如果各个器件之间的电压不匹配,可能会出现何种异常现象:

将某个信号从高电压电平输入至低电压电平的器件,如<图一>右上图所示。低压侧的器件输入电路的耐压通常较低,如果输入高于芯片耐压值的电压,该器件可能会遭损毁。

将某个信号从低电压电平输入至高电压电平的器件,如<图一>左下图所示。如果在高压侧的器件上施加接近输入阈值的电压,则无法识别高电平信号,从而导致故障。

二、问题:既然GPIO允许被配置为开漏输出。那么是否可以直接使用开漏功能实现不同电平之间转换呢?比如:3V-1.8V

2.1、实现开漏输入、输出功能的引脚大至分为两大类:

输入、输出引脚内部电路是真正的MOS开漏、三极管开集电极输出形式:比如电平转换的专用缓存器、使用MOS管搭建的开漏输入、输出电路。此类功能的芯片、电路使用较简单。

普通的GPIO引脚通过配置控制寄存器,实现开漏极输出功能。注意:此类GPIO使用较为复杂,不能简单的认为利用“开漏电路实现线与”实现电平转换。

2.2、通过GPIO控制寄存器配置的开漏输出为什么不能直接“线与”?

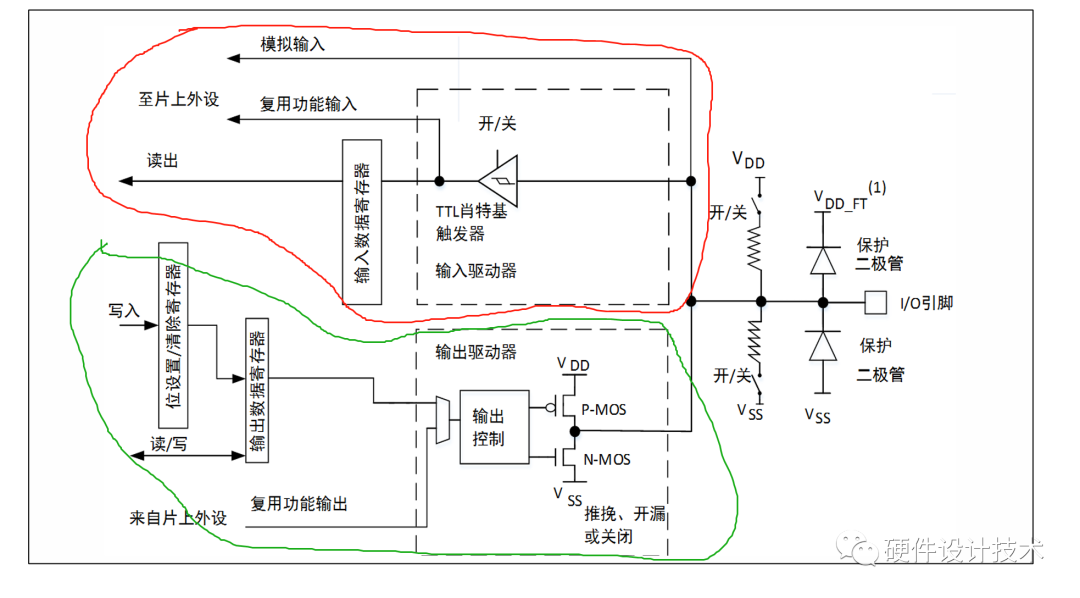

从前文GPIO简介可以知道:GPIO口内部由输入、输出2部分组成;当GPIO口的OUTPUT被使能,不管OUTPUT是否使能开漏输出或推挽输出,GPIO的输入INPUT<输入施密特触发器>始终开启。

如图下图所示,当外部输入1.8V时,由于IO_VCC 3.3V,1.8V处于中间电平,导致IO输入部分漏电。具体原因如下:

当GPI0口电平与供电电压VCC相等时,处于input状态的内部电路等效为一个PMOS连接到VCC和一个NMOS连接到地;当输入电压为VCC时,只导通下管NMOS,不导通上管PMOS,故功耗可以忽略不计。同理,当输入电平为低电平时,只导通上管PMOS,不导通下管NMOS,功耗也可以忽略不计。

但当GPIO输入电压为1.8V时,IO_VCC电压为3.3V,上管和下管同时微导通

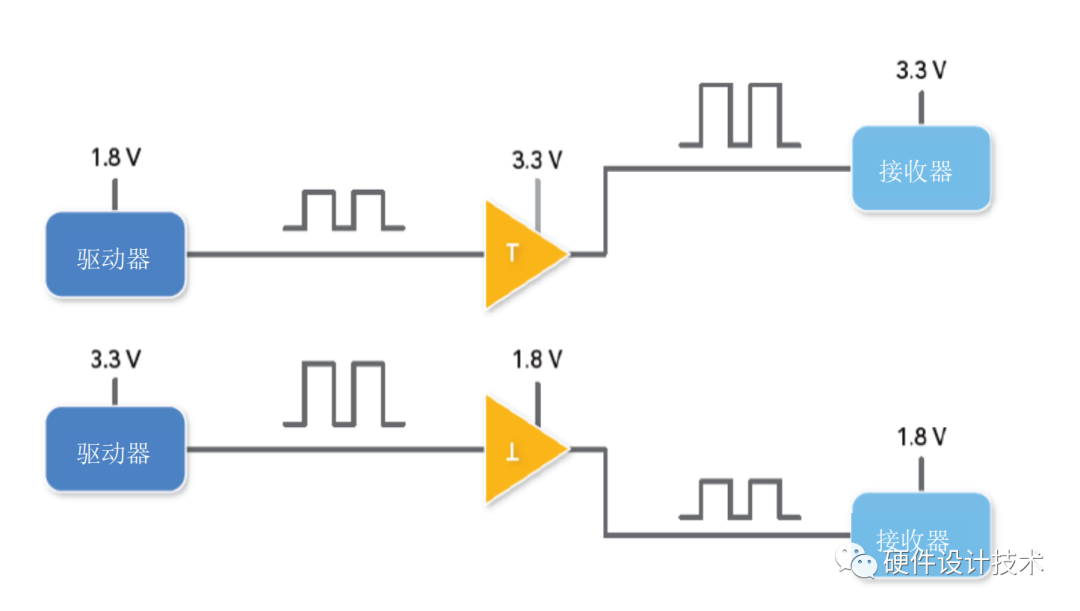

三、常用的电平转换方法、电路:

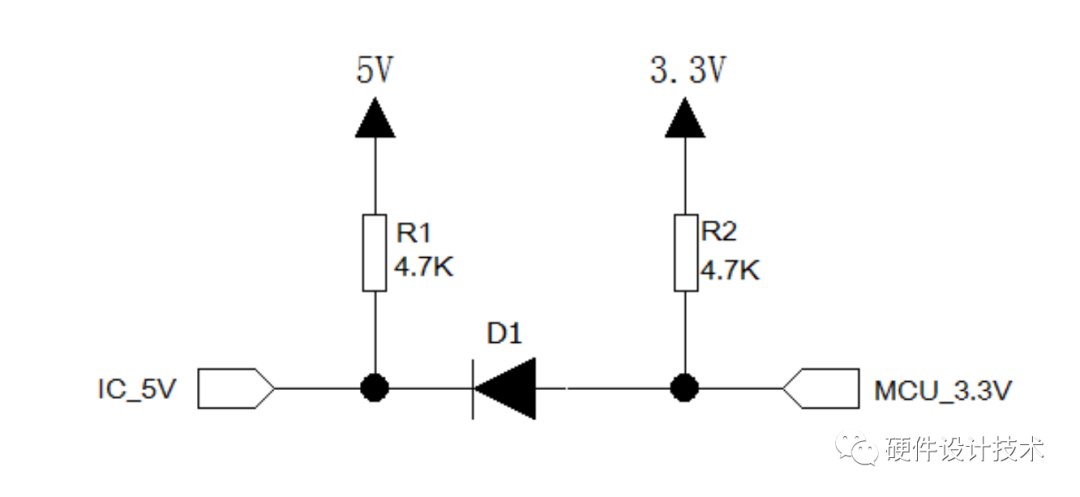

3.1、 二极管转换电平(单向转换)

左侧为 5V 电压域,右侧为 3.3V 电压域:

当左侧电压输出高电平(5V)时,二极管 D1 截止。右侧被上拉到一个 3.3V 的高电平;

当左侧电压输出低电平(0V)时,二极管 D1 导通,右侧被拉到为二极管导通电压的低电平;

(注:该电路在低电平转换时存在转换误差,该误差主要来源于二极管正向导通压降,二极管在选型时,5V 端输出的 VOL + 二极管正向压降 VF不能超过 VIL的最大值,MCU 在 3.3V 供电时,VIL电压最大值为 0.8V,MCU 在 1.8V 供电时,VIL电压最大值为 0.3*1.8V=0.54V)。

3.2、MOS 管转换电平(双向转换)

左侧为 3.3V 电压域,右侧为 5V 电压域:

当左侧电压输出低电平(0V)时,MOS 管导通,右侧电压通过 MOS 管被拉低;

当左侧电压输出高电平(3.3V)时,MOS 管不导通。右侧电压被电阻 R1 上拉到 5V;

当右侧电压输出低电平(0V)时,MOS 管不导通,MOS 管先经过体二极管把左侧电压拉到低电平,此时,Vgs 大于 MOS 管阈值电压从而使 MOS 管导通,进一步左侧电压通过 MOS 管被拉低;

当右侧电压输出高电平(5V)时,MOS 管不导通。左侧电压被电阻 R2 上拉到 3.3V。

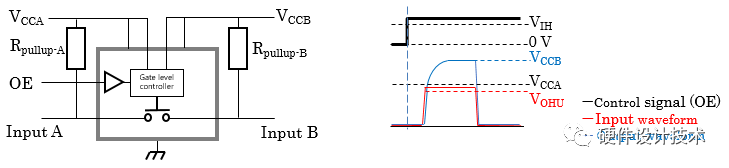

3.3、使用专用电平转换总线开关或总线缓冲器

当向输出使能信号(OE)的输入端施加等于或高于VIH的电压时,总线开关将输入信号(高或低)传输至输出端:

0V≤输入电压

输入电压≥VOHU:内部开关关断。VCCB侧的外部上拉电阻将输入电压上拉至VCCB电平。

审核编辑:刘清

-

请问如何保证多片AD1278的通道之间相位一致性?2025-01-14 536

-

水晶头线序需要和面板一致吗?2024-03-18 12542

-

STM32单片机如何设置以兼容CMOS与TTL电平呢?2024-02-02 6443

-

DDR一致性测试的操作步骤2024-02-01 4300

-

锁相环的输入输出相位一致吗?2024-01-31 2739

-

USB设备之间是怎么同步时钟的?所有USB设备的时钟频率都是一致的吗?2024-01-16 4543

-

电子元器件质量一致性检验技术介绍2022-07-19 3295

-

GPIO的内部上下拉电阻_GPIO的驱动能力2020-10-14 14361

-

TMS320DM642AZDK6 Vport口工作在GPIO模式下输出的电平一直处于低电平状态2020-04-14 1875

-

为什么ALIENTEK开发板PA7的IO口电平一直是初始化状态?2019-09-16 1313

-

6678多核之间的L1 CACHE一致性是由硬件实现的吗2018-12-25 3180

-

加速器一致性接口2017-11-17 4555

-

OCP互连一致方案应用2011-09-09 13951

-

一致性规划研究2009-04-06 680

全部0条评论

快来发表一下你的评论吧 !