H桥电路设计实例、拓扑结构、PCB设计

应用电子电路

描述

关于H桥,前面几篇篇文章基本上讲的差不多了,大家如果想看,可以点击下面文章去详细了解。电路一点通汇总了主要是关于H桥设计。

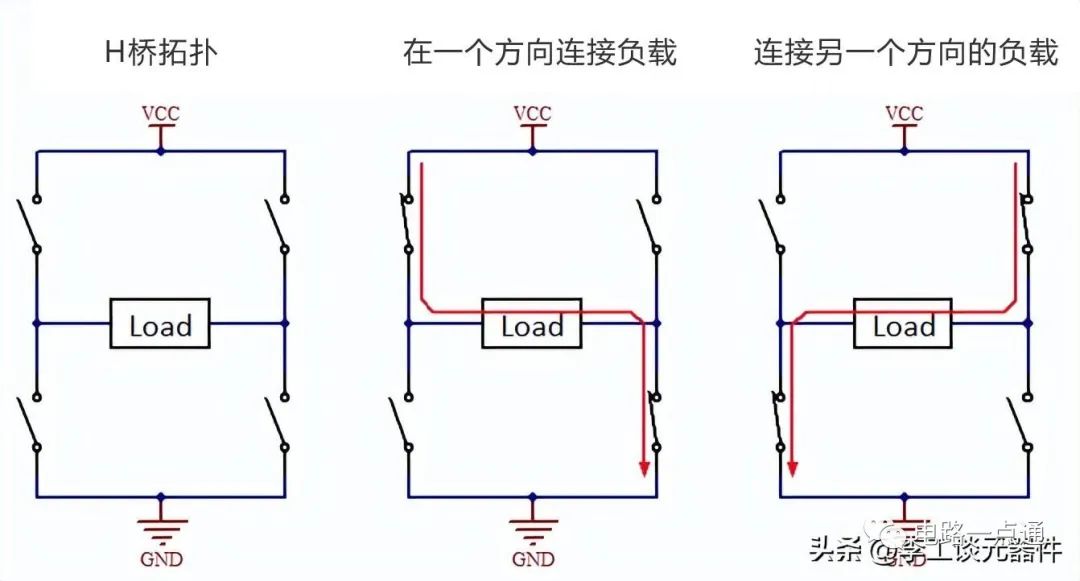

一、H桥基本拓扑结构

下图显示了H的基本拓扑结构:

H桥基本拓扑结构

在一般的设计中,开关通常是某种晶体管(双极型、MOSFET、 IGBT)。开关对角闭合(左上角和右下角或者右下角和左下角)在任一方向将电源连接到负载。

二、H桥需要克服的问题

H桥存在有2个问题:避免击穿和驱动高端晶体管。

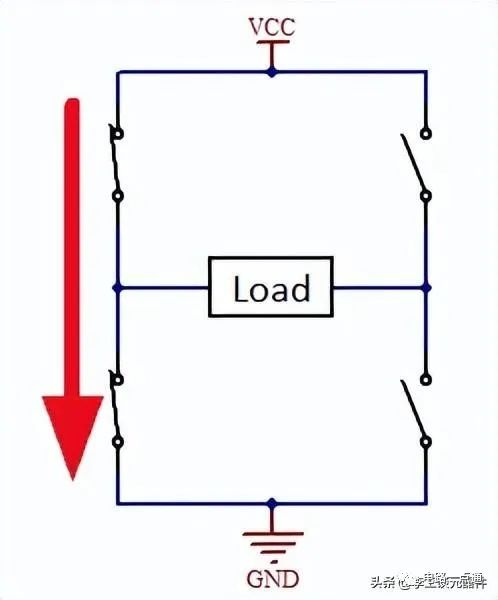

击穿是指左侧两个开关或右侧两个开关同时闭合的情况,这肯定会导致短路,这是一个坏事,可能会损坏开关或者其他组件。

下图显示了这里说的情况。

有2种可能发生这种情况的方式,一个是应用了非法控制信号,例如由于软件错误。

另一个是从一种极性切换到另一种极性时,栅极驱动信号中存在短暂且无意的重叠。

左侧的两个开关意外同时导通,导致大的短路电流流过

驱动高侧晶体管是相对比较难的部分,因为高侧晶体管以相对较高的电源电压为参考而不是以地为参考,控制信号(通常来自微控制器或类似设备)以地为参考,因此需要某种电平转换电路。

三、设计H桥电路

主要是为了驱动5相双极步进电机,Iw = 0.21 A,Rw = 32 ohms,因此H桥需要能够支持6.7V的驱动电压。

1、设计选择

大约200mA的电流不是特别高,使用双极晶体管(BJT)作为开关。对于更高的电流,必须使用具有较低电流增益的强大功率晶体管,就需要大量的基极电流,这样实际上不好处理,并会导致大量损耗和需要消散的热量。

这里打算在电流和电压处理要求上留出一些余量来构建电桥,使用MOS管来避免BJT的静态基极电流引起的功率耗散问题。

对于给定的导通电阻,就元器件尺寸(成本)和栅极电容而言,NMOS管晶体管的效率大约是PMOS晶体管的3倍,因此对于高功率设计,上下开关都使用NMOS晶体管是有利的。

但是将NMOS管用于上部开关有一个问题:NMOS管需要高于桥电源电压的栅极电压。如果使用PMOS管,低于电源电压的栅极电压是足够的。为了避免额外的电源电压,并且由于电流相当低,因此合适的PMOS管的成本不高。

最后我决定使用PMOS管作为顶部开关,NMOS管作为底部开关。

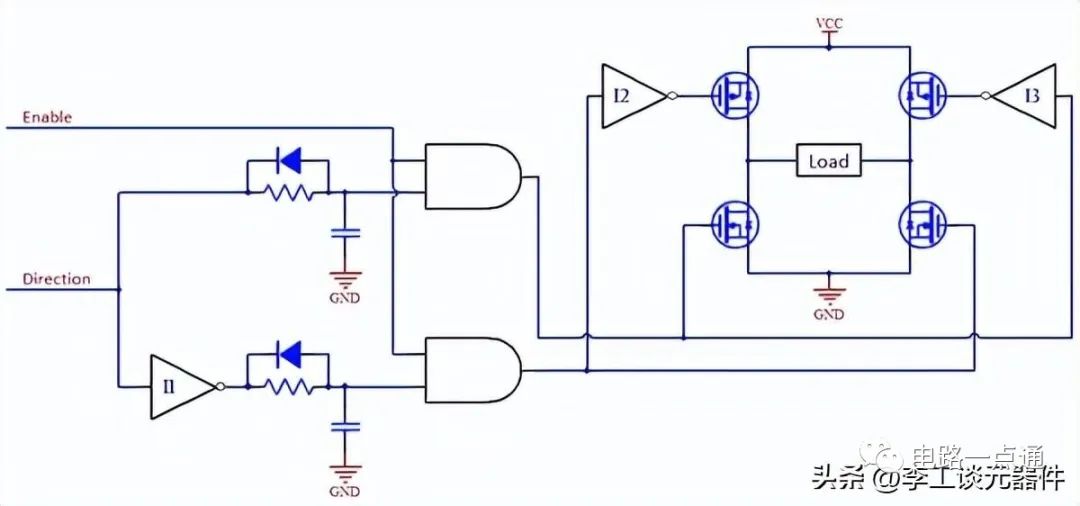

2、H桥驱动电路信号生成

这里为了避免设计安全,即使微控制器代码中的错误就永远不会导致严重情况发生。因此需要注意以下2件事情:

1、使用一些逻辑门用于控制信号(启动/方向)转换为打开左上/右上或者右上/左下的内部信号,

2、为了避免在方向信号变化期间发生短暂的直通,最好在晶体管的导通信号中引入延迟,而且让关断信号尽快通过,因此引入一个短暂的时期,在极性切换期间没有晶体管导通。

下图显示了一种概念性解决方案,实现了启用/方向控制信号和栅极信号之间的切换,并在晶体管即将导通时引入了延迟。

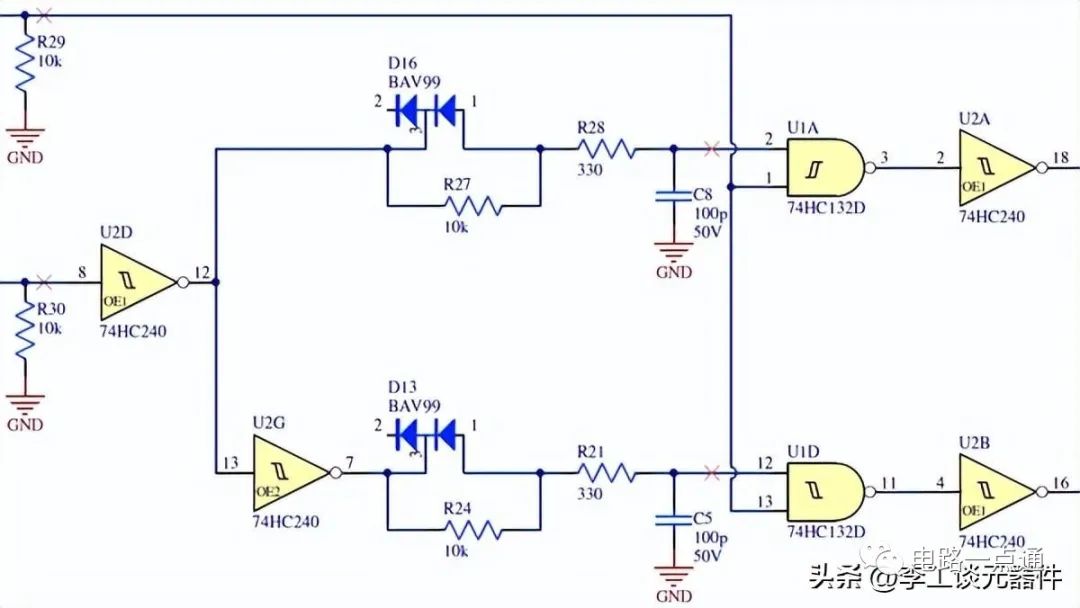

H桥的栅极驱动信号如何生成的电路图

H桥的栅极驱动信号生成原理

两个ADN 门允许使能信号断开控制信号与MOS管栅极的连接,二极管/电阻组合使电容的充电速度比放电速度慢,因此当晶体管即将导通时,栅极驱动信号到达晶体管所需的时间比晶体管即将截止的时间更长。

通过让来自与门的栅极控制信号对角地控制晶体管,来自与门之一的电平变化打开或者由门控制的两个晶体管。仅使用2个延迟电路就可以控制4个晶体管的时序。

反相器I2和I3需要将与门的逻辑电平转换为适合驱动晶体管的电压。

四、详细设计

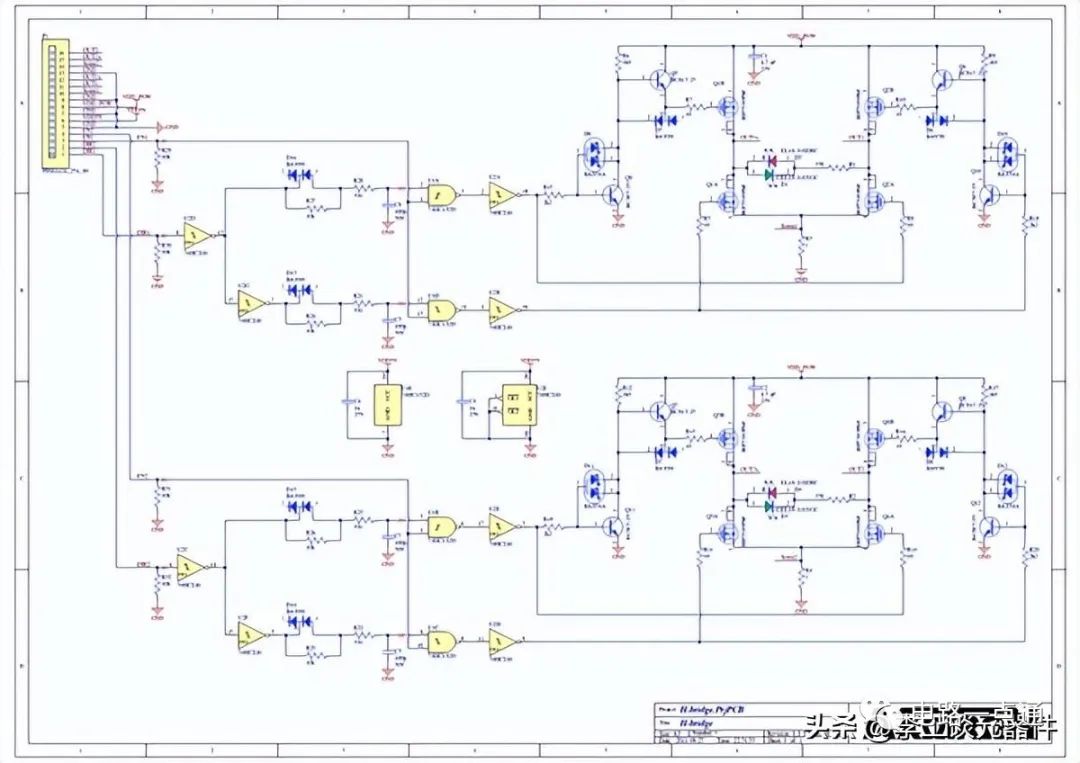

1、设计原理图

完整的(双)H桥的示意图

2、逻辑门的选择

下图的与门需要有施密特触发器输入,因此与门是由相对缓慢变化的电压驱动的。使用或非门会使使能信号处于低电平状态,但这并不是缺点。使用或非门的一个优点是反相器 I1 可以通过或非门实现。然后单个逻辑IC就可以满足H桥的要求。

这里需要使用2个用于H桥的逻辑IC来提供所需的NAND门和4个反相器。'240 系列逻辑电路中有八进制反相器可用,连同'32 四路与非门,有足够的门用于两个桥。所以最后还是在同一块板上构造了2座H桥。下图显示了最终的设计。

逻辑门和不对称时序电路的示意图

可以使用几个不同的逻辑系列,因为我想要具有CMOS输入电平的NAND门,这也意味着施密特触发器输入将以电源电压的一半进行切换,同时我还希望反相器具有CMOS输出用来驱动NFET高达5V。

因此NAND门可以是 HC或者AC系列,而反相器可以是HC、HCT、或者AC等。

最后 2个地方都是使用的HC,将HCT用于反相器用来适应方向信号上的TTL电平并不好,因为启用信号无论如何都必须有CMOS电平。

3、其他输入级选择

这里我在输入信号上放置了下拉电路,将它们保持在有效且安全的逻辑电平,防止某些输入有时没有连接。CMOS输入具有非常高的阻抗,不然很容易拾取噪声。

为了限制电容充电时的电流浪涌,在二极管/电阻对桑串联了一个额外的330Ω电阻,另一个电容和电阻的值先手工计算大致计算确定,然后进行模拟,在电路完成后进行微调,保证没有击穿。

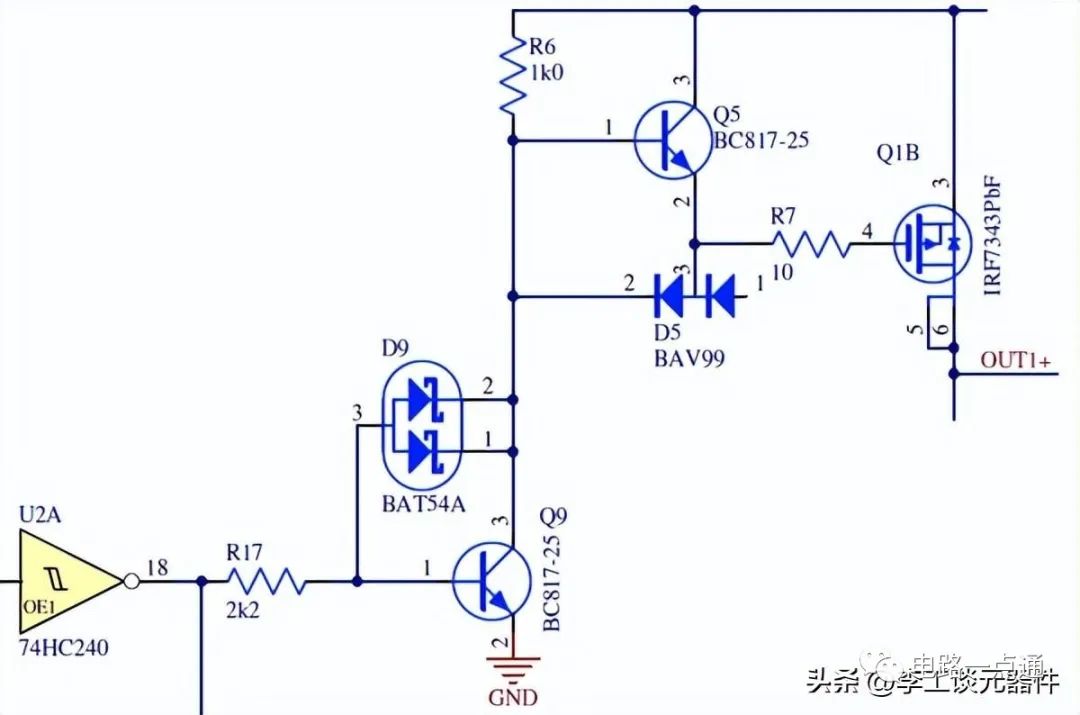

4、高侧驱动器

高侧PMOS晶体管的驱动电路需要反转信号并增加电机电源电压的摆幅,该电压至少为7V,必须能够相对地对FET的栅极电容进行充电和放电。当较低的NMOS管快速拉动漏极电压时,即使寄生栅极电容将其拉低,PFET也会保持关闭状态向下。

高侧驱动器

上图显示了完整的驱动电路。反转和电平移位由NPN晶体管Q9处理。该晶体管的关闭速度非常慢。因为如果没有从基极到集电极的肖特基二极管防止饱和,就会处于饱和状态。这和LSTTL逻辑内部用于加速切换的技术相同。

Q5作射极跟随器连接。并在PMOS晶体管关闭时向电源轨提供所需的低组狼。仅依靠R6将栅极拉高会显著拉高晶体管关闭的时间,但是这里更重要的是。当快速发生变化时,电阻无法将栅极保持在高电平。

由于较低的 NMOS 导通,PMOS 晶体管的漏极处出现压降(大的负 dV/dt)。当 PMOS 导通时,二极管 D5 提供将栅极拉低的路径。这里使用 PNP 射极跟随器来稍微加快开启速度。

小栅极电阻 R7 可限制栅极电流浪涌并降低栅极电路中出现振铃的风险。

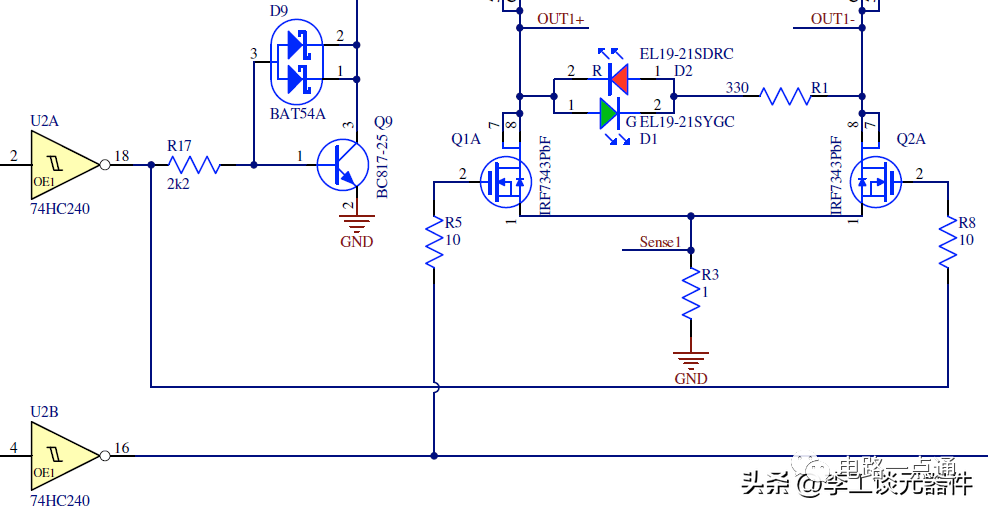

5、电路其余部分

这里显示了电桥电路的其他部分

其他电路

驱动NMOS管要简单一点,将普通的栅极电阻(R8)连接在反相器的输出和栅极之间就可以。

这里在NMOS管的源极引线中添加了一个电流检测电阻。方便测量电流并且验证是否发生击穿。选择1Ω作为获得示波器测量的合适电压和最小化损耗之间的折中方案。

在0.2 A 电流下,我们得到 0.2 V 压降,与 6 或 7 V 电源电压相比,这相对较小。测试完成后,可以用 0 Ω电阻替换 1 欧姆电阻。

对于 MOSFET,选择了 IRF7343,是采用单个 SO8 封装的 NMOS/PMOS 组合,是价格、可用性和导通电阻的综合选择。

这里还在H桥输出上添加了LED,可以直观地指示电路的状态。但是对于成品来说,最好不要使用LED。

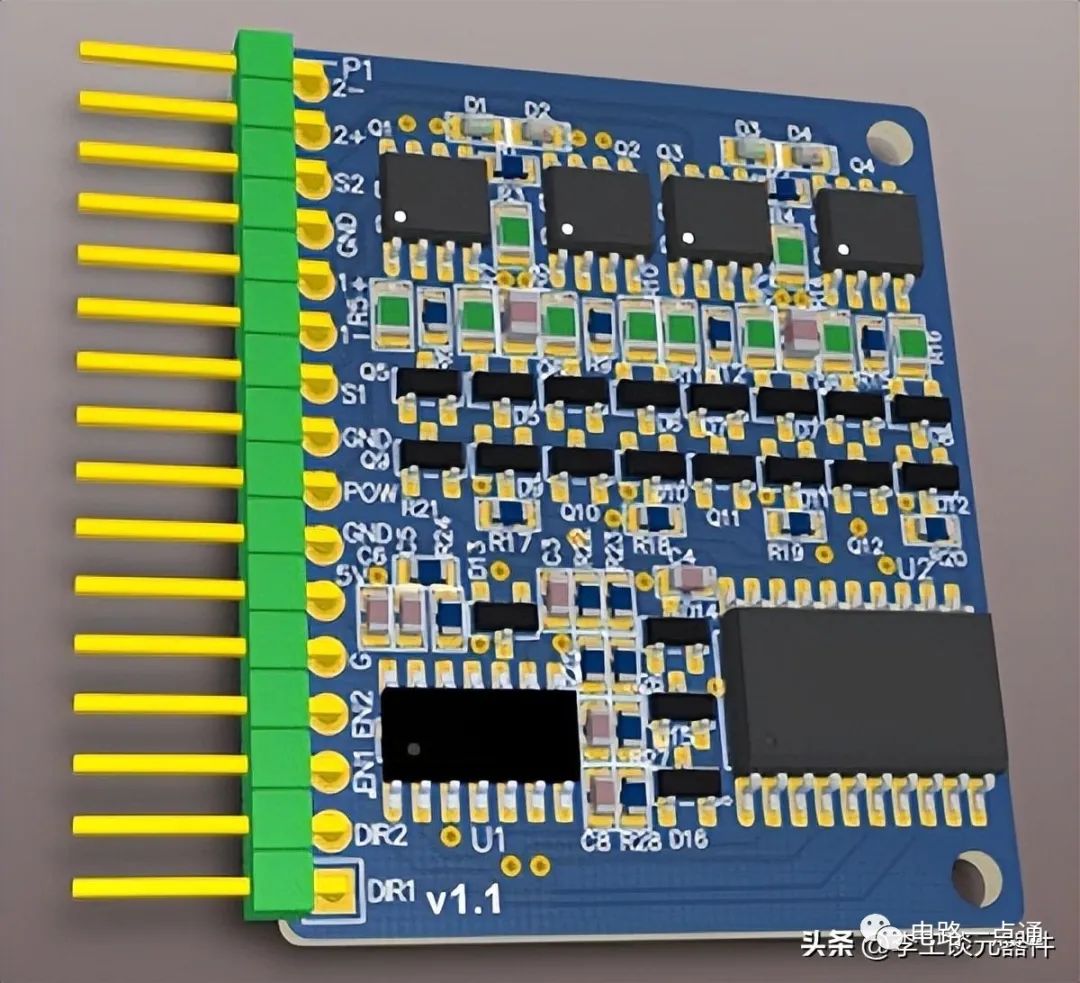

五、H桥电路PCB设计成品图

最后决定将双H桥电路放在双面PCB上,将所有外部信号拉到单排排针,而不是设计一个包含H桥、微控制器、电源等完整的PCB,这样可以最大程度低减少工作量,从而完成项目的H桥部分。如果有必要的化,可以始终将H桥与电路板上的其他电路集成在一起。

下面为最终的成品图。

H桥电路PCB设计成品图

以上就是关于H桥电路设计的内容,希望大家能够点赞、分享、收藏

审核编辑:汤梓红

-

全桥电路基础的拓扑结构2010-06-24 3767

-

高速PCB设计指南的高密度(HD)电路设计2010-03-21 1350

-

H桥逆变器PCB设计板开源2022-08-11 2106

-

电路设计和PCB设计中如何防止ESD损坏设备2023-05-24 1914

-

H桥电路原理图 H桥电路的工作原理和实例2023-07-17 17892

-

接电路设计,PCB设计,PCB Layout2015-05-16 3876

-

基于拓扑结构的升压Boost2021-11-11 2419

-

理解拓扑结构2021-11-17 1421

-

电路设计技巧PCB设计流程2009-11-06 2275

-

步进电机H桥型驱动电路设计及其应用2016-08-09 1253

-

pcb设计实例讲解2019-04-25 21598

-

PCB设计实例说明2021-05-17 1160

-

直流脉宽H桥控制电路设计2021-09-15 1131

-

DDR PCB设计布线时,拓扑结构的选择2022-11-27 2758

-

PCB设计步骤和规范 PCB常见类型电路设计2023-09-26 1468

全部0条评论

快来发表一下你的评论吧 !