芯耀辉:本土Chiplet标准更符合国内芯片厂商现阶段诉求

描述

随着近年来半导体先进工艺向3nm、2nm不断演进,一直以来行业发展仰仗的摩尔定律开始放缓甚至停滞,通过提升晶体管密度来提高芯片性能开始遇到瓶颈。早些年Marvell提出的模块化芯片架构概念,变身Chiplet,重新被行业重视起来。

Chiplet实际上是一种硅片级别的IP复用,将不同功能的IP模块集成,再通过先进封装技术将彼此互连,最终成为集成为一体的芯片组。这种像拼接乐高积木一样,用封装技术将不同工艺的功能模块整合在一颗芯片上的方式,在提升性能的同时还能降低成本和提高良率。

尽管在2018年,AMD已将CPU、GPU等部件分成更小的组件组合成SoC,并成功将Chiplet技术应用于商业化产品中,但在当时,整个行业尚未建立起关于Chiplet芯片设计、互联和接口的统一标准,例如涵盖裸片间的完整接口堆栈,以及传统封装过渡到2.5D封装的标准。因此,Chiplet技术在大范围应用发展上受到了一定限制。

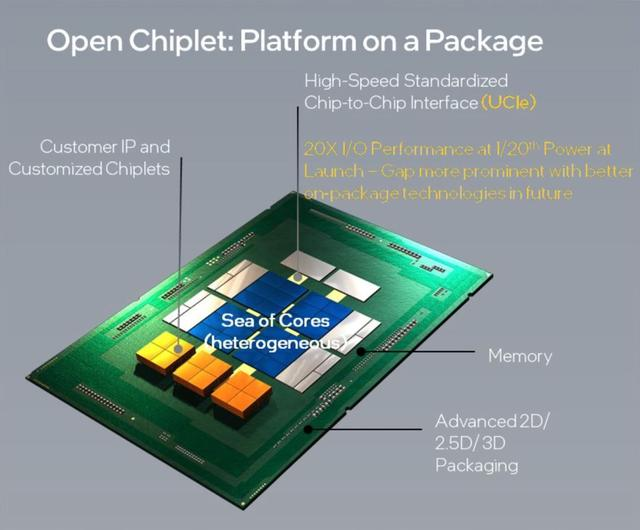

直到2022年,UCIe(Universal Chiplet Interconnect Express)产业联盟的成立,提供开放的Chiplet互连协议UCIe 1.0,才在芯片封装层面和接口堆栈层面确立了互联互通的统一标准。

图自:UCIe

虽然UCIe成立后不久,芯耀辉、芯原等就成为首批加入的中国企业,但也有人担心UCIe标准中明确支持的CXL和PCIe互联协议,均由英特尔提出和创建,一旦在标准上被“卡脖子”,是否会影响到中国Chiplet技术的发展?

Chiplet在中国落地还面临哪些挑战?

其实国内也一直在尝试建立自己的Chiplet生态。2021年5月,国内Chiplet组织——中国计算机互连技术联盟(CCITA)在工信部立项了《小芯片接口总线技术要求》,由中科院计算所、工信部电子四院和国内多家厂商合作展开标准制定工作。

“芯耀辉不仅有基于最新UCIe标准的IP产品,2022年下半年,还作为重点贡献企业加入CCITA承接国家科技部的重点专项,参与了中国小芯片(Chiplet)原生技术标准的制定。其中接口IP部分,我们是唯一一家作为实施落地推动的厂商。” 在第三届中国集成电路设计创新大会暨IC应用博览会高峰论坛(ICDIA 2023)上,芯耀辉科技有限公司董事长曾克强在接受《电子工程专辑》等媒体采访时说到。

2022年12月,中国首个由中国企业和专家主导制订的Chiplet技术——《小芯片接口总线技术要求》团体标准(T/CESA 1248-2023)正式向世界发布,并在今年2月,由中国电子工业标准化技术协会审订后正式实施。谈到这项中国原生的Chiplet标准,曾克强认为要实现落地面临几个挑战:

一、 纯技术的挑战。把一颗芯片拆分成多个小芯片,通过接口在物理上和功能上将这些小芯片完全串联配合起来,需要大量高规格的接口IP,确保各个芯片之间的连接接口,确保高速数据传输和低延迟、解决热管理和功耗分配问题。

二、 整个产业链协同的挑战。Chiplet标准的落地,需要从EDA供应商、IP厂商到生产制造和先进封装,整个生产链的配合,如果整个产业链发展不是齐头并进,任何一处的短板都可能导致到无法整体落地实施。

三、需要制定适合中国产业链的统一互联标准。尽管UCIe的标准被提出,但完全套用UCIe的标准并不能使Chiplet在国内得到快速、有效落地。当前,国内亟需Chiplet技术来突破先进工艺的限制,因此需要制定更符合国内厂商诉求的本土标准。然而,要让Chiplet技术在国内实际应用,仍然需要克服众多挑战并走很长的发展道路。

UCIe和中国的Chiplet标准有什么不同?

简单来说,国内目前更需要的技术是“使用相对不那么先进的工艺,把芯片性能跑到极致。”曾克强说到,曾经业界对于集成电路的创新实际上相当简单粗暴,就是工艺迭代推动着往前走,每一代芯片的极限性能能够做到多少,主要是靠工艺。“但工艺本身的发展趋缓,国内面临着获取先进工艺的困境,就更需要Chiplet技术来挖掘成熟工艺的潜能。”

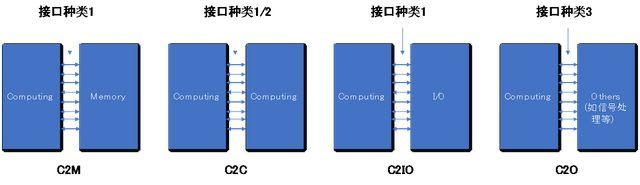

UCIe在标准组成上,主要由D2D(Device to Device)协议层(Protocol Layer)、适配层、物理层(含封装)组成,我国的《小芯片接口总线技术要求》(CCITA)也有类似的组成,由链路适配层、物理层、协议层及封装组成。两个标准的关键区别在于以下两点,UCIe只定义了并口,CCITA的Chiplet标准既定义了并口,也定义了串口,两者的协议层自定义数据包格式也不同,但其标准与UCIe兼容,可直接使用已有生态环境。在封装层面,UCIe支持英特尔先进封装、AMD封装,CCITA定义的Chiplet标准不仅可以满足国际先进封装要求,最主要地,它采用国内可实现的封装技术,从而更好地适应本土市场的需求。

中国计算机互连技术联盟(CCITA)秘书长郝沁汾曾对媒体表示,我国的标准更加符合国情。UCIe在D2D组成的芯片中,加入了一种叫retimer的功能芯片定义,它负责把信号由并行转成串行,然后以更高速度传送到较远的地方,以满足较长距离的连接需求。国内《小芯片接口总线技术要求》则不包括这部分内容,而是一个纯粹的D2D互连标准,在物理层,国内Chiplet标准同时支持并口和串口,串口的差分信号是一对线,可以把信号传的比并口的单端信号更远。如此能使国内某些加速器芯片厂商实现将相同的芯片直接通过串口差分信号接口互连,以拓展总体性能的目的。而UCIe只支持通过单端信号实现D2D短距离互连,或需搭配retimer达成较长距离互连,与国内厂商的现阶段诉求不一致。

图自:中国计算机互连技术联盟

曾克强表示,国内Chiplet标准既支持像台积电CoWoS等先进封装方式,也支持国内能做到的封装方法,以确保多样化的选择。

关于Chiplet D2D更详细的技术细节,芯耀辉的核心三位技术骨干也专门撰写了一篇详细文章,并发布在《电子工程专辑》。感兴趣的朋友可以点击阅读全文查看:《后摩尔时代的Chiplet D2D解决方案》

同样是接口IP,芯耀辉有什么不同?

据曾克强介绍,芯耀辉目前员工人数已接近400人,在接口IP方面是国内不折不扣的龙头企业,相关IP产品和服务也已获得众多客户量产使用。虽然目前国内接口IP市场竞争比较激烈,但他认为,芯耀辉和其他公司还是有很大不同的,主要体现在以下几点:

第一,大量头部客户的认可。先进工艺接口IP之前基本由新思科技和Cadence这样的国外大厂垄断,国内能做到40、28nm及以下工艺的接口IP较少。芯耀辉成立后仅用三年时间,2022年就推出大量自研先进工艺IP产品推向市场,据悉国内很多头部芯片厂商都已采用,部分已经实现流片,并且测试结果良好。

第二,IP领域的主要竞争力是产品系列(Portfolio)全面性。全套产品指的不仅仅是功能的实现,由于接口IP采用国际标准,所有公司对产品的功能定义都类似,但在性能参数上并是不每家公司都能做到比肩国际大厂。具体来说,在DDR3/4、USB2.0、PCIe3等相对较老的标准上,国内有不少IP公司能做,差异化不大;“但在最新的DDR5、PCIe5、32G SerDes、UCIe标准上,国内市场基本只有我们一家实现了国产先进工艺平台最全的IP覆盖,DDR5/4 PHY IP在相关工艺上更是超越了全行业最高速率。”他说到。

第三,兼容性和可靠性。同一款IP用在不同的芯片产品上能否帮助客户一次量产成功,曾克强认为是最重要的。“商业化的IP公司不能只做某个芯片应用的专用型IP,而要同时支持各种不同的芯片应用,并且在各种极限使用情况下都具备很好的兼容性和可靠性,帮助客户芯片成功量产,才是高质量的标准IP产品,这就考验研发人员的经验了。”这类经验往往不是IP研发人员在办公室自己“闭门造车”出来的,还需要通过大量Corner case、应用Case、客户和市场反馈等,不断打磨迭代后累积而成。

“这正是芯耀辉的强项,我们的核心团队曾经在新思科技、紫光展锐、海思、高通等大厂工作过,具备十几二十年的应用经验。”曾克强说到,“目前国内专注做接口IP的厂商大概有两三家,芯耀辉可以说是这些厂商中产品Portfolio最全的一家,与其他家的身位已经大幅拉开。”

在帮助客户做好兼容性方面,曾克强以当前最热、也最复杂的车规级芯片为例,“目前芯耀辉已经成功研发了符合车规工艺平台的全套车规级IP。今年6月,国际公认的检验、测试和认证机构SGS正式向芯耀辉颁发了ISO 26262:2018半导体功能安全ASIL D流程认证证书。这标志着芯耀辉已经按照ISO 26262:2018版标准要求,建立起完全符合功能安全最高“ASIL D”级别的产品开发和管理流程体系,达到国际先进水平。在可靠性方面,芯耀辉的车规级接口IP产品还通过了AEC-Q100车规级可靠性的严格认证,这进一步证明了其在高性能、高可靠、高安全的车规级IP产品及解决方案方面的卓越实力。”值得透露的是,许多国内车规芯片厂商目前也纷纷选择采用芯耀辉的接口IP,这充分证明了他们在行业中的实力与认可。

-

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”2023-02-21 1479

-

芯原股份:正积极推进对Chiplet的布局2021-01-08 3605

-

安华加盟芯耀辉,全面提速先进芯片IP技术的研发2021-01-20 3298

-

芯耀辉:国产接口IP迎接Chiplet发展,未来着眼于超越摩尔2021-10-20 6279

-

芯耀辉如何看待Chiplet国内发展情况2023-04-12 1104

-

芯耀辉曾克强:国产高性能接口IP全方位赋能,迎接Chiplet与AI大市场2023-08-03 3324

全部0条评论

快来发表一下你的评论吧 !