绝缘耐压测试的一个争议问题

描述

今天一位工程师问了我一个问题,“一个模块有几个输入管脚,V+、V-、signal、Gnd,还有金属外壳,甲方测试验收的时候,分别打V+对外壳、V-对外壳,Signal对外壳,Gnd对外壳,打的电压还挺高,至少几百伏,有的电路板就给打坏了,问这种打法有问题没有?是不是还是说明了我们设计的模块有问题?“

类似的问题,在这一两年间,在一些大型科研单位里也发生过两三次。甚至后来都找到了某些GB电气安全标准的制定人,但也是争论半天,因为很多标准只是国外标准翻译过来的,也没说清真正的依据。知其然,知其所以然,才是治学之道。

那到底应该怎么做呢?为什么这样做呢?

首先说结论,应该把所有管脚接在一起,然后统一对外壳打耐压,才是正确的方式。

原因是电路中的某些地方确实是有可能存在绝缘强度的隐患的,最常见的部位之二是DIP封装的器件Pin脚,在电路板固定后,与金属板之间的间距小;二是电路板固定安装孔附近的螺丝与电路板的走线或覆铜层的间距小;当然还有很多其他的地方。

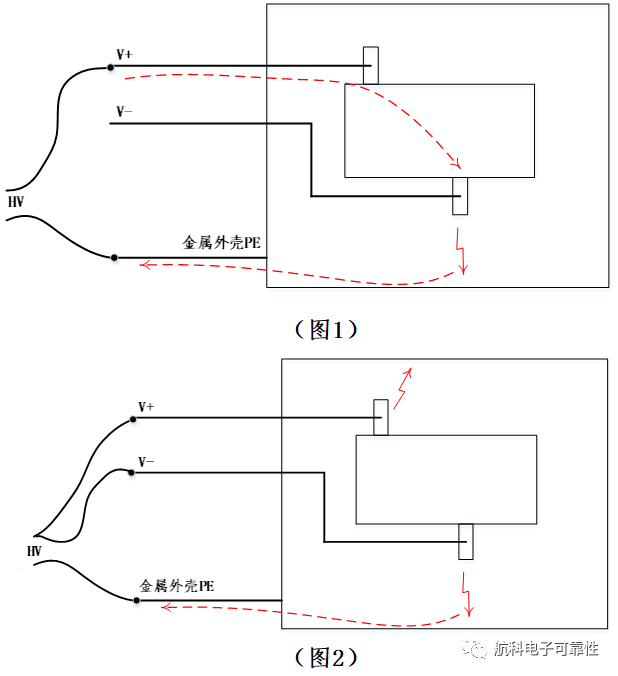

万一模块中有这种绝缘阻抗不足的情况时,各脚单独对外壳打高压,就容易形成如(图1)的情况,图中V+对外壳打耐压,但电路中的某个pin脚对外壳距离很近,则有可能形成如图红线的泄放通路,泄放电流如此之大,器件焉能不坏?如果实际工况中不会有任何距离外壳近的情况发生,即使V+加上了高压,没有泄放通路,整块单板也会处于一个高压等电位,板上没有压差形不成电流,板子也不会坏。

总结成一句话:

如果没隐患,两种打法都没问题;

如果有隐患,则单pin分别对外壳打,则有损伤内部电路的风险。

如果采用了所有输入引脚接在一起后,统一对外壳打的方式,就算是某些pin脚存在了对外壳的绝缘强度不够的问题,因为所有输入管脚的等电位,在电路中的器件自身里内部不易形成放电通路,可以有效地保护器件。

总结成一句:

所有输入管脚接在一起,对外壳打耐压,可以遇到有隐患的电路板则可以更好的保护,避免损坏。

当然,可能有杠头会说一个观点,如果电路中的某个中间电路的引脚对外壳很近,那V+V-虽然等电位,但会不会两边包抄通过这个引脚对外壳放电呢?答案是仍有可能的。不过这种情况发生的概率确实会相对比较低得多。

北京汉通达科技主要业务为给国内用户提供通用的、先进国外测试测量设备和整体解决方案,产品包括多种总线形式(台式/GPIB、VXI、PXI/PXIe、PCI/PCIe、LXI等)的测试硬件、相关软件、海量互联接口等。经过二十年的发展,公司产品辐射全世界二十多个品牌,种类超过1000种。值得一提的是,我公司自主研发的BMS测试产品、芯片测试产品代表了行业一线水平。

-

请问AMC1200绝缘耐压是如何测试的?2024-09-04 471

-

请教 IGBT 模块的绝缘耐压如何测试?2023-10-23 10016

-

智能化多路绝缘耐压自动测试系统的研究2009-03-13 520

-

绝缘和耐压的区别_耐压测试与绝缘测试两者有何区别2018-04-03 112278

-

绝缘耐压测试仪的原理_绝缘耐压测试仪的特点2020-04-22 7385

-

3153绝缘/耐压测试仪的功能特点及应用范围2021-01-17 5063

-

耐压绝缘测试仪如何避免误判2022-11-01 2539

-

ITECH绝缘耐压测试2023-08-28 482

-

电源模块耐压测试的方法是什么?ATECLOUD-POWER测试系统助力绝缘耐压测试2023-10-18 2357

-

NTCRP的绝缘电阻和耐压如何测试?2023-10-25 2624

-

为什么交流耐压测试仪有一大一小两个绝缘柱2023-12-20 1384

-

什么是耐压测试仪?耐压测试仪能测绝缘电阻吗2024-05-07 5983

-

绝缘电阻测试和耐压测试区别2024-05-08 7077

-

绝缘电阻测试和绝缘耐压测试有什么不同2025-02-13 3666

-

电源测试系统:矿用电源为什么需要它的测试绝缘电阻,绝缘耐压和充放电?2025-09-17 959

全部0条评论

快来发表一下你的评论吧 !