以EMC中ESD测试讲述电容的选择应用

EMC/EMI设计

描述

EMC设计过程中,常用的思路包括“堵”和“疏”,电感,磁珠通常用于“堵”,而电容器通常用于“疏”,个人觉得“疏“比”堵”更加可靠,“疏”可以将信号的回路引入低阻抗路径,避免对其他信号进行干扰,而“堵”往往会引起高电压,而高电压又会引起电压驱动型的共模干扰。大量实践表明:在EMC设计中,恰当选择与使用电容,不仅可以解决许多EMC问题,还能充分体现效果良好,价格低廉,使用方便的优点,但若电容的选择或者使用不当,则可能根本达不到预期目的,甚至会恶化产品的EMC水平,电容的选择不当,一个主要的原因在于没有注意到电容的工作电压,工作频率,工作温度。下面以EMC中ESD测试讲述电容的选择应用。

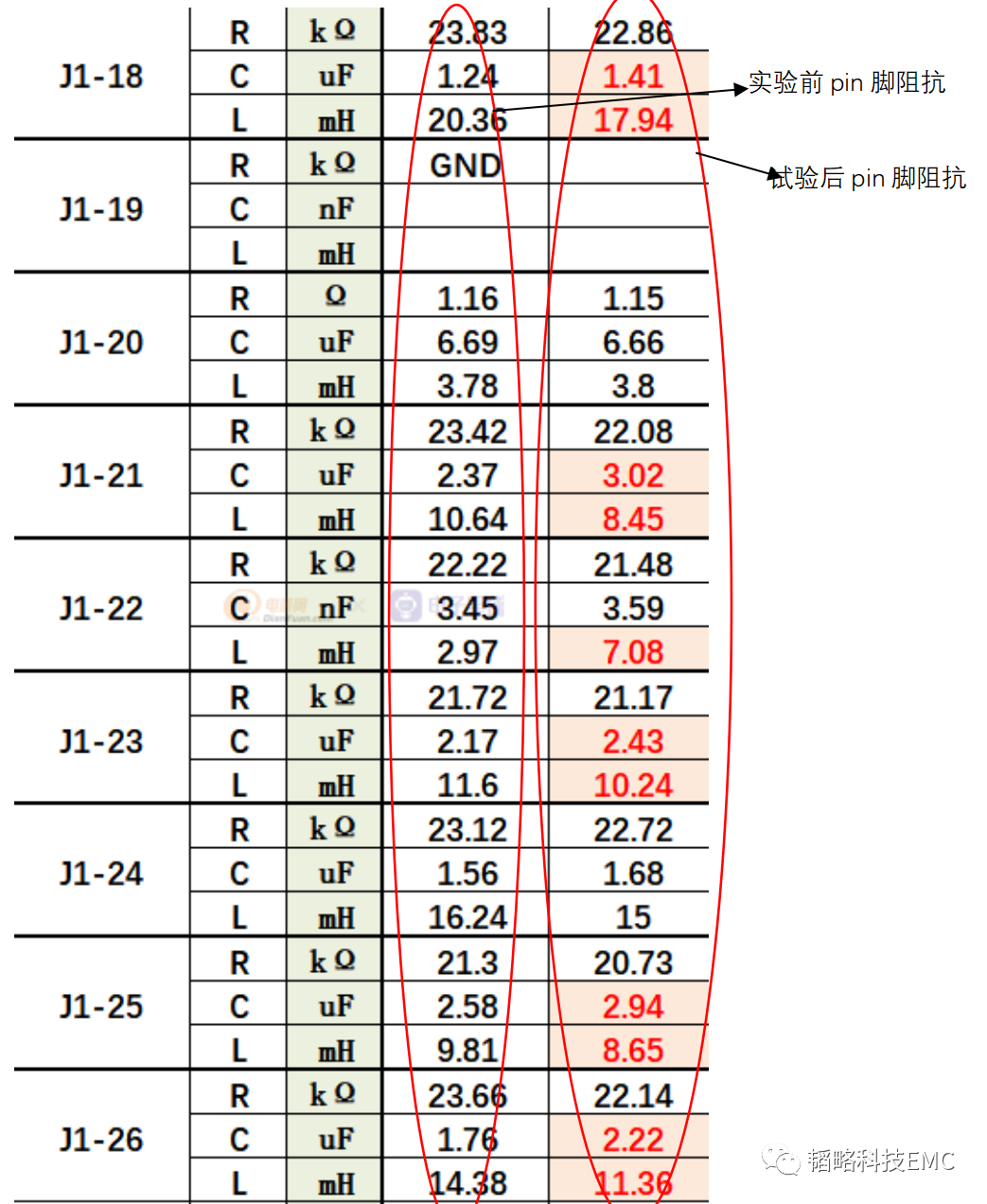

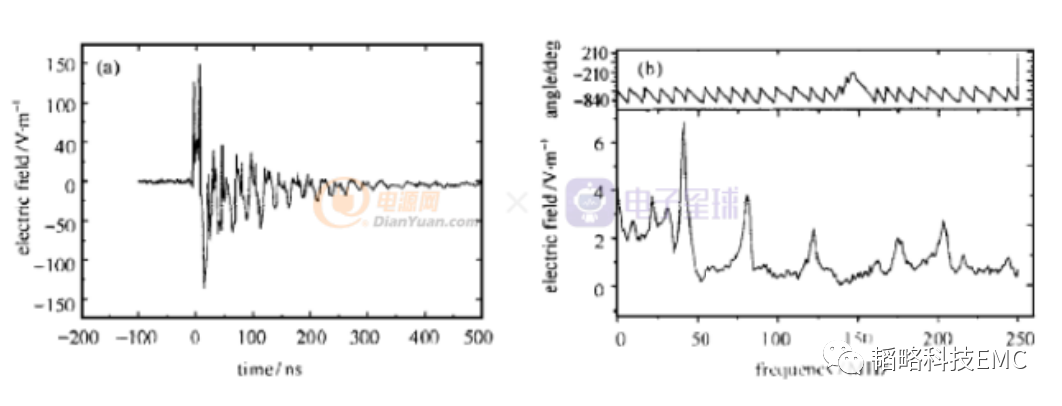

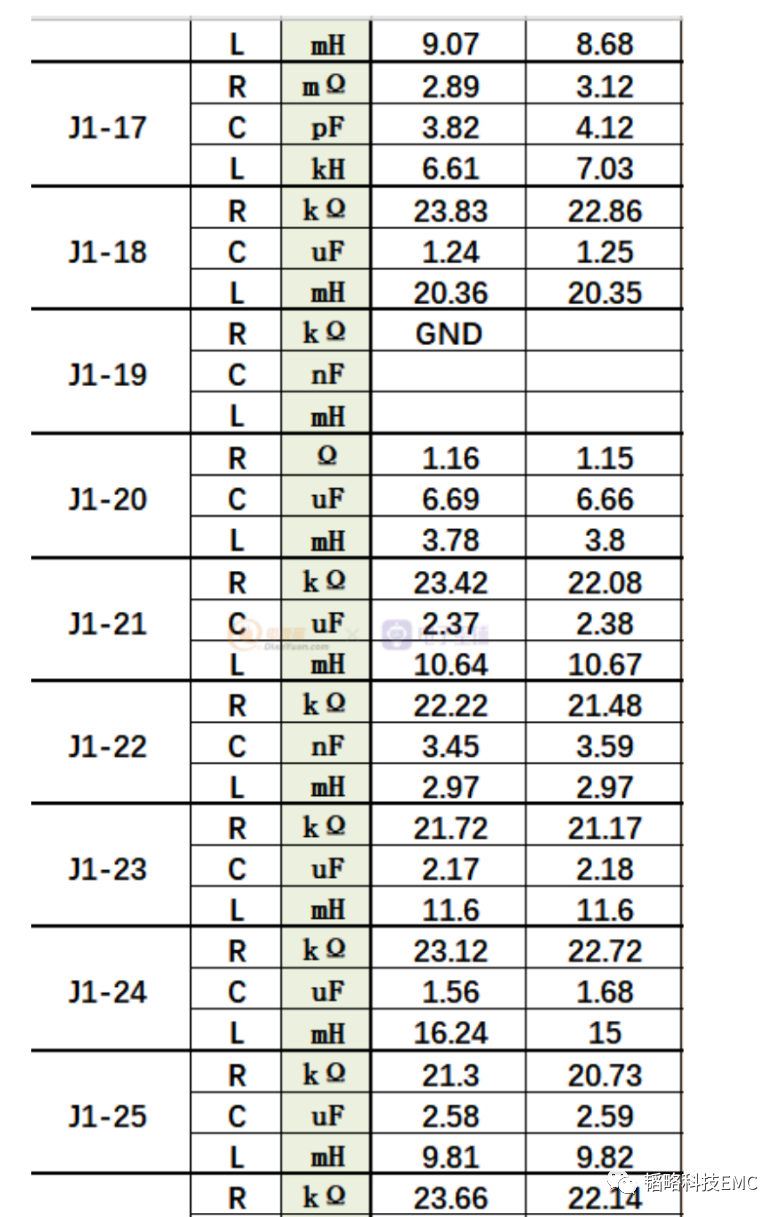

实验现象:在对车载产品进行ESD ±4KV Pin放电实验时,发现有的pin脚在实验前和实验后RCL阻值偏离超过了10%(实验标准),如下图所示:

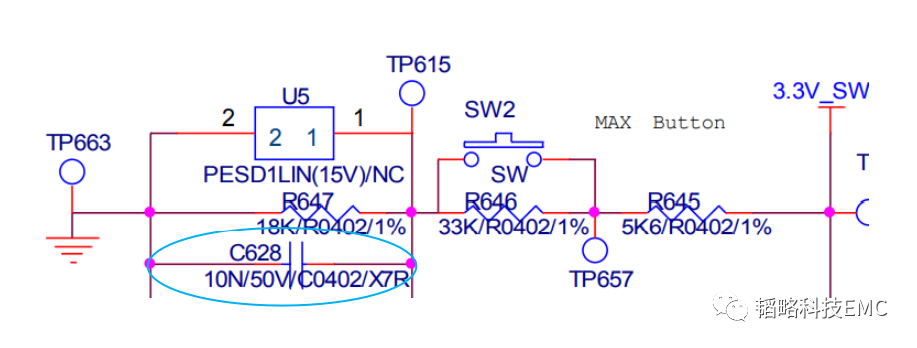

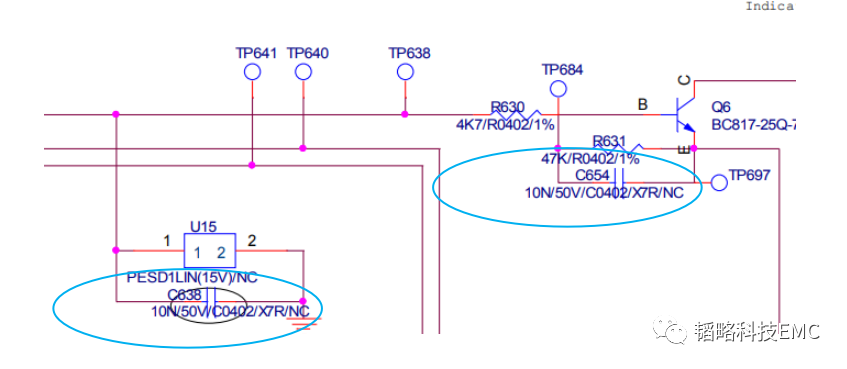

图1 PIN脚实验前后RCL对比 分析数据发现,能够通过ESD实验的都是pin脚接口电路增加10nf电容,没有通过ESD实验的,都是pin脚接口电路既未有ESD管,也没有10nf电容,三极管电路直接暴露在接口处。 我们查阅三极管规格书,发现规格书提到在 HBM模式下,该三极管可以满足±4KV的静电要求,但是实测结果表明,端口不增加ESD管或吸收静电的电容,是无法通过ESD放电实验。

图2 对外接口选用10nf电容

图3 对外接口没有选用10nf电容

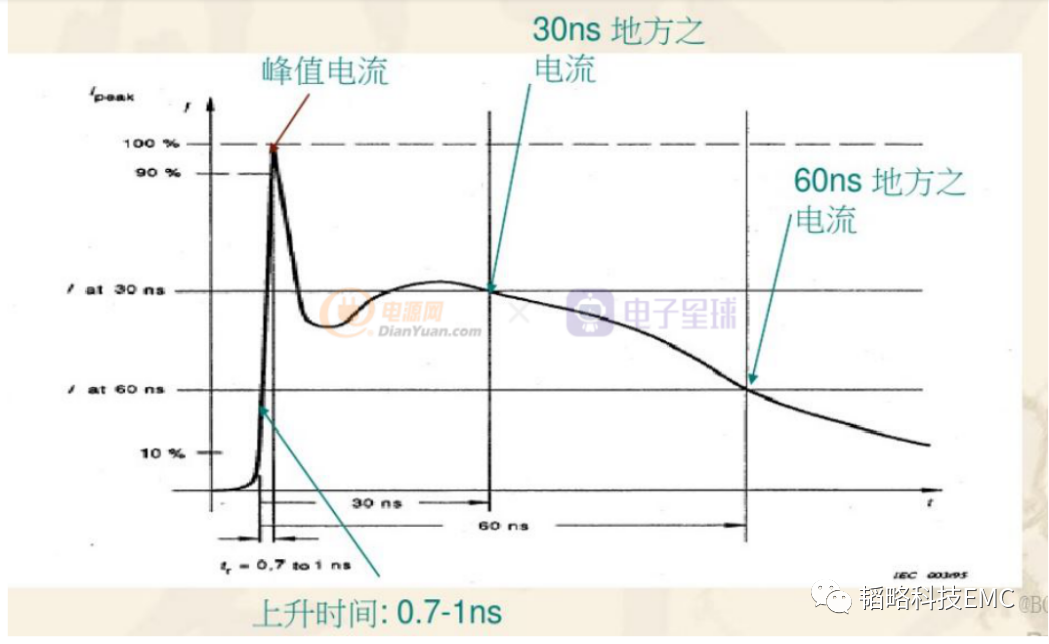

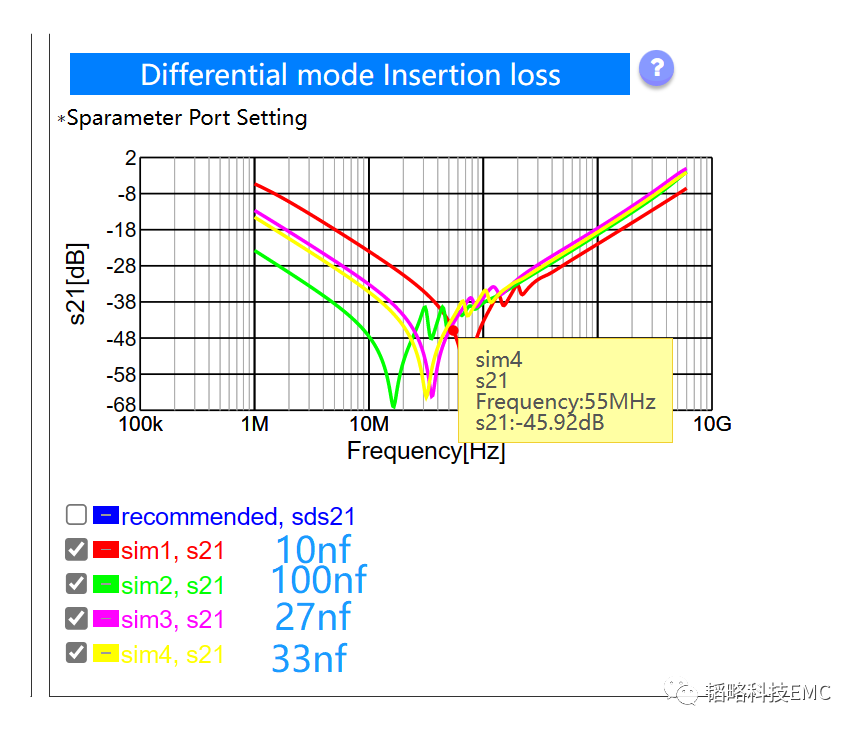

至于为什么选用10nf电容可以通过ESD实验,我们查阅相关资料发现,ESD的放电能量峰值集中在前30ns以内,频谱图发现最高能量峰值是50MHz。

图4 电容放电曲线图

图5 ESD放电频谱图

我们通过村田网站的插入损耗仿真分析发现10nf电容,27nf电容,33nf电容在55MHz均有较低的阻抗,但是这时候,我们应该选择用10nf电容,这是由于27nf,33nf电容在55MHz时已经超过了自谐振频率,呈一定电感性,可能会跟电路中其他寄生电容,形成LC谐振,所以我们最终应用10nf电容。

图6 村田网站各个电容插入损耗图

在选用10nf电容后,我们重新做±4KV的静电实验,下图是测试结果,发现实验前后所有Pin脚的RCL阻值在实验前后都控制在10%以内,即可以通过实验。

图7 选用10nf电容后ESD复测结果

总结:1.从降本角度考虑,不选用ESD管的情况下,10nf的电容可以帮助我们通过±4KV的Pin脚放电测试;

2. 由于制造工艺的影响,电容的工作频率需要小于其谐振频率,否则跟其他电容并联使用时,会形成并联LC谐振,引起EMI干扰。

审核编辑:刘清

-

电容在ESD测试整改中的妙用2023-12-07 1333

-

电容在ESD整改中的应用2023-10-09 1305

-

机械振动测试讲解PPT课件下载2021-07-07 1260

-

EMC设计中电容应该如何使用2020-10-19 1327

-

esd,emc设计优化2017-07-02 4137

-

PCB测试讲议2016-12-16 620

-

芯片测试讲解2016-08-08 1934

-

电源设计中的EMC、EMI、ESD概念简述2016-01-19 4948

-

静电放电ESD测试讲义(程智科技)2015-08-19 12172

-

电路原理图设计checklist——EMC/ESD2012-12-06 7122

-

电容在EMC设计中的应用技巧2009-07-05 638

全部0条评论

快来发表一下你的评论吧 !