LTspice差放分几种玩法?基于CSA23x-2

电子说

描述

续上一集,LTspice(3) 差放分几种玩法?基于CSA23x-1

通过简单的例子大概知道怎么去写一个仿真模型,就像是画电路图将网表直接写出一样,根本不需要原理图直接画pcb那么骚。感觉比直接画原理图还要有意思的多。

有点像是凭空搭洞洞板的感觉。记得读书时候考试科目就是拿洞洞板搭电路。

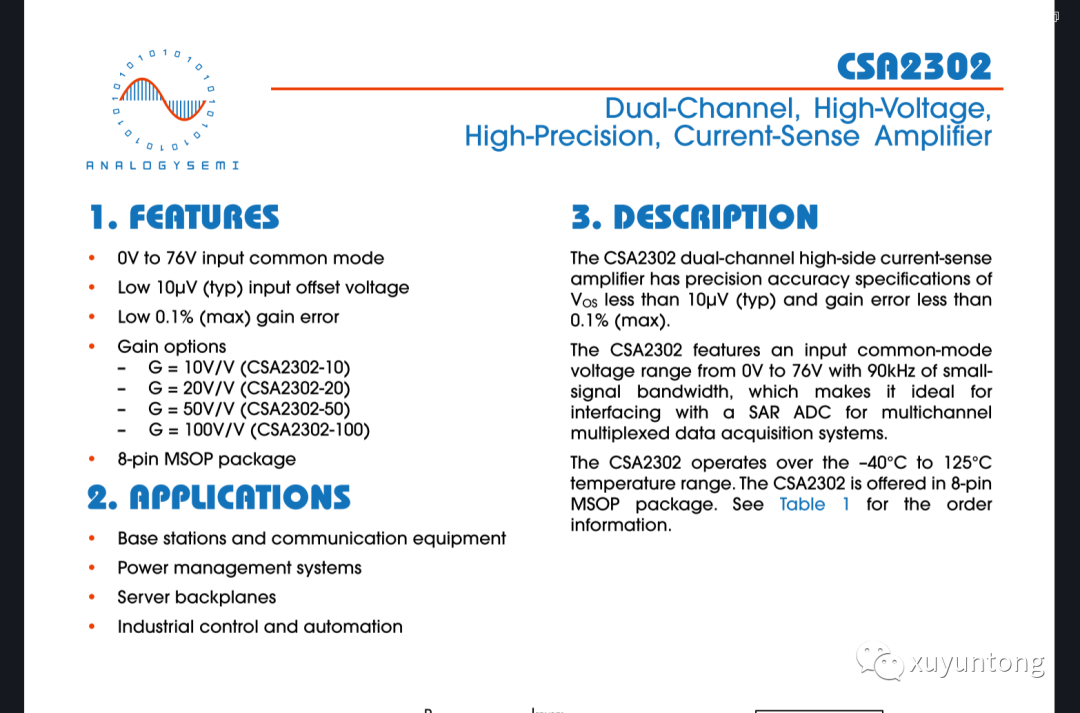

回到正题,之前语句中使用了E1 这个东西,那么E1是做什么用的?

.subckt div N1 N2 GND

R1 N1 0 100k

E1 N2 0 N1 0 50

.ends div

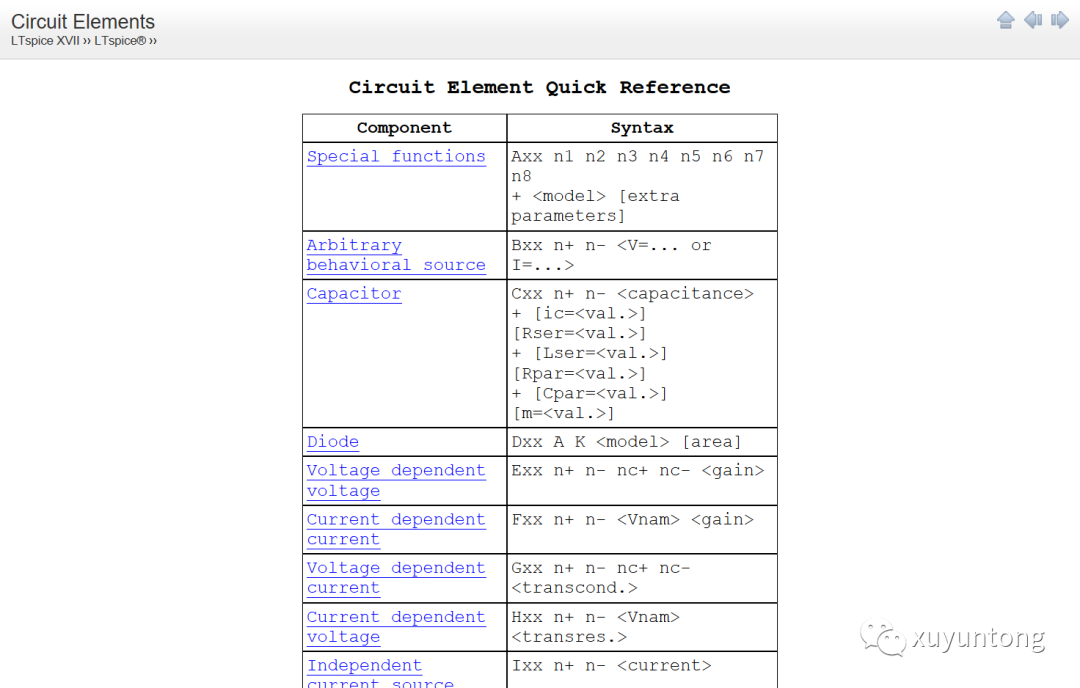

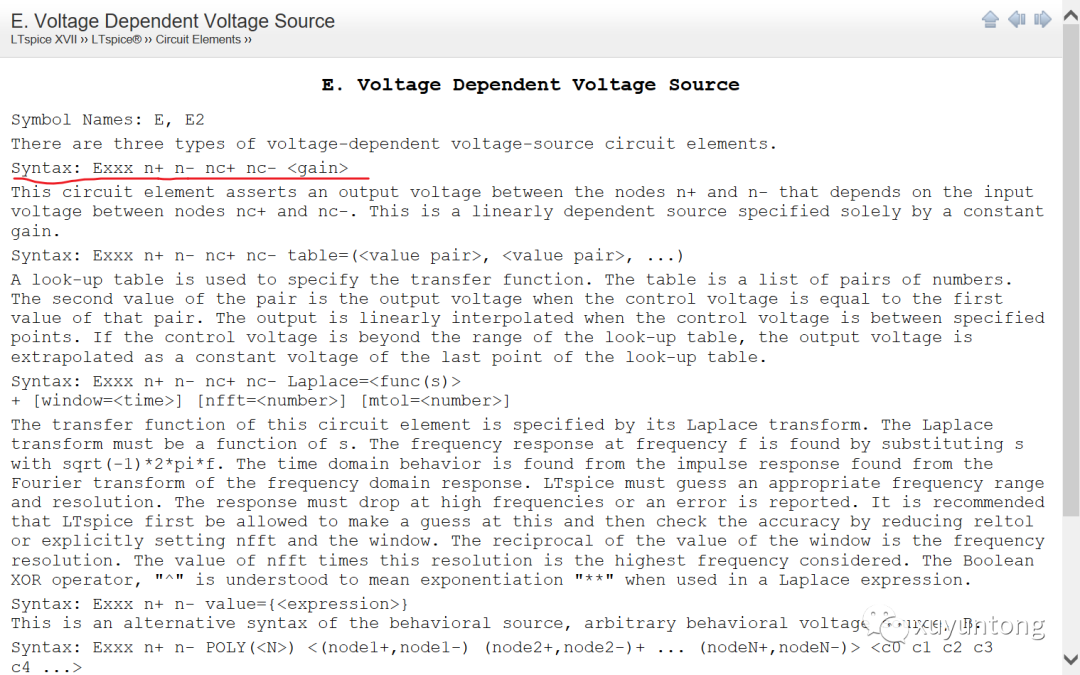

打开LTspice帮助找到以下页面 点到 voltage dependent voltage 里面有关于电压源的描述

大概意思就是说,输出电压是N+和N-输入电压是Nc+和NC-其关系是两个之间的GAIN的倍数。因为CSA23设置的是50倍所以我们整个50倍的。

*

* This is the circuit definition

.subckt CSA23 IN+ IN- VOUT REF GND

*set input and output pins

*the setting gain is equal to 50

*join to network Vo

E1 VO REF IN+ IN- 50

*join to offset 1mV m=micro Meg=mega

E2 VOUT REF value={V(VO,REF)+1m}

.ends CSA23

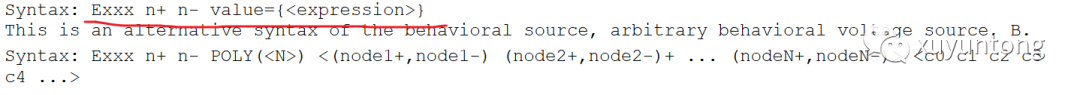

其中第9行代码写到,value={V(VO,REF)+1m}这个似乎没有看过,接着往下拉。

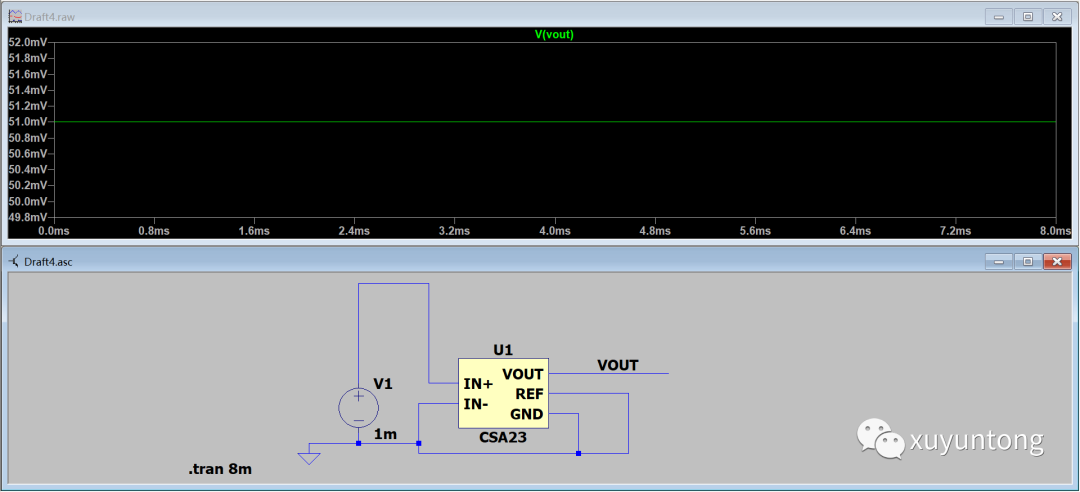

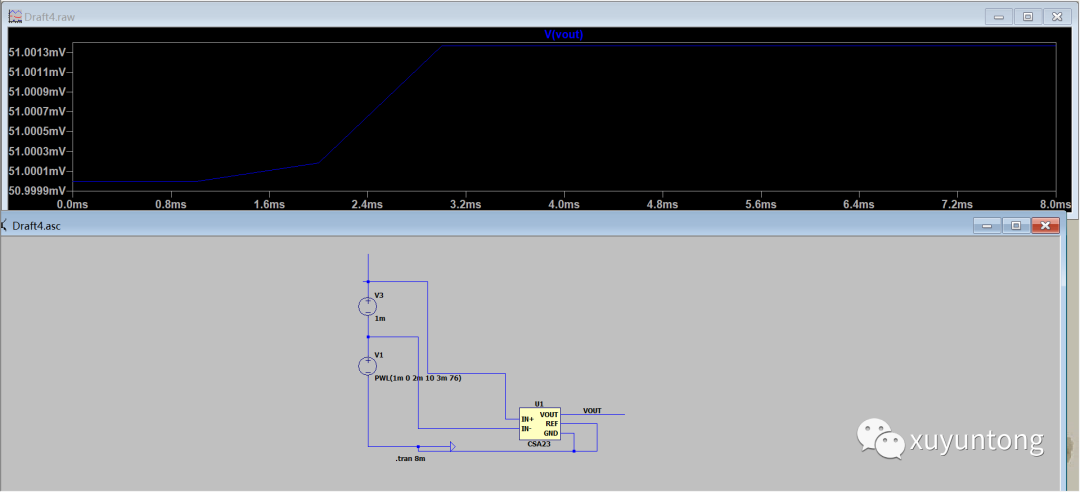

他是可以支持自定义表达式的,就是说你想要什么对应关系直接把你想要的对应关系写进去就行,这里我只加个offset。新建器件仿真得出下图。50倍增益1mV的失调电压。基本function有了可以开始整活了。

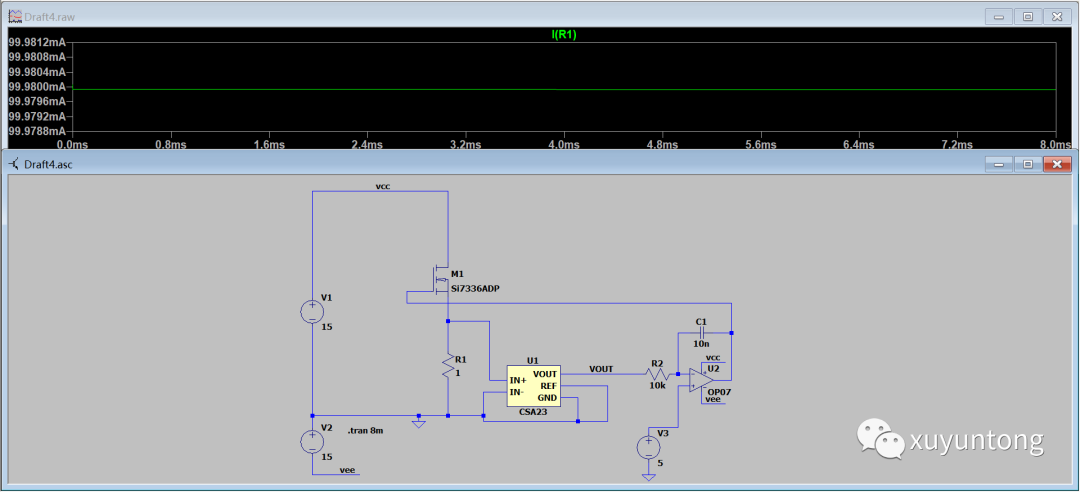

上回似乎说到用ldo做恒流源,但是此次可以用CSA23做恒流源。其实现如下

R1100mAGAIN+offset=5V所以其电流约等于99.98mA,当然初始误差可以通过dac校准掉,对我们没有多大影响,但是共模的变化就会导致误差动态变化,这个就比较难校准掉,所以建议选择共模抑制比比较好的运算放大器。

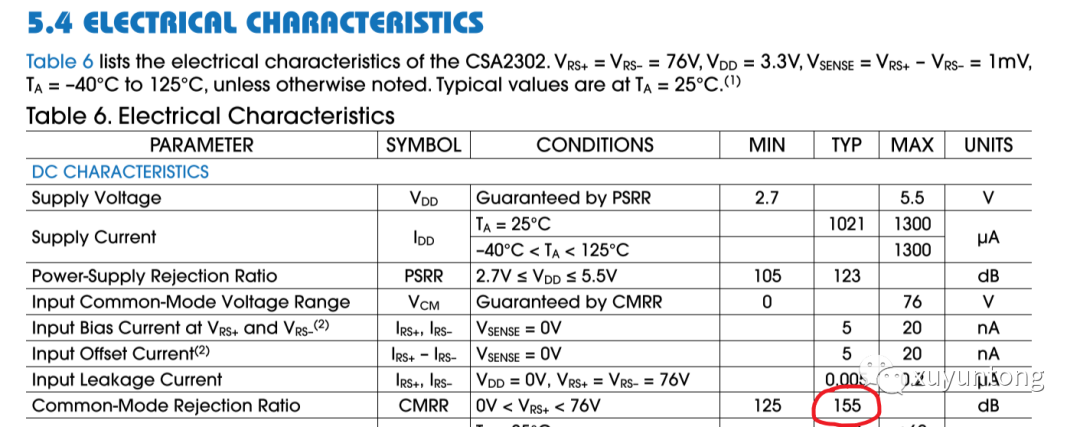

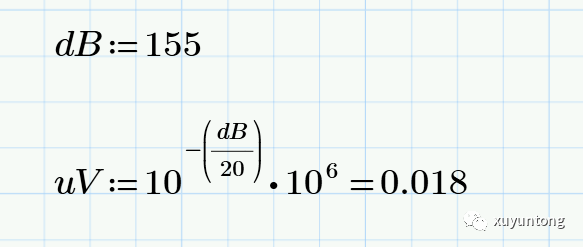

CSA2302的CMRR在0~76V的范围内典型值为155db,代入计算。

db和倍数的关系是这样

20log(10,AV)=db

得出的是输入的共模电压每变化1V那么输出电压变化0.018uV

既然如此那我们再次更新下模型。

*

* This is the circuit definition

.subckt CSA23 IN+ IN- VOUT REF GND

*set input and output pins

*the setting gain is equal to 50

*join to network Vo

E1 VO REF IN+ IN- 50

*join to offset 1mV m=micro Meg=mega

E2 VOUT REF value={V(VO,REF)+1m+V(IN-,0)*0.018u}

.ends CSA23

看到不同共模电压变化的时候输出电压变化并不是特别大。其V1作为电压源设置从0V到76V输出电压变化非常小。因为比较高的CMRR其电流高位采样的精度就有保证。剩下的事就交给DAC去吧~

-

求助,关于差分运放AD8129在Ltspice里的仿真问题求解2025-03-21 2557

-

常用的差分电路有哪几种?2023-09-19 7578

-

LTspice差放分几种玩法?基于CSA23x-12023-08-02 3419

-

LTspice AD4001 THD仿真(反相/增益配置/差分)2021-03-23 1230

-

运放基本参数仿真演示LTSPICE文件2021-01-29 1490

全部0条评论

快来发表一下你的评论吧 !