芯片级LNA设计之基本共源极电路解析

RF/无线

描述

前几天,受了一下刺激。

从队友那得知,去年研发的产品,好不容易推上量产了,也找到一个大客户,卖了几个月后,被竞争对手吃掉了好多份额。而竞争对手采用的是芯片方案。

一方面呢,也是产品研发的晚了,不是打头阵的,所以红利就没剩下多少了;另一方面呢,还是因为产品研发晚了,其他厂家的同类型的产品已经吃过红利了,打通了市场,所以就有芯片厂商介入了。

在那些量大的低端的市场,感觉都是,先是用分立器件搭上,然后先去市场上试水,一旦量起来了,芯片厂商就介入了,然后分立器件就没得玩了。

理由很简单,芯片只要量一起来,简直就是白菜价,性能还比分立的稳定,看上去还美观,换我也选芯片方案。

因此,芯片还是要看起来。

so,又把razavi的射频微电子给打开了。

没想到时隔两个多月,再看以前看的内容,竟然发现还能看懂,没有完全忘记,真是太惊讶了,同时也很开心!

RAZAVI的chapter 5中,大概是按照这样的思路讲的。

刚开始,讲了LNA的一些性能指标,这和板级的差不多,只不过芯片级的LNA设计,其输出可能不是50ohm阻抗。

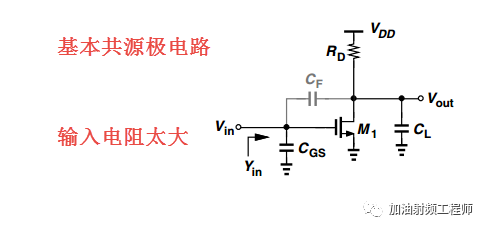

接着对常规的共源(CS)级电路,如下图,进行分析,发现输入电阻太大,与LNA要求的50ohm输入阻抗相差太大,所以需要改进。

基本共源极电路,除了输入阻抗失配外,输出端因为RC时间常数的影响,可能还会限制其工作频率,然后其增益还受工艺电压的影响。

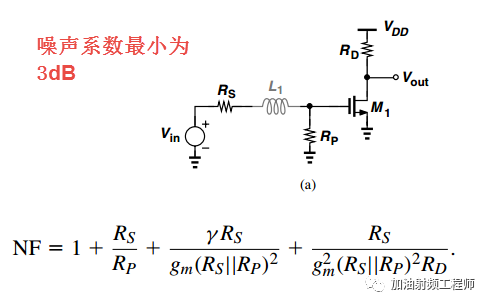

那怎么改进呢,试试直接在输入端并联一个电阻呗,如下图所示。但是发现,50ohm的匹配阻抗是满足了,但是噪声系数>3dB,也不行。

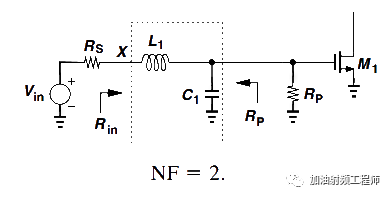

接着又举了个例子,那如果把Rp增大呢,然后中间加一个LC匹配电路,把Rp匹配到Rs,如下图所示。这样噪声系数会不会减小呢?结果算下来发现,噪声系数还是不会小于3dB。所以还要继续改进。

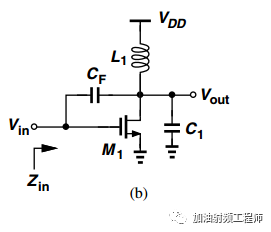

接着考虑电感负载的共源极电路,如下图所示,这个电路,通过选择合适的值,可以获得良好的阻抗匹配,但是因为反馈电容,会增加其他频率处的负阻,导致不稳定。

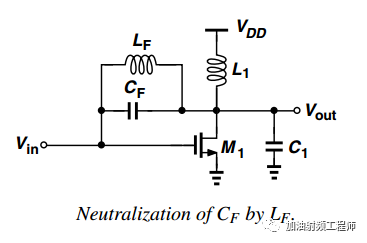

虽然可以通过电感来中和CF的影响,如下图所示,但是因为CF相对来说很小,所以电感就要求很大,从而在输入和输出端引入寄生电容,从而恶化性能。因此,这种拓扑结构,很少在现代RF设计中采用。

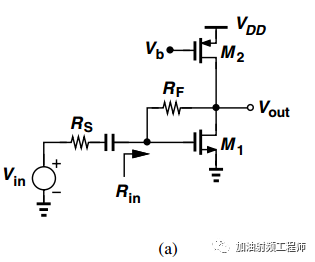

接着又介绍了另外一种架构,仍然基于共源极电路,如下图所示,输入阻抗匹配OK,但是噪声系数还是超过3dB。

也就是说,上面的架构,都不太好,噪声系数偏大。

编辑:黄飞

-

共源极放大器电路及原理2009-12-08 21125

-

芯片级ESD测试方法研究与比较2016-01-11 8897

-

如何设计一个共源级放大电路2023-02-17 3226

-

计算机芯片级维修中心(芯片级维修培训教材)2009-04-05 15235

-

芯片级维修资料分享(一)2019-08-28 3652

-

共漏极放大电路2009-09-16 22134

-

源科将发布芯片级固态硬盘rSSD T1002011-09-16 1080

-

共源级放大电路偏置设计及小信号分析2022-01-07 820

-

解决芯片级功率MOSFET的组装问题2024-08-27 391

-

奥迪威芯片级风扇:面向高性能电子设备的芯片级主动热管理方案2026-02-25 321

全部0条评论

快来发表一下你的评论吧 !