PCB设计时采用哪种走线形式更好?

PCB设计

描述

经常有硬件工程师问到PCB设计的时候,采用哪种走线形式更好?或者说普通微带线和CPW/CPWG共面波导结构各自有那些优点缺点?这个问题看似简单,却很少有资料给出比较肯定的答案。

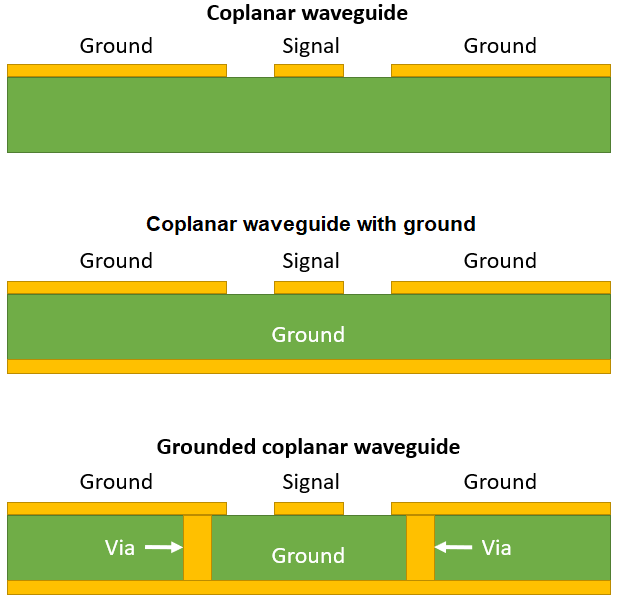

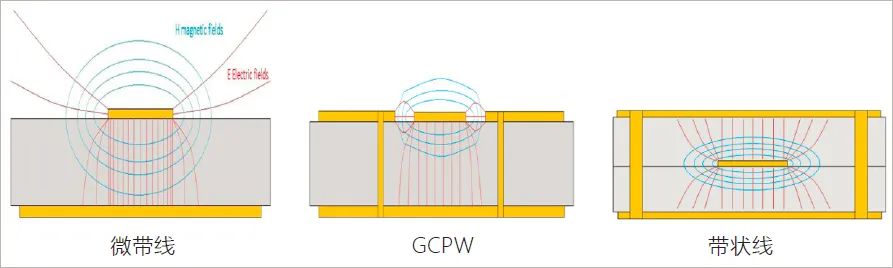

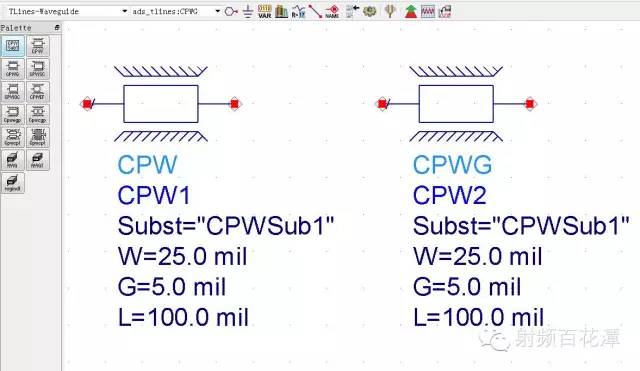

从射频到毫米波频段,微带线,共面波导(CPW)电路是普遍应用的微带形式。传统的共面波导是在PCB材料基片的表面上制作出导体线,底层制作接成平面GND层。被称为接地共面波导(CPW或CPWG)的电路是传统共面波导的一种改进电路。

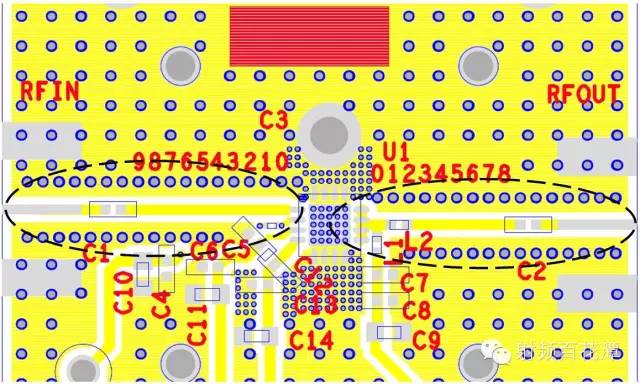

CPWG是在CPW电路结构的底面增加了一个接地平面,并通过过孔via连接上下地平面,CPWG应用上更具广泛性,大多数PCB高速射频PCB都是采用CPWG形式,因为这样连接两端器件可以满足更好的芯片管脚接地要求!

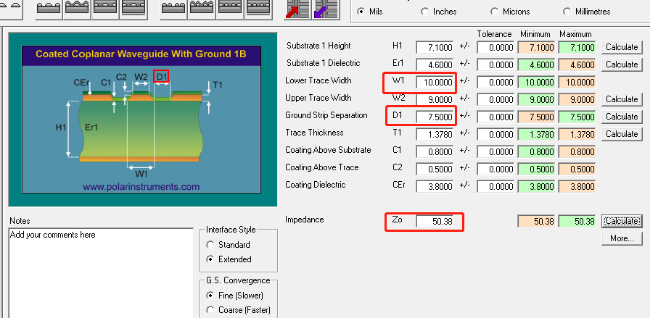

尽管CPW和CPWG两种电路都对邻道信号具有超好的隔离度,从而降低在高密度电路中的串扰。但相比CPW,CPWG会使不连续处辐射量增加,其原因是CPWG中接地过孔的设计会影响阻抗,并增加损耗。但另一方面,当工作频率升高时,相比微带线电路, CPWG地孔的设计可以允许更大的介质材料厚度。

其次,在大功率电路应用中,CPWG比CPW的散热性能更佳,而且增加的接地平面也提高了电路的机械稳定性。最后,当工作在微波和毫米波频率时,对于相同电路材料的微带线和CPWG,CPWG的表面波泄露和辐射损耗更小。

在毫米波及以下频段,CPW和CPWG的生产工艺相对简单且电路性能的稳定性良好。通过传输线传播的电磁波能量,特别是CPWG,其大部分能量都保留在PCB介质材料内部。和微带线电路相比,虽然CPW和CPWG都具有更高的导体损耗,但CPW和CPWG电路的损耗特征是与频率呈线性关系。

而微带线电路,特别是在较高频段时,损耗(因与辐射损耗有关)会随着频率不断变化。此外,CPW和CPWG的损耗可以通过合理设计过孔位置及电路尺寸来降低。

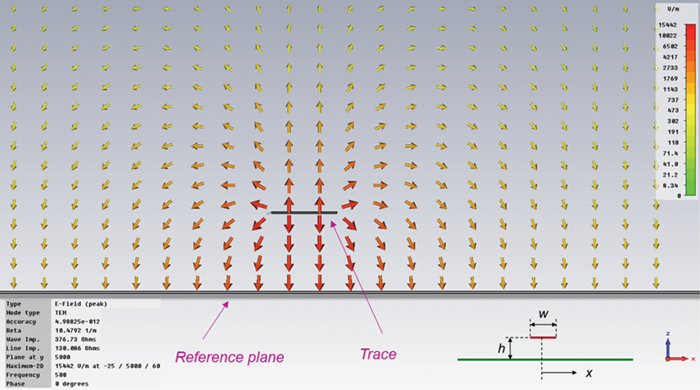

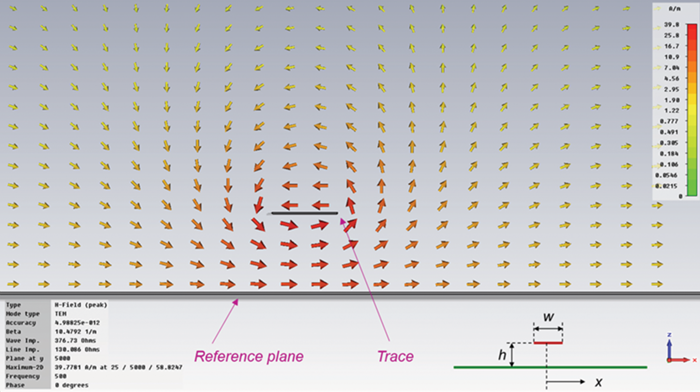

微带线的E、H场

在毫米波等高频频段,电路的尺寸变得越来越小,电路中许多关键元件的尺寸将接近电路所传输信号的波长。对于微带线和带状线,反射损耗和辐射损耗会随着频率的上升而增加,选择合适的电路设计变得尤为关键。如果设计得当,CPW特别是CPWG电路在高频段可获得良好的性能,且可常与微带线相结合使用。在许多高频设计实例中,CPWG都作为微带传输线接口处的高性能接口。

CPW是在介质基片的顶层制作导体,并在导体两侧制作接地平面,呈现地线-信号线-地线(GSG)布局。CPW的地平面与信号线是共面的,通过调节信号线宽度及信号线与地之间的间距来控制阻抗。当信号线的宽度渐变至连接器引脚时,CPW的阻抗值可以保持为常数。

CPWG在介质层的底面增加了接地平面,并通过过孔等方式实现上下接地面的连接。在CPW中电磁能量主要集中在介质层内部。对于CPW和CPWG,当介质基片的厚度为导线宽度2倍以上时,能有效抑制电磁能量向空气中泄露。当大于2倍以上时,特征阻抗基本由中心导线宽度及导线和接地平面的间距决定。CPW特征阻抗值通常在20~250 Ω,而微带线与带状线特征阻抗值通常分别在10~100Ω和20~120Ω。

CPW和CPWG中的耦合

与任何电路技术一样,CPW和CPWG有各自的优缺点。针对不同的应用需要,包括数字电路和模拟电路,必须综合权衡其利弊。CPW和CPWG顶层接地线产生的奇模和偶模电流会造成电路的多种模的耦合。当频率升高时, CPW和CPWG的GSG结构中较近的间隔距离易于形成强耦合,获得较好的寄生模抑制能力,且辐射损耗也较低。增加信号线和地之间的间距或增加信号线宽度(低导体损耗和插入损耗)都能有效降低损耗。当适当增加信号线和地之间的间距,即达到松耦合时,可以降低电路的导体损耗和插入损耗。但其代价是带来更为严重的辐射损耗和杂散失真。因此,对于CPW和CPWG,合适的耦合强度选取是既要有利于获得低损耗的同时也能有效抑制寄生模。

一般情况下,电路的尺寸越薄越利于降低辐射损耗。对于工作于30GHz或者更高频的毫米波电路,辐射损耗是电路总体损耗的一个重要部分。辐射损耗很大程度上与PCB材料的Dk值(介电常数)有关。电路材料的Dk值越高,电路的辐射损耗就越小,然而高Dk值会带来更大的导体损耗。因为当Dk值增大时,为保持特征阻抗不变,信号线的宽度会变窄。因此,导体损耗将增大。

PCB电路中铜的表面粗糙度会影响电场和电流。有效介电常数会随铜表面粗糙度的增加而增大。此外,铜表面粗糙度会影响电路的插入损耗,通常CPWG的影响比微带线小。因为在CPWG电路中,电场和电流集中分布在PCB上GSG区的内部。而在微带线电路中,电场和电流沿着金属导体底部即金属导体粗糙面传播。因此,CPWG的插入损耗受粗糙度的影响比微带线更小。

仿真软件的使用,如是德科技ADS,可以为各种CPW和CPWG电路设计提供合适的参数,比如走线宽度、介质厚度、接地面之间的间距等,这些参数都会对最终性能产生重大影响。

SI9000也是不错的阻抗计算软件,非常简洁方便:

综上,作者推荐PCB设计时:重要的高速射频线采用CPWG形式!

审核编辑:刘清

-

浅谈PCB设计几种常见的走线形式2023-12-11 3939

-

PCB设计的时候采用哪种走线形式更好?2023-12-07 1916

-

有关PCB走线以及如何为PCB设计正确走线的重要事项2023-05-13 7208

-

PCB设计中蛇形走线的作用2023-03-30 6547

-

PCB设计时铜箔厚度,走线宽度和电流的关系.zip2022-12-30 941

-

PCB设计时铜箔厚度、走线宽度和电流有何关系2021-10-09 5931

-

PCB设计时Layout有什么走线策略2019-04-30 1832

-

PCB设计高速模拟输入信号走线方法及规则2018-05-25 10217

-

PCB设计时铜箔厚度走线宽度和电流的关系2016-12-16 1241

-

PCB设计时铜箔厚度,走线宽 度和电流的关系2014-09-08 6055

-

PCB走线镀锡2011-10-31 2406

-

PCB设计时铜箔厚度,走线宽度和电流的关系2007-12-12 16028

全部0条评论

快来发表一下你的评论吧 !