时钟偏移对时序收敛有什么影响呢?

描述

FPGA设计中的绝大部分电路为同步时序电路,其基本模型为“寄存器+组合逻辑+寄存器”。同步意味着时序路径上的所有寄存器在时钟信号的驱动下步调一致地运作。这就要求时钟信号(更准确地说是时钟有效沿)在同一时间点到达所有寄存器的时钟端口,为此,FPGA内部提供了专用的时钟布线资源。然而,即便如此,实际情形是时钟信号往往在不同时间点到达寄存器的时钟端口,这种现象就是时钟偏移。

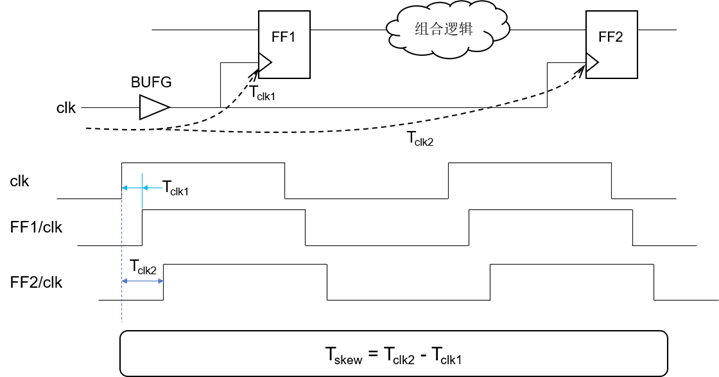

时钟偏移反映了时钟信号到达同一时序路径上的不同寄存器的时钟端口之间的时间差异,如下图所示。时钟clk从源端到达寄存器FF1的时间点为Tclk1,到达寄存器FF2的时间点为Tclk2,故时钟偏移即为Tclk2与Tclk1的差。若clk源端记为零时刻点,那么Tclk1和Tclk2分别对应发送时钟路径延迟和捕获时钟路径延迟。

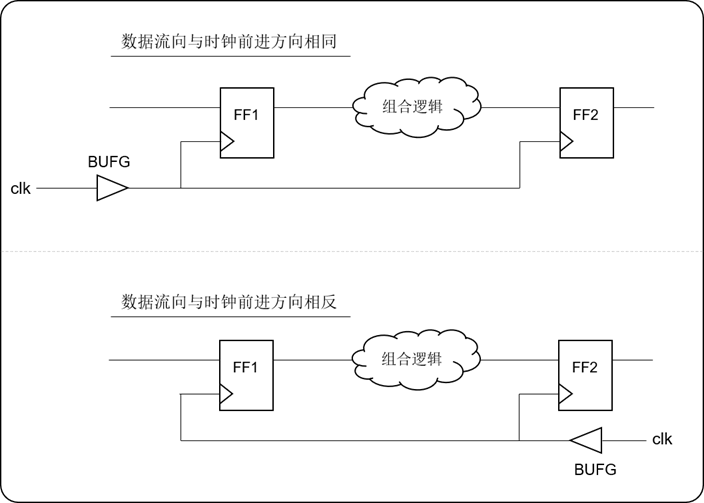

时钟偏移可正可负。通常,若数据流向与时钟前进方向一致,那么时钟偏移为正。否则为负,如下图所示。

时钟偏移对时序收敛有什么影响呢?

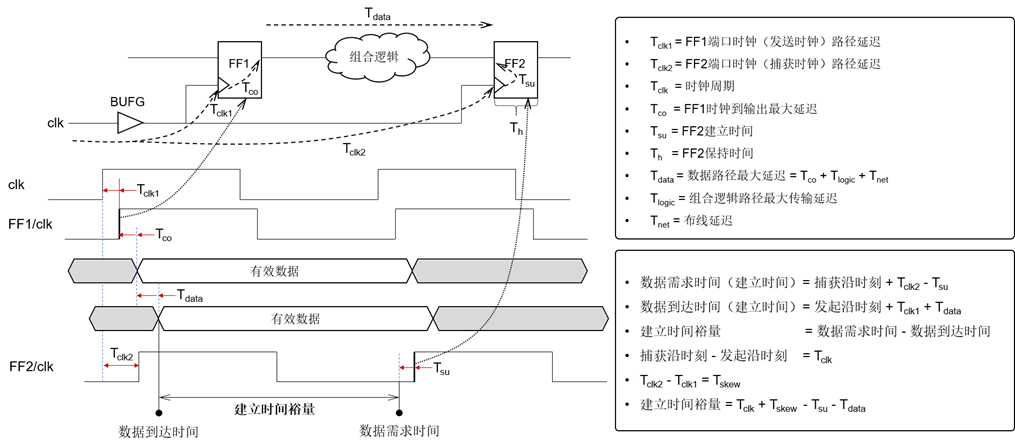

我们从建立时间裕量和保持时间裕量两个角度分析。先以正向的时钟偏移为例。建立时间裕量分析如下图所示,发起沿和捕获沿相差一个时钟周期。由图中建立时间裕量表达式可以得出结论:正向的时钟偏移对建立时间收敛是有利的,相当于捕获寄存器的建立时间由Tsu减小至Tsu-Tskew。

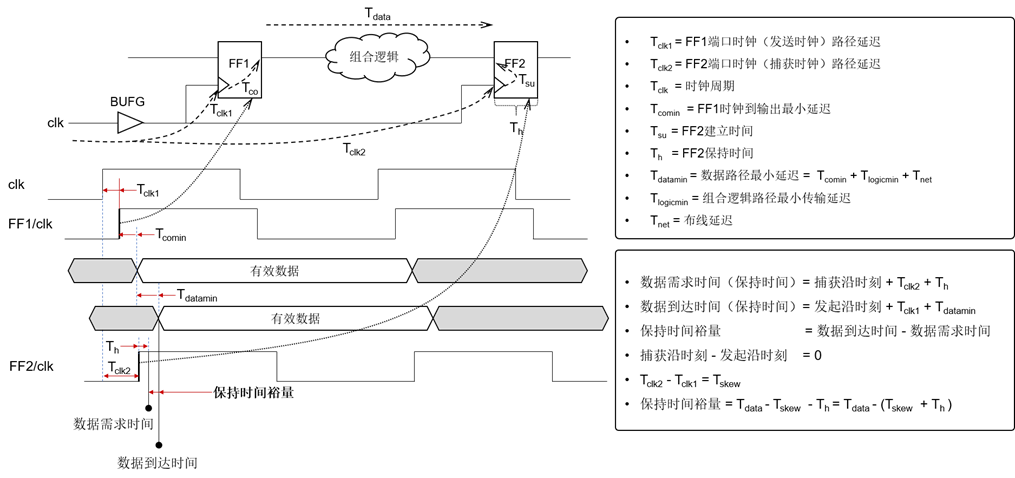

保持时间裕量分析如下图所示,保持时间检查的发起沿和捕获沿为同一时钟沿(保持时间检查是基于建立时间检查的,要求当前发送沿发送的数据不能被前一个捕获沿捕获;下一个发送沿发送的数据不能被当前捕获沿捕获)。由图中保持时间裕量表达式可以得出结论:正向的时钟偏移不利于保持时间收敛。相当于数据在有效沿到达之后还要稳定保持的时间变长了,由原来的Th变为Th+Tskew。这显然阻碍了保持时间收敛。

结合建立时间裕量和保持时间裕量表达式,若Tskew为负,则建立时间收敛更加困难,保持时间收敛更加容易。

审核编辑:刘清

-

进行RTL代码设计需要考虑时序收敛的问题2020-11-20 5074

-

错误时钟偏移计算导致错误时序收敛的解决方案2020-12-24 7779

-

UltraFast设计方法时序收敛快捷参考指南2021-11-05 6221

-

记录一次时序收敛的过程2023-11-18 1993

-

FPGA 高级设计:时序分析和收敛2024-06-17 2115

-

FPGA时序收敛学习报告2011-09-23 4072

-

零基础学FPGA (二十七)从静态时序分析到SDRAM时序收敛 下2015-03-31 14629

-

详解FPGA的时序以及时序收敛2019-07-09 3088

-

请问如何收敛高速ADC时序?2021-04-14 1474

-

有哪些方法可以解决时序收敛的问题?2021-04-26 3391

-

fpga时序收敛2017-03-01 1002

-

基于MCMM技术IC时序收敛的快速实现2017-10-20 1236

-

时钟抖动和时钟偏斜讲解2023-04-04 5596

-

地阻抗对时钟的影响2023-11-23 911

-

时钟抖动和时钟偏移的区别2024-08-19 3603

全部0条评论

快来发表一下你的评论吧 !