如何在VScode中用AI补全V/SV代码呢?

电子说

1.4w人已加入

描述

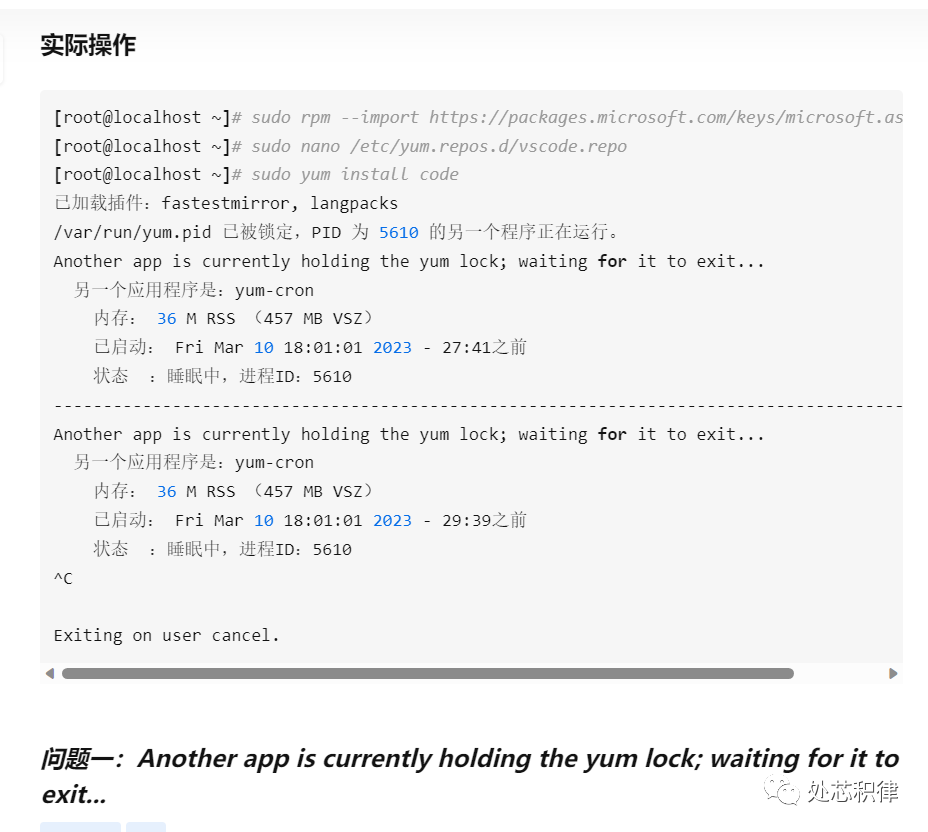

昨天群里小伙伴说在VScode中用AI写verilog效果很好。小编以前编辑代码都是用gvim。抱着学习的心态,我在linux下尝试了下用VScode写代码。小编的环境的Centos,下面文章内容以Centos为

首先是VScode的安装。在网上搜索VScode 安装。

看了一圈,各有各的说法,不少内容冗长。

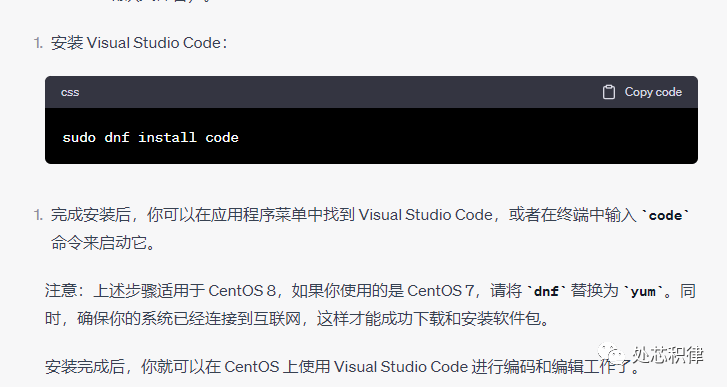

直接上GPT,干净利落。

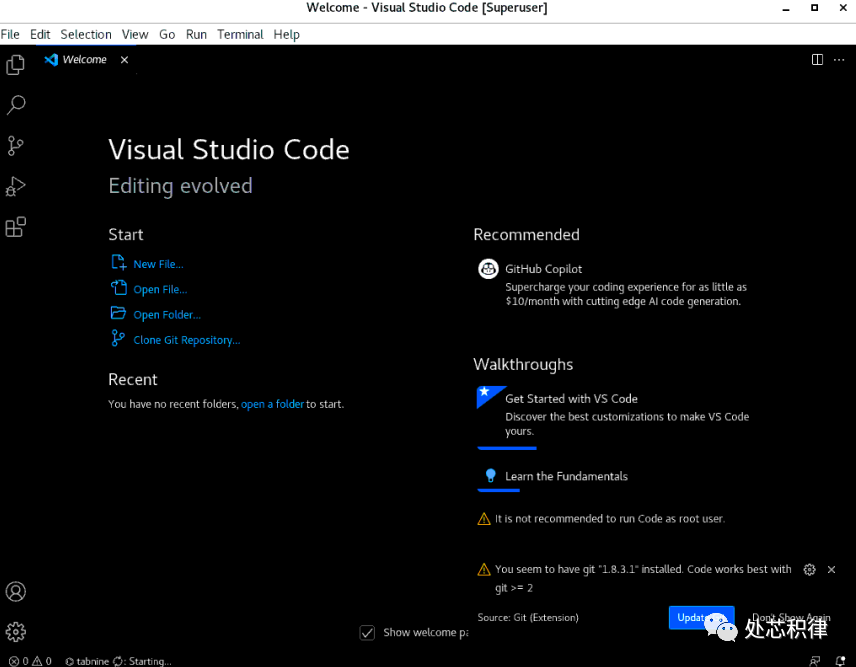

看下安装完的效果

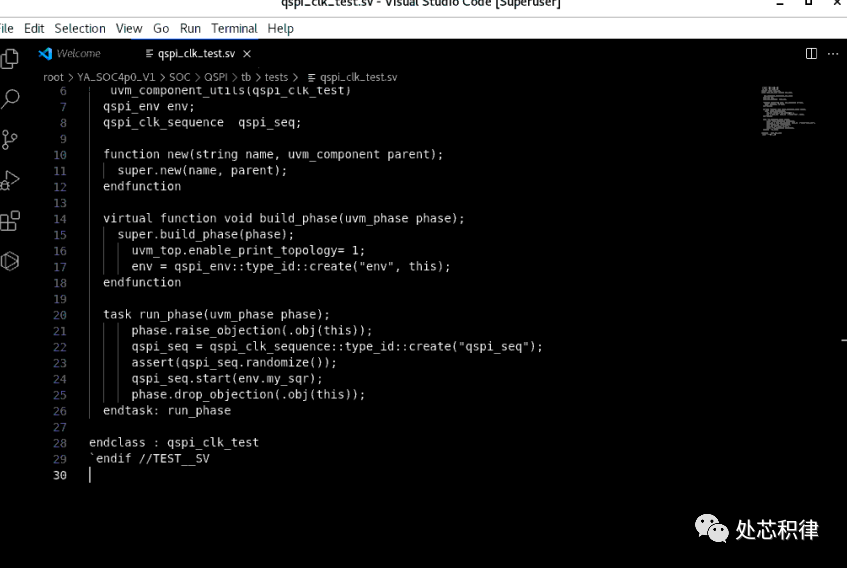

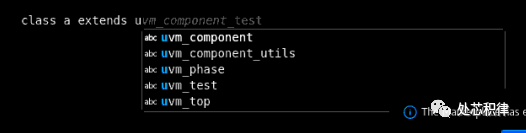

接下来打开一份verilog文档,好像没什么特别。

编辑下试试,带有自动补全的功能,不错不错。

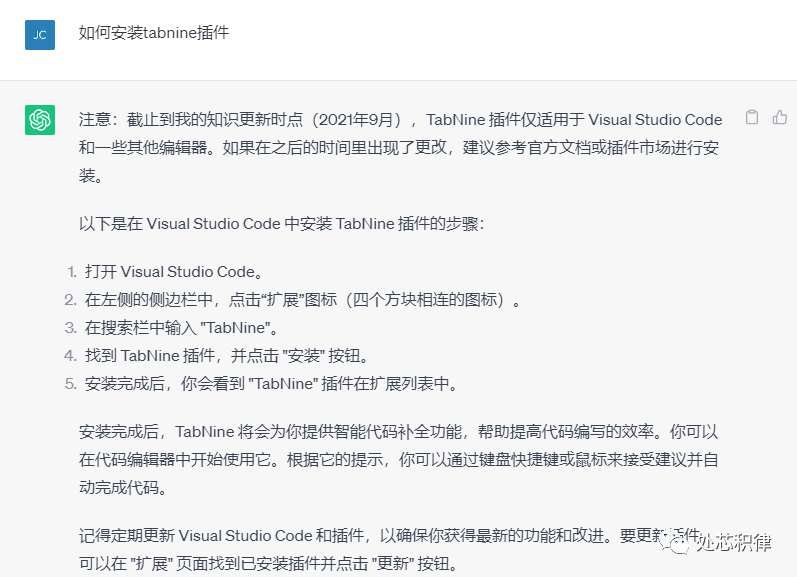

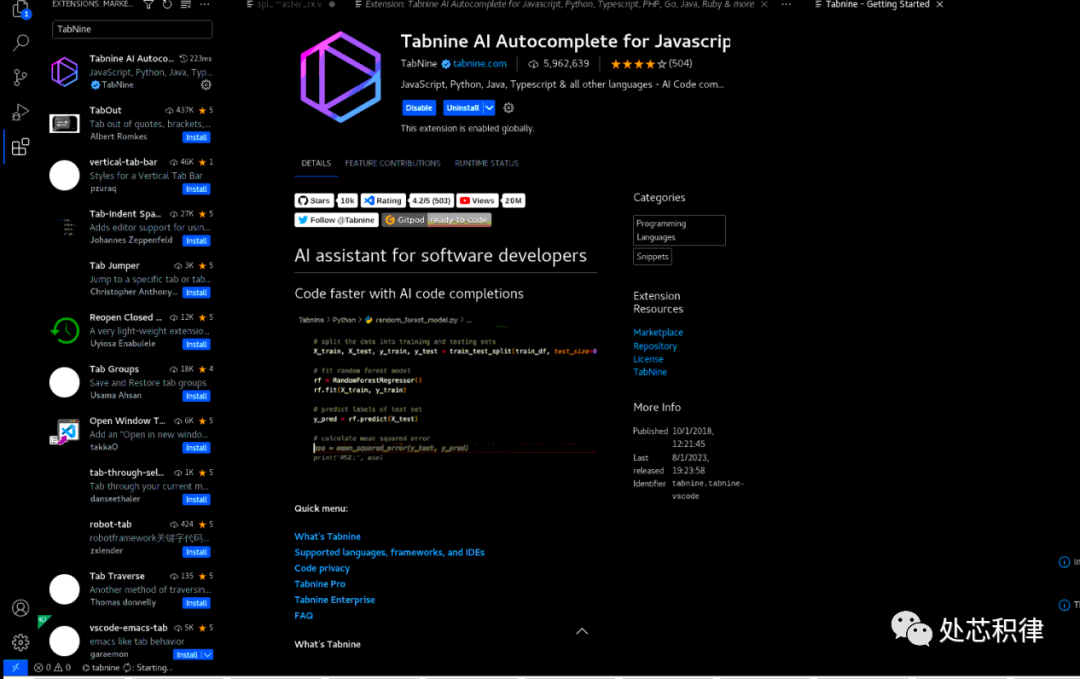

继续探索,在VScode 上装上朋友介绍的Tabnine AI 插件。具体安装方法,继续GPT。

安装完之后效果如下。

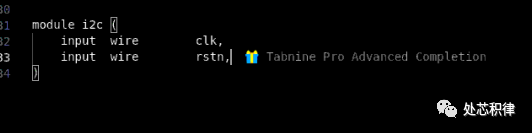

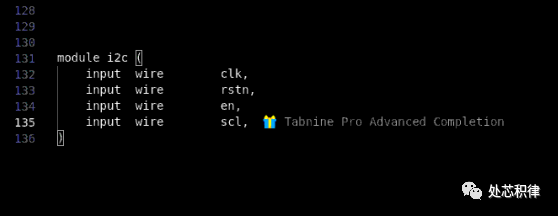

我们开始尝试下朋友说的逆天功能,尝试写个I2C的model。

写完I2c的名字,直接出来了clk和rst。这个地方不是太准确。

按 tab,继续自动填补

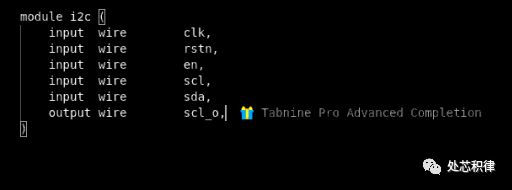

现在有点样子了

如果一直换行,一直tab,他会一直补下去。这个时候需要我们人工进行干预,除去错误的地方。

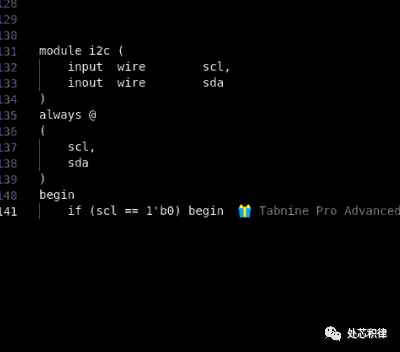

接下来我们继续编辑 model的主体部分。我们发现 AI可以根据模块的名字给出建议的代码。

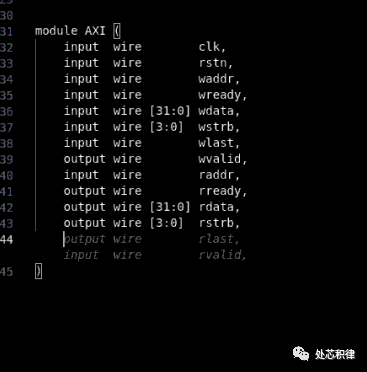

下面是AXI的例子

这和我们用GPT生成代码的效果是一样。通过上面实验,我们发现引入AI 插件能够极大方便我们写verilog/system verilog的效果。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

请问STM32CubeIDE v1.16.1支持代码补全功能吗?如何开启呢?2025-03-14 554

-

如何在VSCODE下面进行RISC-V的调试2024-07-25 1454

-

如何在vscode上面开发stm322022-10-08 3262

-

sv810是什么?sv810有何功能呢2022-03-03 1892

-

怎样使用VSCode去编译一种Keil工程呢2022-02-23 1220

-

使用vscode进行开发2022-01-10 1727

-

使用VSCode编译Keil工程2021-12-29 807

-

在ubuntu中用vscode编译调试C\C++2021-12-22 1436

-

如何在ubuntu中用vscode编译调试C\C++2021-12-14 969

-

VScode在ubuntu中的简单应用2021-11-08 1142

-

如何在VSCode上配置Arduino?2021-09-26 2827

-

怎样用VScode+STM32CubeMX去开发STM322021-08-23 1897

-

基于差异性代码克隆的代码块补全提示方法2021-05-28 920

-

VC6.0代码补全插件2015-12-08 1323

全部0条评论

快来发表一下你的评论吧 !