AES HWIP技术规格

电子说

描述

AES HWIP技术规格

一、概述

本文档介绍了AES 硬件 IP 功能。高级加密标准 (AES) 是 OpenTitan 协议中使用的主要对称加密和解密机制。 AES 单元是一个加密加速器,它接受来自处理器的请求以加密或解密 16 字节的数据块。它作为外设模块连接到芯片互连总线,符合外设功能的要求指南。

1、特点

AES单元支持以下功能:

• 在以下密码块模式下使用 AES-128/192/256 进行加密/解密:

• Electronic Codebook (ECB) mode,

• Cipher Block Chaining (CBC) mode,

• Cipher Feedback (CFB) mode (fixed data segment size of 128 bits, i.e., CFB-128),

• Output Feedback (OFB) mode, and

• Counter (CTR) mode.

• 可以删除对 AES-192 的支持以保存区域,并使用编译时 Verilog 参数启用/禁用

• 使用面向域的掩码 (DOM) 来加重侧信道分析 (SCA) 的密码核心的一阶屏蔽,可以选择使用编译时 Verilog 参数禁用(有关更多详细信息,请参阅下面的安全强化

• AES-16/12/14 模式下每 16 字节数据块的 56/66/72 时钟周期(未屏蔽实现)和 128/192/256 时钟周期 (DOM) 的延迟 内部伪随机数发生器 (PRNG) 的自动和软件启动重新设定种子,具有可配置的重新设定速率,导致最大熵消耗率范围为 286 Mbit/s 至 0.035 Mbit/s(100 MHz 时)。

• 加重控制路径上的故障注入 (FI) 的对策(有关详细信息,请参阅下面的安全强化)

• 基于寄存器的数据和控制接口

• 系统密钥管理器接口,用于可选密钥旁加载,不向连接到系统总线互连的处理器和其他主机公开密钥材料。

• 动态生成轮次密钥,与通过寄存器接口提供的单个初始 128/192/256 位密钥的实际加密/解密并行(有关更多详细信息,请参阅下面的操作理论

该 AES 单元针对中等性能(16 个并行 S-Box,未屏蔽实现每轮 ~1 个周期,DOM 实现每轮 ~5 个周期)。对于高带宽数据流,不需要高速、单周期操作。

ECB、CBC、CFB、OFB 和 CTR 以外的密码模式超出了此版本的 AES 单元,但将来的版本可能会受支持。

2、说明

AES 单元是一个加密加速器,它接受来自处理器的请求以加密或解密 16B 数据块。

• 它支持电子码本 (ECB) 模式下的 AES-128/192/256、

• 密码块链接 (CBC) 模式、

• 密码反馈 (CFB) 模式(固定数据段大小为 128 位,即 CFB-128)、

• 输出反馈 (OFB) 模式

• 计数器 (CTR) 模式。

有关这些密码模式的详细信息,请参阅分组密码操作模式的建议。将来的版本中可能会添加其他密码模式。

AES 单元作为外设模块连接到芯片互连总线。 与处理器的通信通过一组控制和状态寄存器 (CSR) 进行。

这包括输入/输出数据和密钥,以及状态和控制信息。

AES 单元的未来版本可能包括一个单独的接口,通过该接口,可能的系统密钥管理器可以提供密钥,而无需将其暴露给连接到系统总线互连的处理器或其他主机。(这样更加合理,这样就避免了在通路上通过信号检测能获取到密钥,当然防侧信道攻击针对一般是处理器运算时,这个核发出的电磁信号来检测出密钥或者计算模式)

二、操作理论

AES 单元支持使用单个共享数据路径在 ECB、CBC、CFB、OFB 和 CTR 模式下对 AES-128/192/256 进行加密和解密。

也就是说,它可以进行加密或解密,但不能同时进行两者。

AES 单元具有密钥扩展机制,可从通过寄存器接口提供的单个初始密钥即时生成所需的圆形密钥。这意味着处理器只需通过寄存器接口向 AES 单元提供初始加密密钥。然后,AES 单元使用此密钥生成所有整数密钥,因为它们需要与实际加密/解密并行。与通过寄存器接口传递所有圆形密钥相比,这种设计的优势包括:

• 降低存储要求,减小电路面积:AES-15 只需要 128 个 3 位密钥寄存器,而不是存储 256 个 256 位整数密钥:

• 处理器向其写入初始密钥的一组寄存器,即用于加密的启动密钥,

• 一组寄存器用于保存当前完整密钥,以及

• 一组寄存器,用于保存上一轮加密的完整密钥,即用于解密的开始密钥。

• 更快的重新配置和密钥切换:内核只需要执行 8 次写入操作,而不是 AES-60 的 256 次写入操作。

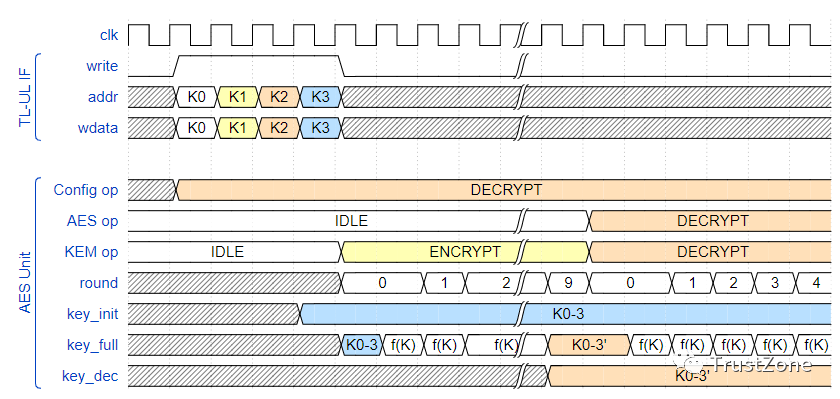

然而,在AES单元可以使用这个新密钥执行ECB/CBC解密之前,每当处理器更改密钥时,即时轮次密钥生成就会以初始延迟为代价。在此阶段,密钥扩展机制以迭代方式计算解密的开始密钥。此延迟阶段的持续时间对应于加密一个 16B 块所需的延迟(即 AES-12/14/16 的 128/192/256 周期)。计算出解密的开始密钥后,它将存储在专用的内部寄存器中供以后使用。然后,AES 单元可以在解密和加密之间切换,而不会产生额外的开销。

对于加密或模式设置为 CFB、OFB 或 CTR,则更改密钥时没有此类初始延迟。如果密钥切换后的下一个操作是 ECB 或 CBC 解密,AES 单元会首先使用密钥计划自动启动密钥扩展(要生成用于解密的启动密钥,实际数据路径在该阶段保持空闲状态)。

AES 单元使用状态寄存器向处理器指示何时准备好通过寄存器接口接收下一个输入数据块。当 AES 单元对数据块执行加密/解密时,处理器提供下一个输入数据块是安全的。一旦上一个加密/解密完成并且新的输入数据可用,AES 单元就会自动开始下一个数据块的加密/解密。输入寄存器的写入顺序无关紧要。

每个输入寄存器必须至少写入一次,AES单元才能自动启动加密/解密。这是默认行为。可以通过将 CTRL_SHADOWED 中的MANUAL_OPERATION位设置为 . 在这种情况下,AES 单元仅在 TRIGGER 中的 START 位设置为(自动清除到下一次加密/解密启动后)后才会开始加密/解密。110

类似地,AES 单元通过状态寄存器指示处理器何时有新的输出数据可供读取。此外,输出数据还有一个背压机制。如果 AES 单元想要完成数据块的加密/解密,但处理器尚未读取以前的输出数据,则 AES 单元将停止。它挂起并且不会丢弃数据。只有在读取了先前的输出数据并且可以安全地覆盖相应的寄存器后,它才会继续。读取输出寄存器的顺序无关紧要。每个输出寄存器必须至少读取一次,AES单元才能继续。这是默认行为。可以通过将 CTRL_SHADOWED 中的MANUAL_OPERATION位设置为 .在这种情况下,AES 单元永远不会停止,只会覆盖以前的输出数据,而与是否已读取数据无关。

1、功能框图

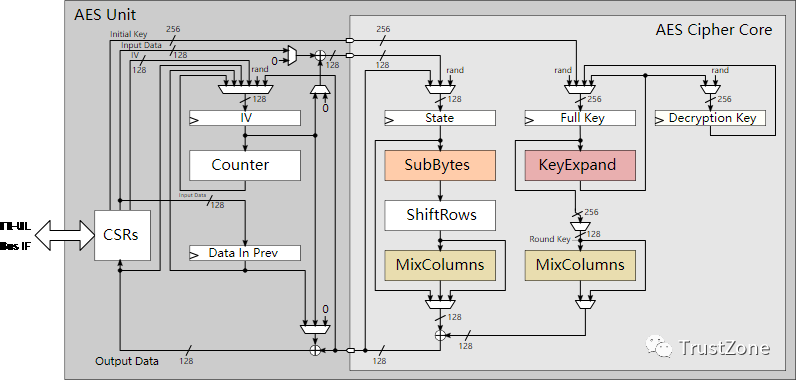

此 AES 单元针对中等性能(未屏蔽实施每轮 ~1 个周期)。对于高带宽数据流,不需要高速、单周期操作。

因此,AES 单元使用具有 128 位宽数据路径的迭代密码核心架构,如下图所示。请注意,为简单起见,下图显示了未屏蔽的实现。有关密码核心的屏蔽实现的详细信息,请参阅下面的安全强化)。

使用迭代架构允许以吞吐量为代价实现更小的电路面积。采用 128 位宽数据路径允许在未屏蔽实现中分别在 AES-12/14/16 模式下实现每 16B 数据块 128/192/256 个时钟周期的延迟要求。

在这里插入图片描述

在密码核心内部,实际密码(左)和轮密钥生成(右)的数据路径在加密和解密之间共享。因此,图中显示的块始终实现相应操作的正向和后向(反向)版本。例如,SubBytes 同时实现了 SubBytes 和 InvSubBytes。

除了实际的 AES 密码内核外,AES 单元还具有一组控制和状态寄存器 (CSR),处理器可通过 TL-UL 总线接口访问,以及一个计数器模块(仅用于 CTR 模式)。该计数器模块根据分组密码操作模式的建议(附录 B.1)实现标准递增功能,固定参数 m = 128。请注意,对于 AES,参数 b = 128,计数器增量为大端序。CFB 模式支持固定参数 s = 128 (CFB-128)。对 128 位以外的数据段大小的支持将需要大量额外的多路复用资源,因此无法提供。初始化向量 (IV) 寄存器和用于保存先前输入数据的寄存器仅用于 CBC、CFB、OFB 和 CTR 模式。

2、AES算法原理

【密码学基础:AES加密算法】[1]

3、设计细节

本节讨论 AES 模块的不同设计细节。

1、数据路径体系结构和操作

AES 单元实现【AES 算法】[2]。这允许在加密/解密之间更有效地共享密码数据路径,因为操作以相同的顺序应用(更少的复用器,更简单的控制),但要求在解密期间使用反向 MixColumns 在所有轮次中转换轮密钥,除了第一轮和最后一轮。

这种架构选择旨在实现高效的密码数据路径共享和低面积占用空间。根据应用方案,其他体系结构可能会提供更合适的区域/性能权衡。例如,如果只使用 CFB、OFB 或 CTR 模式,则根本不使用反向密码。此外,如果密钥很少更改(例如在批量解密的情况下),则存储所有整数密钥而不是动态生成它们可能会有所回报。AES 单元的未来版本可能会提供编译时参数,以便有选择地实例化正向/反向密码部分,以仅允许专用的仅加密/解密单元。

数据路径中的所有子模块都是纯组合的。密码和轮次密钥生成中唯一的顺序逻辑是状态、完整密钥和解密密钥寄存器。

以下描述解释了 AES 单元的工作原理,即 AES 密码的操作如何映射到 AES 单元的数据路径体系结构。斜体短语适用于不同分组密码模式的特性。有关这些密码模式的一般介绍,请参阅【分组密码操作模式的建议】[3]

• 1、配置和初始密钥通过一组控制和状态寄存器 (CSR) 提供给 AES 单元,处理器可通过 TL-UL 总线接口访问这些寄存器。处理器必须首先向CTRL_SHADOWED寄存器提供配置。然后跟随初始键。每个密钥寄存器必须至少写入一次。寄存器的写入顺序无关紧要。

• 2、处理器分别在 CBC、CFB 和 OFB 模式或 CTR 模式下通过 TL-UL 总线接口向四个 IV 寄存器提供初始化矢量 (IV) 或初始计数器值。每个IV寄存器必须至少写入一次。寄存器的写入顺序无关紧要。请注意,在运行时,AES单元在消耗当前IV值后自动更新IV寄存器。每当启动新消息时,处理器必须通过 TL-UL 总线接口提供相应的 IV 值。在 ECB 模式下,无需提供 IV。在 ECB 模式下,IV 寄存器的内容将被忽略。

• 3、输入数据通过四个 CSR 提供给 AES 单元。每个输入寄存器必须至少写入一次。寄存器的写入顺序无关紧要。

• 4、如果有新的输入数据可用,AES 单元将通过执行以下操作自动启动加密/解密。请注意,要使 AES 装置在 CBC、CFB、OFB 或 CTR 模式下自动启动,还必须准备好 IV。如果自上次 IV 更新(由处理器或 AES 单元本身完成)以来,所有 IV 寄存器至少写入一次或均未写入,则 IV 已准备就绪。AES 单元不会使用部分更新的 IV 自动启动下一次加密/解密。通过将CTRL_SHADOWED中的MANUAL_OPERATION位设置为 ,AES 装置可以在手动模式下操作。在手动模式下,每当触发中的起始 位设置为 ,无论 IV 和输入数据寄存器的状态如何,AES 单元都会开始加密/解密。

• AES 单元将初始状态加载到密码内核内的状态寄存器中。

• 根据密码模式,初始状态是输入数据和 IV 的组合。请注意,如果执行 CBC 解密,或者以 CFB、OFB 或 CTR 模式运行,则输入数据也会被注册(框图中的“上一个数据”中的数据)。

• 初始密钥加载到密码内核内的全密钥寄存器中。请注意,如果执行 ECB/CBC 解密,则全密钥寄存器将使用存储在解密密钥寄存器中的值加载。

• 5、加载状态和完整密钥寄存器后,AES 密码核心通过将第一轮密钥添加到初始状态来开始加密/解密(绕过两个数据路径中的所有块)。结果被存储回国家登记册。

• 6、然后,AES 密码核心在使用 9/11/13 位密钥时分别执行 128/192/256 轮加密/解密。在每个轮次中,密码数据路径执行以下四个转换。有关更多详细信息,请参阅 AES 规范。如果在 CTR 模式下运行,计数器模块会迭代更新 IV,并行更新执行加密/解密的密码核心。在内部,计数器模块使用一个16位计数器,这意味着它需要8个时钟周期来递增存储在IV寄存器中的128位计数器值。由于计数器值仅在第一轮中使用,并且由于单个块的加密/解密需要 12/14/16 个周期,因此迭代计数器实现不会影响 AES 单元的吞吐量。

• 子字节转换:一种非线性字节替换,使用替换表 (S-Box) 对状态的每个字节独立运行。

• ShiftRows 转换:状态的最后三行的字节在不同的偏移量上循环移动。

• MixColumns 转换:状态的四列中的每一列都被视为 GF(2^8) 上的多项式,并单独乘以另一个固定多项式。

• AddRoundKey Transformation:round键与MixColumns操作的输出进行XOR运算,并存储回状态寄存器。128位整数密钥本身是从Full Key寄存器中的当前值中提取的。同时,使用密钥扩展模块动态计算用于下一轮的完整密钥。

• 7、最后,AES 密码核心执行最后一轮加密/解密,其中跳过混合列操作。输出被转发到CSR中的输出寄存器,但不会存储回状态寄存器。内部状态寄存器使用伪随机数据清除。

根据密码模式,最后一轮的输出可能会与IV寄存器中的值(CBC解密)或存储在先前输入数据寄存器中的值(CFB,OFB,CTR模式)进行异或运算,然后再转发到CSR中的输出寄存器。

如果在CBC模式下运行,IV寄存器将使用输出数据(加密)或存储在先前输入数据寄存器中的值(解密)进行更新。

如果在 CFB 或 OFB 模式下运行,IV 寄存器将分别使用输出数据或最终密码轮的输出(在与先前输入数据进行 XOR 运算之前)进行更新。

具有单独的输入、输出和内部状态寄存器可防止通过 TL-UL 总线接口提取中间状态,并允许将重新配置与操作重叠。当 AES 单元执行加密/解密时,处理器可以安全地将下一个输入数据块写入 CSR 或从 CSR 读取上一个输出数据块。状态寄存器位于 AES 单元内部,不通过 TL-UL 总线接口公开。如果 AES 单元想要完成输出数据块的加密/解密,但处理器尚未读取前一个数据块,则 AES 单元将停止。它挂起并且不会丢弃数据。只有在读取了先前的输出数据并且可以安全地覆盖相应的寄存器后,它才会继续。读取输出寄存器的顺序无关紧要。每个输出寄存器必须至少读取一次,AES单元才能继续。相比之下,初始密钥和控制寄存器只能在AES单元空闲时更新,这简化了设计验证(DV)。同样,初始化向量 (IV) 寄存器只能在 AES 单元空闲时由处理器更新。如果 AES 设备繁忙且以 CBC 或 CTR 模式运行,则 AES 设备本身会更新 IV 寄存器。

AES单元的密码核心架构源自Satoh等人提出的架构:“具有S-Box优化的紧凑型Rijndael硬件架构”[4]。110nm CMOS技术的预期电路面积约为12 - 22 kGE(未屏蔽实现,仅限AES-128)。启用掩蔽的整个AES单元的预期电路面积约为110 kGE。

有关各个子模块的说明,请参阅以下部分。

2、SubBytes / S-Box

SubBytes操作是一种非线性字节替换,使用替换表(S-Box)对状态的每个字节独立操作。它既用于加密数据路径,也用于密钥扩展数据路径。AES单元总共并行实例化20个S盒(16个用于SubBytes,4个用于KeyExpand),每个S盒具有8位输入和输出。结合128位宽的数据路径,这允许每次迭代执行一轮AES。

这种S盒及其反向器的设计会对电路面积、时序关键路径、鲁棒性和功率泄漏产生很大影响,这本身就是其研究的主题。S盒通过握手协议与AES单元的其余部分解耦,允许在需要时用不同的实现方式轻松替换它们。AES单元具有以下S-Box实现,可通过编译时Verilog参数进行选择。

3、ShiftRows

ShiftRows操作简单地执行状态矩阵的第1、2和3行的循环移位。因此,它可以使用3*4个32位2输入多路复用器(加密/解密)来实现。

4、列混合变换

状态的四列中的每一列都被认为是GF(2^8)上的多项式,并分别与另一个固定多项式相乘。整个操作可以使用36个2输入XOR和16个4输入XOR(全部为8位)、8个2输入多路复用器(8位)以及78个2输入和24个3输入XOR门来实现。

5、秘钥扩展

集成在AES单元中的密钥扩展模块(KEM)负责从初始密钥生成各种圆形密钥,用于加密和解密。KEM基于当前完整密钥或初始密钥(用于第一轮加密),与实际加密/解密并行生成下一个128/192/256位完整密钥。然后,从该完整密钥中提取实际的128位循环密钥。

动态生成密钥允许更低的存储要求和更小的电路面积,但代价是每当密钥发生变化时,在进行ECB/CBC解密之前的初始延迟。在此阶段,KEM循环使用所有完整密钥,以获得解密的开始密钥(等于最后一轮加密的密钥)。该延迟阶段的持续时间对应于加密一个16B块所需的等待时间。在这个初始阶段,密码数据路径保持空闲。下面的时序图显示了这一过程。

在这里插入图片描述

6、系统密钥管理器接口

默认情况下,AES单元完全由处理器控制。处理器通过系统总线互连将输入数据和初始密钥写入专用寄存器。

或者,处理器可以将AES单元配置为使用密钥管理器经由密钥侧载接口提供的初始密钥,而不将密钥暴露给处理器或连接到系统总线互连的其他主机。为此,处理器必须将CTRL_SHADOWED中的SIDELOAD位设置为1。然后忽略处理器对初始密钥寄存器Key_SHARE_0-Key_SHARE1_7的任何写入操作。在正常/自动模式下,AES单元仅在侧载密钥标记为有效时才开始加密/解密。

为了更新侧载密钥,处理器必须1)等待AES单元变为空闲,2)等待密钥管理器更新侧载关键字并断言有效信号,以及3)写入CTRL_SHADOWED寄存器以启动新消息。使用侧载密钥后,处理器必须触发清除AES单元内的所有密钥寄存器(请参阅下面的去初始化)。

三、安全强化

AES单元在体系结构、微观体系结构和物理级别上采用不同的手段,以针对侧通道分析和故障注入进行安全加固。

1、侧通道分析

为了加剧侧信道分析(SCA),AES单元实施以下对策。

1-密码核心的一阶掩码

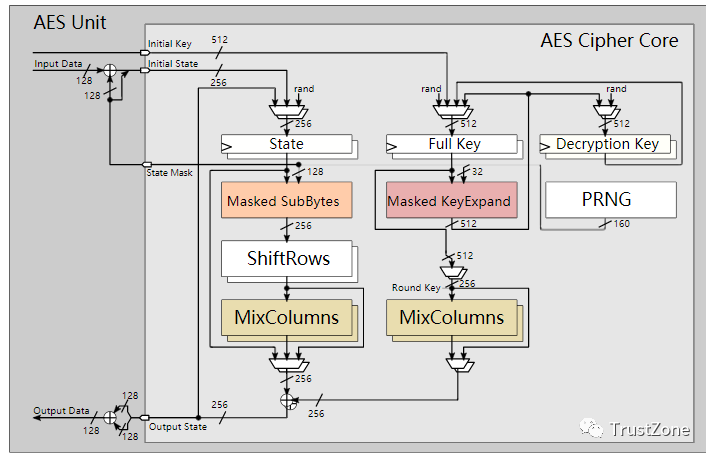

AES单元采用AES密码核心的一阶掩码。更确切地说,密码和密钥扩展数据路径都使用两个共享。如下面的框图所示,所有寄存器和数据路径的宽度基本上都会翻倍。

在这里插入图片描述

初始密钥通过寄存器接口分为两部分提供。输入数据以未屏蔽的形式提供,并在密码核心之外屏蔽,以获得初始状态的两个份额。屏蔽输入数据所需的伪随机数据(PRD)由密码核心的伪随机数生成器(PRNG)提供。类似地,输出状态的两个份额在密码核心之外被组合以获得输出数据。

相同的PRNG还生成屏蔽子字节(16个屏蔽S盒)和屏蔽KeyExpand(4个屏蔽S框)所需的新随机性。为S-Box选择的掩蔽方案可以对SCA电阻、电路面积、每个周期和每个S-Box评估消耗的PRD比特的数量以及吞吐量有很大影响。屏蔽S-Box实现的选择可以通过编译时Verilog参数来控制。

默认情况下,AES单元对Gross等人提出的S盒使用面向域屏蔽(DOM):“面向域屏蔽:具有任意保护顺序的紧凑屏蔽硬件实现”。所提供的实现具有每次S-Box评估5个时钟周期的延迟。结果,在AES-128/192/256模式中,处理16字节数据块的总等待时间分别从12/14/16增加到56/66/72时钟周期。所提供的实现进一步在DOM S-Box实例之间转发部分中间结果,以用于重新屏蔽目的。这允许在不影响SCA电阻的情况下减少与生成、缓冲和应用PRD相关的电路面积。

可替换地,Canright和Batina提出的屏蔽Canright S盒的两个原始版本可以选择:“一个非常紧凑的”完全屏蔽的“AES(校正)S盒”。这两个版本是完全组合的(每个周期一次S盒评估)并且具有较低的占地面积,但它们对SCA的抵抗力明显较低。

它们主要用于参考,但由于Moradi等人描述的相关性增强碰撞攻击的潜在漏洞,不鼓励使用它们:“相关性增强功率分析碰撞攻击”。

每当提供新密钥时(参见CTRL_AUX_SHADOWED.key_TOUCH_FORCES_RESEED),以及2)基于块计数器。此块计数器启动自动重新设定操作的速率可以通过CTRL_SHADOWED.PRNG_reseed_rate进行配置。此外,软件可以通过TRIGGER.PRNG_RESED手动启动重新设定操作。

请注意,可以通过编译时Verilog参数启用/禁用屏蔽。当例如在CSRNG内部使用AES密码核心来生成随机数时,禁用屏蔽是可以接受的。禁用屏蔽时,还需要使用相应的编译时Verilog参数选择未屏蔽的S-Box实现。禁用屏蔽时,建议分别针对ASIC或FPGA目标使用未屏蔽的Canright或LUT S-Box实现。两者都是完全组合的,并且允许每个时钟周期进行一次S盒评估。

值得注意的是,由于输入/输出数据是以未屏蔽的形式通过寄存器接口提供/检索的,因此AES单元不应用于形成身份梯形图,其中一个AES运算的输出用于形成梯形图中下一个AES操作的密钥。在OpenTitan中,Keccak消息验证码(KMAC)单元用于此目的。

2-完全并行数据路径

任何一阶屏蔽方案主要针对一阶SCA进行保护。针对高阶SCA的漏洞可能仍然存在。加剧高阶攻击的一种常见技术是增加系统中的噪声,例如通过利用并行架构。为此,AES密码核心使用128位并行数据路径,总共有20个并行评估的S盒(16个在SubBytes内,4个在KeyExpand内)。

除了增加噪声以提高对高阶SCA的抵抗力外,全并行架构还实现了更高的性能和灵活性。它允许用户无缝切换S-Box实现,以便试验不同的掩蔽方案。为了将数据路径与S-Boxes接口,使用了握手协议。

3-关于重置与非重置触发器的注意事项

选择触发器类型来注册密钥等敏感资产可能会对漏洞产生影响,例如组合重置故障攻击和SCA。根据OpenTitan非重置与重置失败的基本原理,可以进行以下观察:如果启用屏蔽,密钥和状态值将存储在AES单元内的两个共享中。无论是个股的汉明权重还是汉明权重之和都与秘密资产的汉明重量成比例。

输入/输出数据和IV值(目前)没有存储在多个共享中,但这些数据不太重要,因为它们只使用一次。此外,它们被存储在32位的存储体中,与将例如8位寄存器假信号复位时相比,留下了更大的假设空间。此外,当通过TL-UL总线接口传输时,它们也可能被提取。

因此,AES单元仅使用复位触发器。然而,所有主密钥和数据寄存器在复位时都用伪随机数据清除。

4-用伪随机数据清除寄存器

重置后或由软件启动时,AES模块内的所有主密钥和数据寄存器都用伪随机数据(PRD)清除。这有助于在写入这些寄存器进行重新配置时以及在使用后清除寄存器时减少SCA泄漏。此外,在每次加密/解密的最后一轮期间,密码核心内的状态寄存器都用PRD清除。这防止了最后两轮的状态之间以及输出和输入数据之间的汉明距离泄漏。

2、故障注入

故障注入(FI)攻击可以根据FI目标进行区分。

1-控制路径

在加密设备中,控制路径上的故障攻击通常旨在干扰控制流,从而促进SCA或其他攻击。AES的示例目标包括:切换到不太安全的操作模式(ECB),继续处理相同的输入数据,减少轮次/提前终止,跳过特定轮次,跳过轮次中的单个操作。为了防止控制路径上的FI攻击,AES单元执行以下对策。阴影控制寄存器:主控制寄存器实现为阴影寄存器。这意味着软件必须执行两个后续写入操作才能执行更新。在内部,使用一个卷影副本,该副本不断与实际寄存器进行比较。有关更多详细信息,请参阅注册工具文档。

• FSM状态的稀疏编码:AES单元内的所有FSM都使用稀疏状态编码。多路复用器选择器信号的稀疏编码:所有主要多路复用器都使用稀疏编码的选择器信号。

用于握手和其他重要控制信号的稀疏编码。

多轨控制逻辑:AES单元内的所有FSM都使用多个独立和冗余的逻辑轨来实现。每个轨道精确地评估和驱动稀疏编码的握手或其他重要控制信号的一个比特。不断比较不同导轨的输出,以检测潜在故障。逻辑轨道的数量可以通过相对容易的RTL修改来扩大。默认情况下,使用三个独立的逻辑轨道。

强化圆形计数器:与密码核心FSM类似,内部圆形计数器通过多轨实现来防止FI。不断比较不同轨道的输出,以检测圆形计数器中的潜在故障。

如果这些对策中的任何一个检测到故障,就会触发致命警报,内部FSM进入终端错误状态,AES单元不会释放更多数据并锁定,直到重置。由于AES单元没有自我复位的能力,因此在AES单元能够再次运行之前,需要系统提供的复位。

STATUS.ALERT_FATAL_FAULT中报告了这种情况。没有提供检测到故障的详细信息。

2-数据路径

对数据路径进行故障攻击的目的通常是通过统计分析来提取密钥上的信息。AES单元的当前版本没有针对此类攻击采取反措施,但未来版本很可能会采取反措施。

审核编辑:汤梓红

-

AES加密流程2025-10-23 277

-

IN6xx硬件AES介绍橙群微电子 2023-12-04

-

SOC-AES系列广播专业10路AES数字音频光端机2011-03-13 2839

-

转:熟悉AES加密2016-07-09 7222

-

静态DAC技术规格是什么?2019-08-21 2452

-

什么是AES算法? 怎样快速实现AES算法?2021-04-28 2172

-

GPON 中的AES加密2009-12-14 912

-

AES/EBU接口标准2009-08-01 16383

-

AES算法中S-box和列混合单元的优化及FPGA技术实现2010-04-23 3569

-

基于AES算法的加密模块设计2013-02-21 1441

-

LORA6500AES 5w LORA AES加密无线数传模块V2017-09-05 1496

-

AES加密算法说明2017-11-30 2847

-

基于AES算法研究与设计2017-12-03 827

-

AES加密协议是什么?AES加密协议的应用2024-04-15 3509

-

开源物联网技术--AES加密功能技术分享2024-09-11 2254

全部0条评论

快来发表一下你的评论吧 !