芯片制造和封测工艺简述

制造/封装

描述

来源:祺芯半导体

一、硅晶圆制造与切割

晶圆是制作硅半导体IC所用之硅晶片,状似圆形,故称晶圆。材料是「硅」, IC(Integrated Circuit)厂用的硅晶片即为硅晶体,因为整片的硅晶片是单一完整的晶体,故又称为单晶体。但在整体固态晶体内,众多小晶体的方向不相,则为复晶体(或多晶体)。

晶圆是硅元素加以纯化,经过照相制版、研磨、抛光、切片等程序将多晶硅融解拉出单晶硅棒,然后切割成一片片晶圆。

二、光学显影

光学显影是在感光胶上经过曝光和显影的程序,把光罩上的图形转换到感光胶下面的薄膜层或硅晶上。光学显影主要包含了感光胶涂布、烘烤、光罩对准、 曝光和显影等程序。

曝光方式有紫外线、X射线、电子束、极紫外光等。

三、蚀刻技术

蚀刻技术(Etching Technology)是将材料使用化学反应物理撞击作用而移除的技术。可以分为:

湿蚀刻(wet etching):湿蚀刻所使用的是化学溶液,在经过化学反应之后达到蚀刻的目的。

干蚀刻(dry etching):干蚀刻则是利用一种电浆蚀刻(plasma etching)。电浆蚀刻中蚀刻的作用,可能是电浆中离子撞击晶片表面所产生的物理作用,或者是电浆中活性自由基(Radical)与晶片表面原子间的化学反应,甚至也可能是以上两者的复合作用。

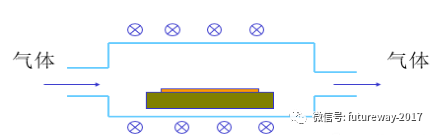

四、CVD化学气相沉积

这是利用热能、电浆放电或紫外光照射等化学反应的方式,在反应器内将反应物(通常为气体)生成固态的生成物,并在晶片表面沉积形成稳定固态薄膜(film)的一种沉积技术。CVD技术是半导体IC制程中运用极为广泛的薄膜形成方法,如介电材料(dielectrics)、导体或半导体等薄膜材料几乎都能用CVD技术完成。

常用的CVD技术有:

(1)常压化学气相沉积(APCVD);

(2)低压化学气相沉积(LPCVD);

(3)电浆辅助化学气相沉积(PECVD)

较为常见的CVD薄膜包括有:

二气化硅(通常直接称为氧化层)

氮化硅

多晶硅

耐火金属与这类金属之其硅化物

CVD的反应机制主要可分为五个步骤:

(1)在沉积室中导入气体,并混以稀释用的惰性气体构成「主气流(mainstream)」;

(2)主气流中反应气体原子或分子通过边界层到达基板表面;

(3)反应气体原子被「吸附(adsorbed)」在基板上;

(4)吸附原子(adatoms)在基板表面移动,并且产生化学反应;

(5)气态生成物被「吸解(desorbed)」,往外扩散通过边界层进入主气流中,并由沉积室中被去除。

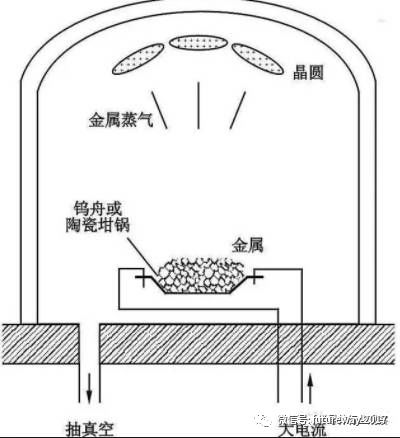

五、物理气相沉积(PVD)

这主要是一种物理制程而非化学制程。此技术一般使用氩等钝气,藉由在高真空中将氩离子加速以撞击溅镀靶材后,可将靶材原子一个个溅击出来,并使被溅击出来的材质(通常为铝、钛或其合金)如雪片般沉积在晶圆表面。

PVD以真空、测射、离子化或离子束等方法使纯金属挥发,与碳化氢、氮气等气体作用,加热至400~600℃(约1~3小时)后,蒸镀碳化物、氮化物、氧化物及硼化物等1~10μm厚之微细粒状薄膜。

PVD可分为三种技术:

(1)蒸镀(Evaporation);

(2)分子束磊晶成长(Molecular Beam Epitaxy;MBE);

(3)溅镀(Sputter)

解离金属电浆是最近发展出来的物理气相沉积技术,它是在目标区与晶圆之间,利用电浆,针对从目标区溅击出来的金属原子,在其到达晶圆之前,加以离子化。离子化这些金属原子的目的是,让这些原子带有电价,进而使其行进方向受到控制,让这些原子得以垂直的方向往晶圆行进,就像电浆蚀刻及化学气相沉积制程。这样做可以让这些金属原子针对极窄、极深的结构进行沟填,以形成极均匀的表层,尤其是在最底层的部份。

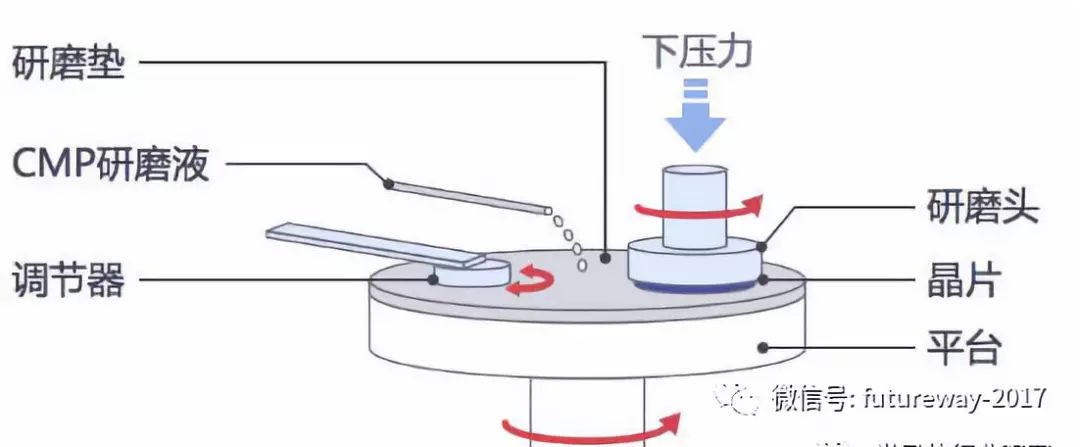

六、化学机械研磨技术

化学机械研磨技术(化学机器磨光, CMP)兼具有研磨性物质的机械式研磨与酸碱溶液的化学式研磨两种作用,可以使晶圆表面达到全面性的平坦化,以利后续薄膜沉积之进行。

在CMP制程的硬设备中,研磨头被用来将晶圆压在研磨垫上并带动晶圆旋转,至于研磨垫则以相反的方向旋转。在进行研磨时,由研磨颗粒所构成的研浆会被置于晶圆与研磨垫间。影响CMP制程的变量包括有:研磨头所施的压力与晶圆的平坦度、晶圆与研磨垫的旋转速度、研浆与研磨颗粒的化学成份、温度、以及研磨垫的材质与磨损性等等。

七、光罩检测

光罩是高精密度的石英平板,是用来制作晶圆上电子电路图像,以利集成电路的制作。光罩必须是完美无缺,才能呈现完整的电路图像,否则不完整的图像会被复制到晶圆上。光罩检测机台则是结合影像扫描技术与先进的影像处理技术,捕捉图像上的缺失。

当晶圆从一个制程往下个制程进行时,图案晶圆检测系统可用来检测出晶圆上是否有瑕疵包括有微尘粒子、断线、短路、以及其它各式各样的问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。

一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。

八、清洗

清洗的目的是去除金属杂质、有机物污染、微尘与自然氧化物;降低表面粗糙度;因此几乎所有制程之前或后都需要清洗。

九、晶片切割(Die Saw)

晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die)切割分离。首先必须进行晶圆黏片,在晶圆上贴一层胶带,然后送至晶片切割机上进行切割。切割完后之晶粒井然有序排列于胶带上,而框架的支撑避免了胶带的皱摺与晶粒之相互碰撞。

十:焊线(Wire Bond)

将集成电路内部的线路引出,并向外拉出引线,称之为打线,作为与外界电路板连接之用。

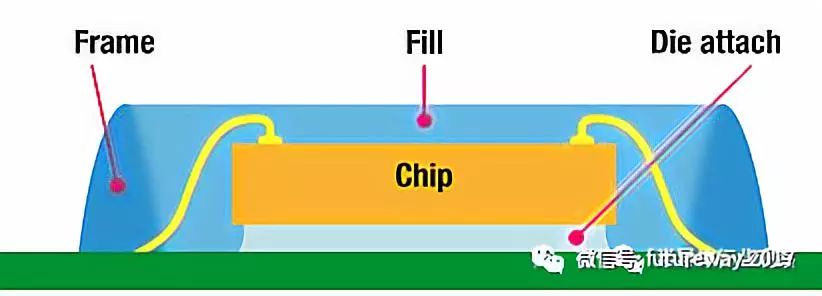

十一、封胶(Mold)

封胶之主要目的为防止湿气由外部侵入、以机械方式支 持导线、内部产生热量之去除及便于手持。其过程为将导线架置于框架上并预热,再将框架置于压模机上的构装模上,再以树脂充填并待硬化。

十二、剪切/成形(Trim /Form)

剪切之目的为将导线架上构装完成之晶粒独立分开,并把不需要的连接用材料及部份凸出之树脂切除(dejunk)。成形之目的则是将外引脚压成各种预先设计好之形状,以便于装置于电路版上使用。

十三:芯片测试和检验过程

这些测试和检验就是保证封装好芯片的质量,保证其良率的。

审核编辑:汤梓红

-

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺2024-12-30 3375

-

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测2025-04-15 1792

-

板上芯片封装的焊接方法及工艺流程简述2012-08-20 2789

-

霍尔IC芯片的制造工艺介绍2016-10-26 6744

-

芯片封测什么意思2020-04-10 12757

-

芯片制造全工艺流程解析2020-12-28 19168

-

想问一下pcb的工艺,是属于在晶圆厂做的工艺还是封测厂呀2021-10-14 5432

-

PCB制造工艺简述2009-05-16 864

-

PCB 制造工艺简述2016-06-15 950

-

简述晶圆制造工艺流程和原理2019-08-12 48556

-

什么是芯片封测技术 芯片设计制造封装测试全流程2023-08-23 8001

-

ic封装测试是做什么?ic封测是什么意思?芯片封测是什么?2023-08-24 8386

-

PCB 制造工艺简述.zip2022-12-30 532

-

芯片封测揭秘:核心量产工艺全解析2024-10-15 4118

-

芯片封测架构和芯片封测流程2024-12-31 3974

全部0条评论

快来发表一下你的评论吧 !