高速PCB叠层设计注意事项

PCB设计

描述

只有使用正确的PCB叠层进行构建,高速设计才能成功运行。您的叠层必须正确布置电源和接地层,为信号分配足够的层,并且所有材料组和铜选择均能以适当的规模和成本制造。如果设计人员能够获得正确的叠层,那么在确保信号完整性的情况下布线就会容易得多,并且可以抑制或防止许多更简单的EMI问题。

为了帮助设计人员更快地设计和构建支持所需布线和信号完整性的高速叠层,我们为不同类别的高速叠层编译了重要资源。

低层数叠层

更简单的高速PCB将从4层电路板开始。我坚定认为,2层电路板不应该用于支持阻抗控制的高速数字接口的设计,因为其无法保证信号完整性或噪声控制。任何设计专业人士均认同这一点。

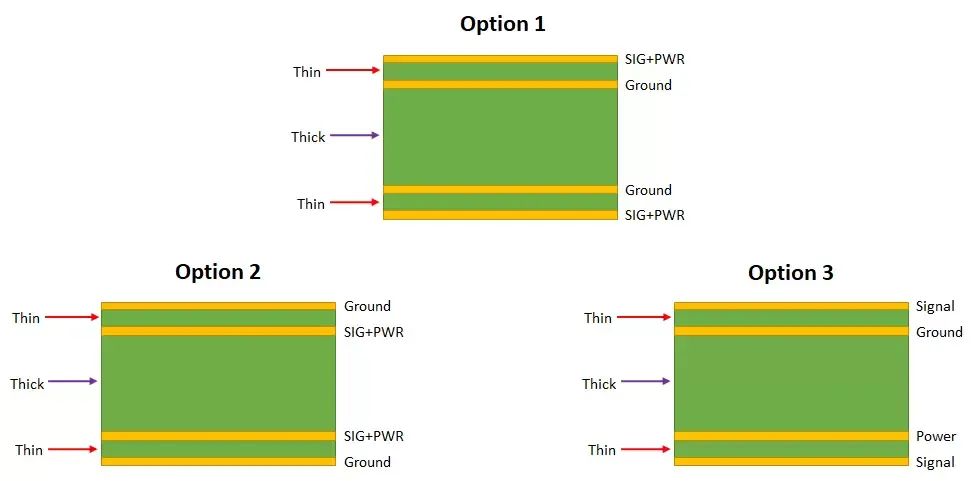

可以支持高速信号的三种主要类型的4层PCB叠层如下所示。在这些叠层中,选项1可以说是最佳选择,因为它提供了最大的布线灵活性,并且可以用作双面电路板。选项2也可用于双面放置,但它限制了信号的布线位置,因为内层可能存在串扰。选项3适用于有高功率需求,但只能在一层上布线高速信号;被动元件或机械元件仍可以放置在背面层上。

详细了解双面PCB的最佳4层叠层选项

可支持高速布线的4层PCB叠层示例

如果需要将低速信号放入内层等更高的信号数,则下一步是将选项1扩展到更高的层数。这将从一个6层叠层开始,其中一个专用电源层和一个信号层被添加到上面选项1所示的叠层中。此叠层之所以有用,有两个原因:

表层适用于受控阻抗高速接口

内层可以支持大多数较慢的接口或控制信号

电源层可以分成多个大电源轨以支持不同的核心电压电平

可以使用相同的步骤将叠层扩展到具有高速信号的8层或更多层;下一节将讨论这种类型的PCB叠层。

详细了解可支持高速PCB的6层PCB叠层

适中层数

在某些时候,电路板叠层会变得非常厚,以至于PCB的总厚度会大于标准值。就制造方面而言,这不是问题;标准层压过程可以处理超出标准厚度值并达到数毫米厚度的板。如果您的目标是薄板,那么您将需要更薄的层;选项是增强型PTFE层压板(将在下文讨论)或直接转向HDI过程。

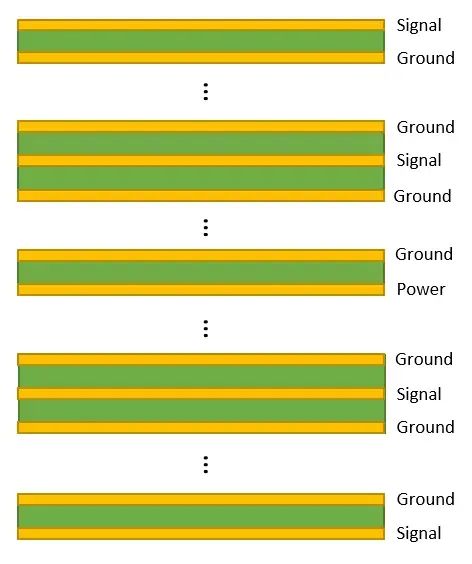

适中层数的电路板(约8层以上)往往会将多个平面层分配给电源,并具有额外的信号层。对于适中层数的电路板,很少会有简单的指南可以帮助抑制EMI并确保电源完整性:

只要信号不参考该平面层,就可以将电源层分成多个轨道

如果有多个电源平面,不要将电源平面堆叠在相邻的层上,而是用一个GND层将其分开

将快速信号放在两个GND平面之间的内层上,不要将其参考有任何拆分的电源平面

仅将表层用于快速微带线,可以使用一些电源布线(如有需要),也可以使用一些GND灌注(如有需要)

这些指南可能会导致您在设计中添加几个额外的层,但优势是噪声控制、电源完整性和信号完整性要好得多。

将层分组到更高层数的策略

更多高级叠层

在高速PCB设计的背景下,“更先进”的想法可能意味着很多事情。在高速数字设计中,它在层选择和排列方面可能有两种可能的含义:

支持HDI布线的薄层

层数过高会迫使使用薄层

在多层的细间距BGA中进行布线(但不一定要用HDI)

换句话说,您可以拥有非常薄的信号层(例如4密耳)和低层数的玻璃增强型FR4,或者您可以拥有非常高的层数,从而迫使采用薄层和可能的替代材料。

这些PCB高速叠层设计的考量重点是元件所需的线宽和可制造性,而不仅仅是叠层的Dk和Df值。在某些情况下,信号层需要使用低Dk、低Df的层压板,但并不只是因为损耗较低。在这些设计中,可制造性和信号完整性至高无上,薄层压板可以解决具有高层数和/或薄信号层的高速叠层中的许多挑战。如今,较薄电路板的主要选择是增强型PTFE层压板,其厚度可低于4密耳,从而无需转向最先进的工艺或HDI过程。

其他资源

对高速PCB而言,叠层设计的其他重要领域是电源完整性和信号完整性。在BGA封装具有细间距并且层变得非常薄时,也有可能需要转向HDI设计。查看以下资源,详细了解PCB设计的这些重要领域:

您需要了解的11种HDI材料

适用于HDI电路板的2+N+2 PCB叠层设计

电子书:PDN仿真和分析指南

叠层设计对信号完整性的影响

如果您需要指定材料、构建叠层和进行阻抗计算以支持高速PCB,请确保使用Altium Designer中的全套PCB设计工具。当设计完成并准备将文件递交给制造商时,Altium 365平台可以轻松地协作并共享您的项目。

审核编辑:汤梓红

-

FPGA的高速接口应用注意事项2024-05-27 3160

-

高速PCB设计的叠层问题.zip2022-12-30 767

-

PCB线路板叠层设计的注意事项2022-12-08 1797

-

【资料】PCB的EMC设计之常见的PCB叠层结构2021-03-29 2794

-

六层pcb layout层叠结构设计中的注意事项介绍2019-06-03 3059

-

PCB设计中叠层算阻抗时需注意哪些事项?2019-05-16 3687

-

总结了PCB设计叠层算阻抗的4大注意事项 帮助提高计算效率2018-01-22 6693

-

48V电源的PCB设计注意事项2017-07-06 5373

-

设计高速电路板的注意事项2017-01-28 1234

-

pcb注意事项2016-07-29 1187

-

PCB地线设计注意事项2016-07-26 1370

-

高速电路中过孔设计注意事项2009-08-16 20577

-

高速PCB设计的叠层问题2009-05-16 867

全部0条评论

快来发表一下你的评论吧 !