短波电台无线数据传输网络的组建

广播电台

描述

无线电短波是指波长为10~100 m的电磁波,其频率为3~30 MHz。利用短波信道进行数据通信,具有传输距离远、受地形限制较小、不易遭受人为破坏等优点,有着广阔的应用前景。文章在对短波信道的特性进行分析的基础上,通过对短波通信的主要工具短波电台进行改进,提出了一种方案,用于组建一个一点对多点的星型拓扑结构无线网络,进行远距离数据传输,并根据此方案设计了基于DSP芯片的系统软、硬件。通过实验测试,该系统实现了组网的功能。

1 组网方案

在设计组网方案时需要对短波电台进行改进,为了不影响电台原有的内部硬件结构和功能,本文方案设计了与短波电台的音频输入输出口相接口的硬件,在发送端先对数字信号做音频调制,再由电台进行二次调制到短波频段上发送,在接收端经过短波解调和音频解调得到数字信号。这种改进方法适用于大多数具有语音通信功能的电台,易于移植,具有良好的经济性和通用性。

采用了时分多址(TDMA)的方式,在某一时刻只有一个用户发送信号,以获得较好的信噪比性能。在短波通信中产生的多径时延,限制通报的码元速率一般在200 b/s以下,本方案设置码元速率为100 b/s。

选择多进制频率键控(MFSK)的音频调制方式,这种方式适合于在缺乏相位稳定性的信道及衰落信道上进行数据传输,而且充分利用了传输带宽,提高了传输速率。在接收端使用非相干解调和平方率检波的方法对MFSK信号进行解调[1],这种方法不需要估计载波的相位,大大降低了系统的复杂度。

发送端在发送MFSK信号之前插入时域位同步导频,用来帮助接收端获取抽样判决的位同步信息。本方案利用了m序列的自相关函数近似于冲击函数的特性,使用与码元等周期的m序列音频调制信号作为位同步导频。接收端在进行导频检测时,先对采样得到的信号进行顺序移位,再与本地序列做相关,在一个码元周期内,找到最大的相关结果与对应的时刻,认为此时刻为码元结束的时刻,并由此获得位同步信息。

2 系统硬件设计

2.1 系统硬件总体结构

系统硬件以DSP芯片为核心,对信号主要进行数字处理,把固定的硬件结构和灵活的软件算法相结合,只通过修改软件就可以实现方案的改进和系统的升级,灵活简单、方便易行。系统使用TI公司生产的DSP芯片TMS320VC5402(简称C5402),是一款低功耗、高性价比的16 b字长定点DSP芯片,运算速率可达100MI/s,具有高度灵活的可操作性和高速的处理能力,在实时嵌入语音通信等方面得到了广泛的应用。

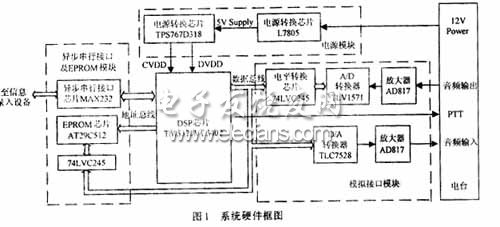

系统硬件结构如图1所示。主要包括4个模块:DSP模块、电源模块、模拟接口模块和异步串行接口及EPROM模块。DSP模块用来完成数字信号处理算法;电源模块利用了电台提供的12 V直流电压,经过两级电源转换,产生稳定的3.3 V和1.8 V的电压输出,分别提供给C5402作为I/O电源和内核电源,同 时5 V的直流电压也给电路板上的其他芯片供电;模拟接口模块和电台音频口连接,用来采样音频输出信号和产生音频模拟输入信号,控制电台音频输入输出转换键控信号PTT;异步串行接口及EPROM模块完成与信息录入设备通信,以及保存程序代码并在复位时自行加载。

2.2 模拟接口模块设计

系统硬件采用了10 b并行A/D转换器TLV1571,该芯片的采样率最高可达1.25 MS/s,功耗极低,具有2个软件可配置的控制寄存器,由触发信号控制所有的采样、转换和数据输出,接口和控制简单,采用了双路8 b并行D/A转换器TLC7528,该芯片设计成具有单独的片内数据锁存器,VDD=5 V时的建立时间为100 ns,传输延时为80 ns,并且可用工作位电压方式,数据锁存与数模转换同样由触发信号完全控制。他们与C5402的连接如图2所示。

该模块通过地址译码把TLV1571和TLC7528分别映射到I/O空间的0x0002和0x0001,保证在C5402访问数据总线时只有一个芯片处于选通状态。在程序开始时要对TLV1571的工作方式进行初始化,通过写入控制字0x00C0和0x0100,把他配置成使用内部时钟、软件启动采样、二进制输出的模式[2]。C5402将串口引脚FSX0设置为通用输出引脚,控制TLV1571的读信号。在每次定时中断中产生相应的触发信号启动D/A和A/D转换,通过改变定时中断的频率就可以灵活地更改采样率和D/A转换频率。

2.3 异步串行接口及EPROM模块设计

异步串行接口及EPROM模块与C5402的连接如图3所示。

本方案利用了C5402的缓冲串口McBSP0的2个引脚:BDR0和BDX0作为通用的输入和输出引脚,用来模拟异步串口,采用 MAX232芯片将C5402输出的TTL电平转换为符合RC232标准的电平,可以与遵循该标准的器件进行通信。EPROM芯片采用了 AT29C512,其存储容量为64 k×8 b,用来存储程序代码和完成自举加载。

3 系统软件设计

3.1 系统软件总体流程

程序开始时,先要进行初始化,对一些初始值和硬件状态进行设置,之后就进入数据收发的进程中。接收中心首先发送一个“查询”信号,开始一次数据接收,并为整个通信网提供定时的基准。用户检测到“查询”信号后,如果有数据需要发送,则在属于自己的时间段内发送数据。接收中心以一定的时间间隔不断发送“查询”信号,由此实现双向的数据传输。软件流程分别如图4和图5所示。

3.2 信号检测算法流程

设采样率为f样本/s,码元速率为Rb/s,则对每个码元采样得到的点数为:N=f/R。在DSP的RAM中设置一个滑窗,其长度为N,用来保存采样结果,每次采样后用新样本覆盖滑窗中最老的样本,实现数据的更新。在RAM中预先保存了对导频信号进行数字化得到的N点的本地导频序列,以及对MFSK信号进行数字化得到的N×M的本地MFSK序列,并开辟N 点的缓冲区用来保存做导频检测时的相关结果。信号检测算法的流程如图6所示。

4 实验测试结果

作者根据组网方案和设计的软、硬件,使用解放军某工厂生产的边海防短波电台组建了一个包含3个用户,1个接收中心的星型网络,并在此网络上测试组网方案。

实验设定波特率为100 Baud,采用4FSK信号调制方式,比特率达200 b/s;选择m序列的长度为15,在每段数据信号之前,插入20个周期的位同步导频。在接收端为了防止对于同步导频的漏检和虚警,采取连续检测到8个周期的导频信号后,开始对接收信号进行非相干解调的方法,并根据平方率检测器输出的平方和结果的值的大小,判断数据信号是否已经起始。根据用户数据长度,每个用户分配给1 s的定时时间,实现多用户的组网。

测试结果表明,所组建的短波电台无线数传网络,可以准确地完成信息的发送和接收,实现了组网的功能。

5 结 语

使用短波电台组建无线数传网络是一项具有现实意义的工作。本文从短波信道和短波电台的特性出发,提出了一种采用时分多址(TDMA),时分双工(TDD),多进制频率键控(MFSK)的组网方案,并根据该方案设计了基于DSP芯片的系统软、硬件,实验证明该系统完成了组网的功能。本方案已经在解放军某部组建的预警信息网络中得到了应用。

-

【OK210申请】无线数据传输模块设计2015-07-24 1875

-

无线数据传输模块的实际应用2019-06-18 4146

-

无线数据传输是什么?2019-10-22 2064

-

如何搭建无线数据传输系统?2021-03-09 1828

-

基于opnet的数据传输网络的实现2010-08-11 720

-

基于ARM的无线数据传输系统设计2010-10-27 577

-

蓝牙网络数据传输分析2008-12-16 3699

-

数据传输速率是什么意思2010-03-18 5296

-

基于无线数据传输与CDMA的远程测控网络2011-09-09 1114

-

nRF905的无线数据传输系统2015-11-06 950

-

WNS无线数据传输模块2017-09-25 1079

-

如何实现CC2500无线数据传输?(1)2018-08-10 9477

-

纵横智控无线数传电台——点对点/点对多点数据传输2020-02-17 8009

-

无线数据传输模块的功能特点2021-07-20 2349

-

网络数据传输速率的单位是什么2024-10-12 10470

全部0条评论

快来发表一下你的评论吧 !