Xilinx 7系列FPGA Multiboot介绍

可编程逻辑

描述

在远程更新的时候,有时候需要双镜像来保护设计的稳定性。在进行更新设计的时候,只更新一个镜像,另一个镜像在部署之前就测试过没问题并不再更新。当更新出错时,通过不被更新的镜像进行一些操作,可以将更新失败的数据重新写入Flash。这样即使更新出错,也能保证设计至少可以被远程恢复。

Xilinx的双镜像方案成为Multiboot。本文对Xilinx 7系列的Multiboot做一些简单介绍。

Multiboot直接操作的是两个镜像,但实际上可以用于多个镜像。为了便于描述,Multiboot中的两个镜像分别成为G镜像(Golden)和M镜像(Multiboot)。

远程更新的方案,有一些是通过FPGA来读写Flash的,例如Xilinx平台下需要自己实现的Flash读写控制器,Altera平台下的ASML IP。当无法提供JTAG等其他连接时,Flash的更新就只有FPGA一种方案。

当写入Flash的操作出现错误,或者Flash中部分地址中的数据出现错误,导致无法正确写入或者存储的数据出现错误,这样会导致FPGA无法加载成功。

当FPGA无法加载成功或者工作不正常的时候,Flash的读写操作也就无法得到保证。此时也就不能重新通过远程更新方案来重新读写Flash,纠正之前的错误。所以可以看到,如果Flash直接由FPGA控制,当远程更新出现错误时,很可能导致远程更新彻底失效,只能安排现场更新来修复。

对应方案就是使用双镜像(多镜像),更新的时候只更新M镜像,更新后直接使用M镜像。当出现M镜像更新出现错误的时候,则启动G镜像。通过G镜像中的设计来重新更新Flash中M镜像部分的数据。

由于G镜像从来没有被更新过,这样出现错误的概率也就非常小。这样即使M镜像出现错误,可以通过G镜像来完成一些工作(例如Flash读写操作),由此来保证设计一直可以使用。

从这个分析可以看出,双镜像的方案,需要完成两个任务。

1.正常情况下,加载完成时应该是M镜像在运行

2.出现错误的时候,需要返回G镜像

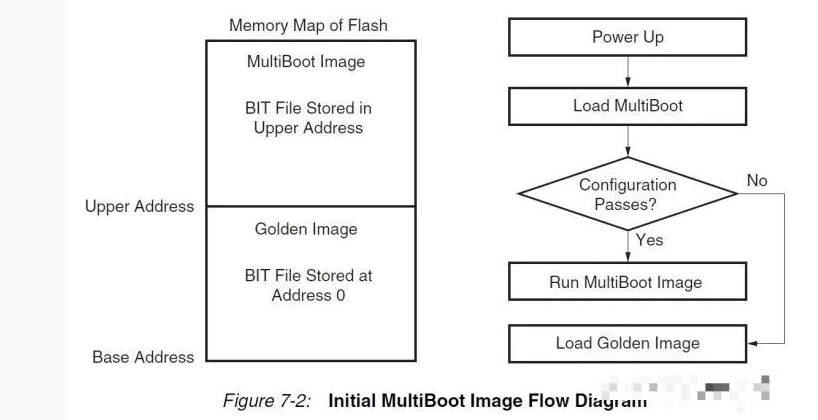

图片来自UG470

从上图可以看到,Xilinx 7系列FPGA的Multiboot方案是从基地址开始存放G镜像,后续存放M镜像。加载过程中是先加载M镜像,配置完成后如果成功,则运行M镜像;如果运行失败,则重新加载G镜像。

下面就从需要完成的两个任务,结合上图来进行介绍。

先看第一个任务,加载M镜像。

上电完成之后,FPGA就会按照设置,进行加载操作。在主动模式下,FPGA会开始对Flash的操作,尝试读取Flash中存储的配置镜像数据。需要注意的是,主动模式下的这一系列操作都是FPGA自动完成的,用户无法控制。

所以就出现了第一个问题。既然读取操作是自动的,那么FPGA是如何知道M镜像存储在哪里,并先加载M镜像呢?如果是从0地址开始读取,那么应该先完成G镜像的加载。否则,是否使用Multiboot及M镜像的地址,是如何传递给FPGA、让FPGA知晓呢?

Xilinx的Multiboot方案中的解决办法是使用一条加载命令:IPROG。而这条命令,是放在G镜像中。

具体说,对于FPGA直接从0地址开始读取,先开始加载G镜像,但是这个G镜像是经过特别处理的,在镜像数据刚开始的部分添加了IPROG命令和M镜像的地址。当FPGA读取到这个命令之后,就会直接跳过后面的数据,从设置的地址开始继续加载。这样的操作,导致G镜像只是运行了最前面的几条加载命令,而M镜像也只是等了几条命令的操作就开始加载了,保证了M镜像的直接加载。

需要说明的是IPROG这是一条命令,所以既可以在G镜像中生效,也可以在设计中任意使用。用户可以将IPROG命令发给ICAP,来实现任意时间触发重新加载的需求。通过设置合适的地址,可以实现多个镜像的切换。

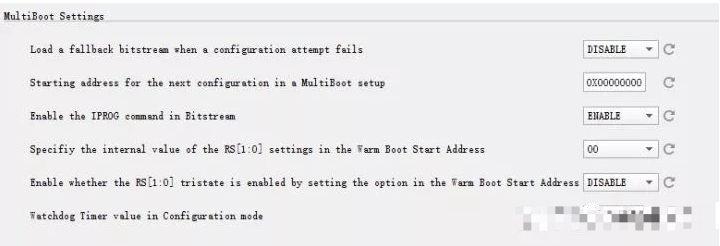

图片截取自Vivado

从vivado中的设置可以看出,Multiboot的主要设置只有这6个。第一个成为Fallback,最后一个成为Watchdog。这两个下文会做介绍。第四个第五个是关于RS pin。等熟悉Multiboot理解之后可以查看文档进行理解,本文不做深入介绍。

第二个是设置跳转到的地址、第三个是在G镜像中加入IPROG命令。这两个操作可以以命令的形式发给ICAP接口,从而触发Multiboot中转跳并加载新的镜像数据。

看完上述的分析,应该明白如何实现先加载M镜像这个需求了。下一步就是,在加载失败时如何回退到G镜像。

M镜像加载不成功,需要回退到G镜像的操作,Multiboot方案称这一步骤为Fallback。

Fallback在四种条件下会被触发:

1. ID Code错误

2. CRC错误

3. Watchdog超时

4. BPI地址越界

ID Code错误是指配置文件中的器件型号和当前器件不匹配。CRC校验是指配置数据送入FPGA之后会进行校验,如果数据不一样则会提示CRC错误。这两个基本原理比较容易理解,至于具体细节,需要能解析bit文件的内容之后才能充分理解。

Watchdog超时是指在规定的时间内如果无法配置成功,则触发Watchdog超时,进而会导致Fallback。

BPI地址越界是指发现逐步增长的BPI地址超过最大值,发生溢出,回到0,则除法Fallback。

大概理解一下四个条件之后可以看到,BPI是只针对BPI模式的,和Watchdog有一点类似,都是在一段时间内如果没有加载成功,地址会逐步增加,计时器会逐步增加,超过范围后就触发Fallback,所以BPI就不做进一步解释了。

ID Code也不做进一步解释了,因为ID Code不对,大概率是用错镜像文件了。所以也没有太多可以分析的。

重点是2和3,当存在Multiboot镜像的时候,如M镜像的内容出现问题,则会触发CRC校验错误,这样可以保证镜像加载成功之后,数据是没有问题的。

但是如果没有Multiboot镜像,则CRC校验无法进行,或者加载到一半就挂死了。这个时候就需要Watchdog来触发Fallback。只要一定时间内加载没有完成,就一定会触发Watchdog超时。

所以CRC是用来保证加载正确的,Watchdog是用来保证一定会提示加载失败的。

注意,Watchdogd的计时设置,请设置好然后实际测试一下,而不要仅仅凭经验/文档来推断一个合适的值。

当发生了Fallback之后,工程会反跳回0地址开始加载,从新加载G镜像。这里,FPGA内部的配置寄存器会做记录,当发生Fallback之后,会自动忽略IPROG命令,直接加载G镜像后续的部分,来保证G镜像有机会被完整的加载。

FPGA自带一些寄存器,记录了FPGA加载时的一些状态,通常称为device status寄存器。当初出现加载失败的问题时,可以通过JTAG查看相关寄存器来寻找一些线索,帮助定位问题。

通过这一系列复杂的操作,可以实现双镜像的配置切换。这种方法最大的优点就是速度快。在配置完成之后可以快速的跳转、加载和返回。最关键的双镜像选择这一步是在加载初期就进行转跳,所以跳转非常迅速,适合一些对配置时间有要求的场合。缺点就是原理和设置都相对麻烦了一些。

和上述方法不一样的一个双镜像切换的方法就是用户自行做切换。大致原理是用户利用FPGA的可编程逻辑资源对ICAP模块进行控制,输入需要跳转的地址然后输入IPROG命令,来触发跳转操作。这个操作是需要先加载好G镜像并开始运行,然后由用户来控制什么时候进行跳转。

这样操作的优点有:

1.跳转地址由用户自行选择,所以可以在多个镜像中跳转,而不限于两个;

2.可以选择在合适的时间进行加载,用户选择性更大。

主要缺点:

1.需要对配置过程、ICAP端口和控制命令有更多的理解

2.需要加载完至少一个镜像才能使用,所以对配置时间要求高的场景无法使用

如果仅仅是为了远程更新,那么这个方案,并不合适。用自动的双镜像方案更简单易用一些。只要G镜像调试完毕,整个方案对M镜像的要求比较低。

审核编辑:汤梓红

-

multiboot什么意思 MultiBoot的功能简介、流程介绍2021-08-04 21034

-

AMD Xilinx 7系列FPGA的Multiboot多bit配置2024-02-25 2787

-

7 series FPGAs SPI MultiBoot应用笔记2019-04-05 4273

-

Xilinx-Spartan6 FPGA实现MultiBoot2012-03-22 1044

-

xilinx公司的7系列FPGA应用指南2012-08-07 2343

-

关于Xilinx公司出品的Spartan6系列FPGA的MultiBoot设计方案详解2018-07-13 11247

-

7 eries FPGAs SPI MultiBoot实现方式2020-12-11 2601

-

Xilinx 7系列FPGA介绍2020-11-13 16931

-

Xilinx 7 系列FPGA中的Serdes总结2020-12-31 1890

-

Xilinx 7系列FPGA简介--选型参考2021-01-30 3073

-

深入探究Xilinx Multiboot实例2021-09-26 5230

-

Xilinx 7系列与Ultrascale系列FPGA的区别2023-09-15 9404

-

简述Xilinx 7系列FPGA芯片相关知识2023-11-28 3212

-

Xilinx 7系列FPGA功能特性介绍2024-04-22 9576

-

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性2024-11-05 5215

全部0条评论

快来发表一下你的评论吧 !