基于FPGA开发板的OV7670 驱动设计

可编程逻辑

描述

本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。

OV7670 驱动设计

本篇实现基于叁芯智能科技的SANXIN -B01 FPGA开发板

OV7725和OV7670都是豪威系列摄像头,工作原理和接口类似。在此以OV7670为主来介绍。

OV7670是一个种图像传感器(摄像头),感光阵列为640x480(可以采集宽度为640,高度为480的图像)。

在摄像头的接口中,有3.3V和GND的电源接口,正确连接电源即可。

在一些摄像头中,pwdn管脚和rst管脚有时会直接省略掉。pwdn管脚为电源掉电模式管脚,低电平表示为正常模式,高电平表示掉电模式。使用时,将pwdn管脚置为低电平即可。rst管脚为复位管脚,低电平为复位状态,高电平为正常工作状态。使用时,可以拉低一段时间(10ms),然后一直拉高即可(拉高后的1ms之内,不能够进行其他操作)。

摄像头中,xclk为摄像头的主时钟信号,由FPGA提供,时钟速率选择24MHz即可。

在摄像头正常工作之前,还需要通过SCCB协议配置摄像头内部的多个寄存器,来达到我们想要的功能。SCCB协议与IIC协议几乎完全相同,直接应用即可。配置速率选择为100KHz。配置的寄存器较多,可以参考摄像头的手册。配置管脚为SCL和SDA。

在配置寄存器结束后,摄像头有一段的适应时间,该时间为15帧图像。

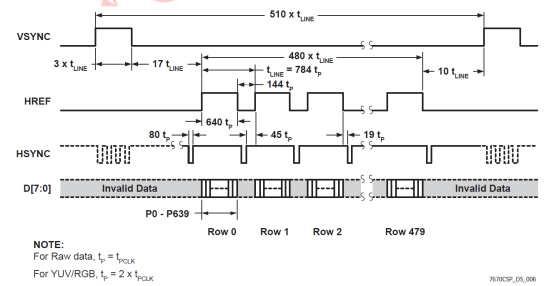

在图像可以正常输出时,摄像头按照以下时序进行输出。

输出时,VSYNC为帧同步脉冲,HREF为行数据有效标志,D为摄像头输出像素点信号。

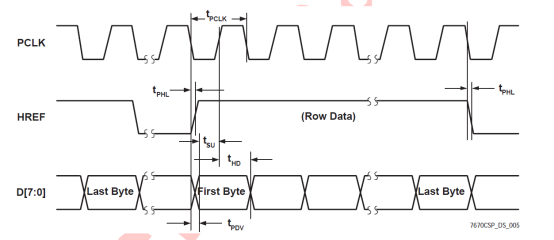

pclk为摄像头输出像素点数据的时钟,FPGA在pclk的上升沿沿采样即可。

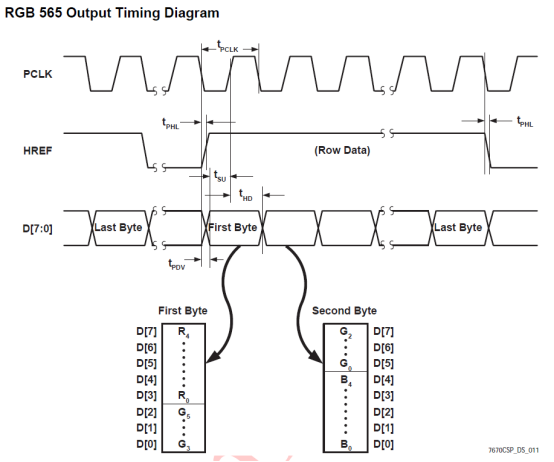

当选择摄像头输出像素点模式为RGB565时,输出两个数据为一个像素点数据,格式为上图所示。

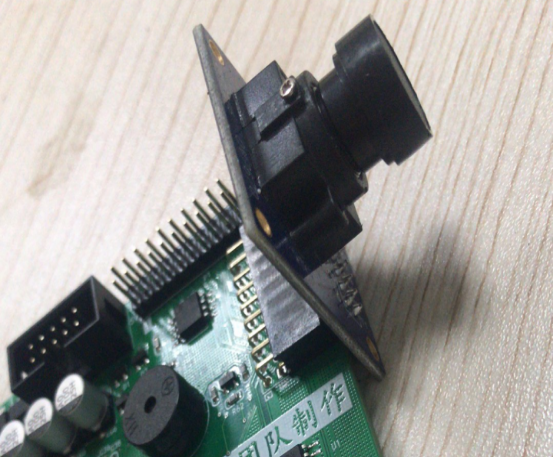

摄像头通过开发板上的18pin的弯头插针与开发板相连接。

具体的设计参考图像显示系统设计所对应的设计代码。

编辑:黄飞

-

OV7670的驱动程序和模块经典资料合集免费下载2019-08-15 2421

-

OV7670新手求助2013-03-24 3743

-

基于野火stm32 V3开发板驱动OV7670摄像头实验2014-01-08 19461

-

【STM32F103试用申请】精英STM32F103开发板+OV7670网络相机开发2018-09-14 2899

-

【工程源码】基于FPGA的OV5640/OV7670的IIC接口初始化Verilog代码2020-02-14 2235

-

请问STM32如何驱动OV7670?2021-11-25 3953

-

OV7670 FIFO 30W摄像头的相关资料推荐2022-01-06 2828

-

FPGA零基础学习:OV7670 驱动设计2023-03-28 824

-

OV7670模块(资料总包)2016-01-19 1764

-

OV7670使用说明和程序讲解-参考精英板2016-05-13 2070

-

ov7670电路原理图2016-05-20 1645

-

一文看懂ov7620与ov7670的区别2018-03-01 53147

-

OV7670模块的详细资料合集免费下载2019-04-11 2427

-

使用STM32单片机驱动OV7670进行图像的采集的程序和工程文件免费下载2019-08-07 2118

-

基于stm32控制OV7670摄像头2021-05-26 3797

全部0条评论

快来发表一下你的评论吧 !