功率器件终端区设计的必要性及注意事项有哪些?

模拟技术

描述

01

终端区设计的必要性

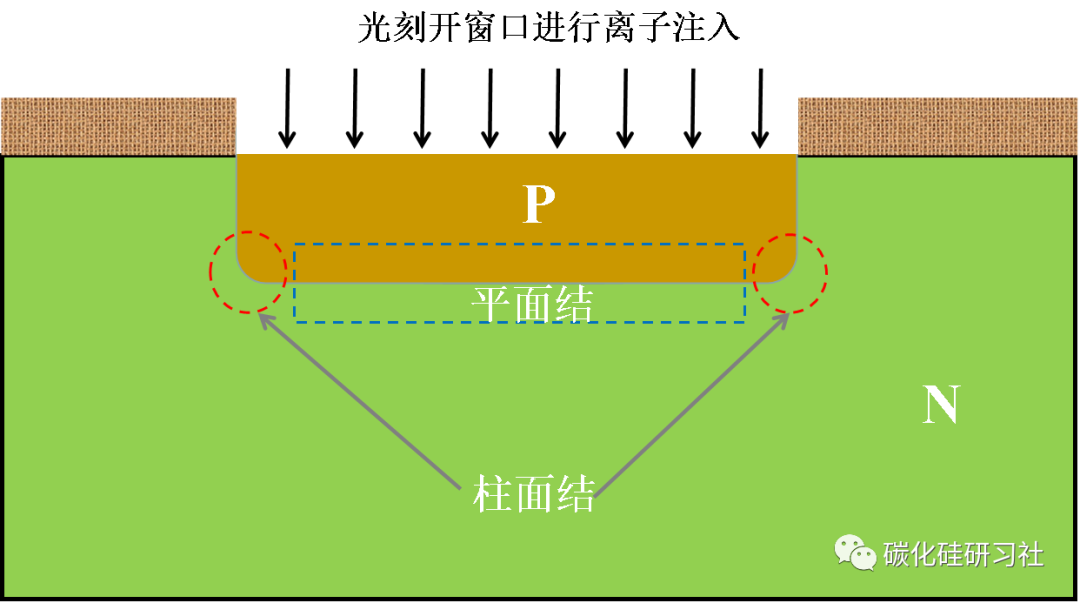

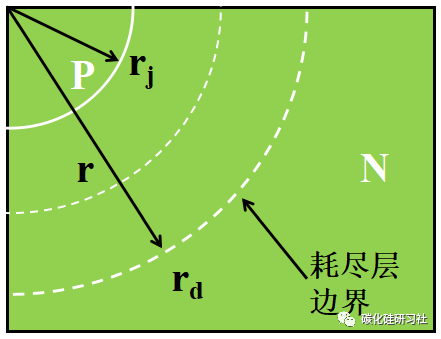

功率器件有源区含有PN结,施加反向耐压时,靠PN结承压。实际平面工艺中,在芯片发射极表面光刻掩膜开窗口后进行杂质注入推结,制作出的 PN结在中间大部分区域表面近似于平面。但是,在四条边角处,由于P型区杂质离子的横向扩散,在近似认为横向扩散系数和纵向相同的假设下,所形成的耗尽区边界会呈现出柱面形或球面形,如图1所示,就会在扩散窗口附近形成两种不同的扩散结面,扩散结面的底部可以认为是一个理想的平面,称之为平面结,在扩散窗口的四条边和四个角由于扩散的终止分别会形成柱面结和球面结。

图1 PN结形貌示意图

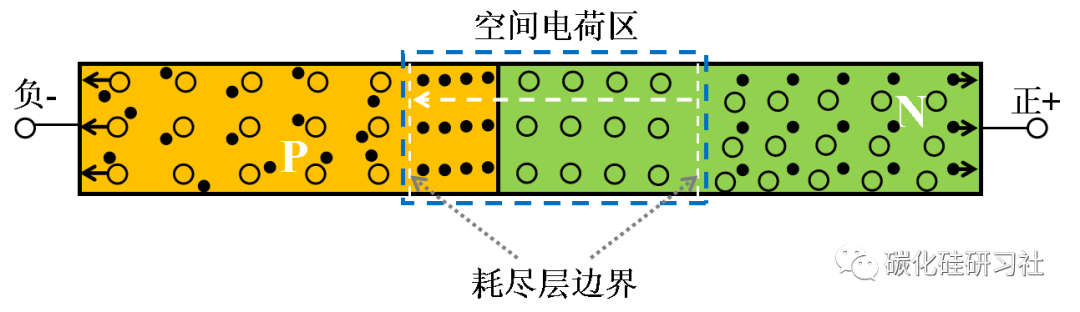

对PN结施加反向偏压,反向偏压在空间电荷区产生的电场与内建电场方向一致,空间电荷区的电场增强,空六被强电场驱向P型区被抽走,电子被强电场驱向N型区被抽走,空间电荷区随之变宽。

图2 反向偏压下PN结载流子流向示意图

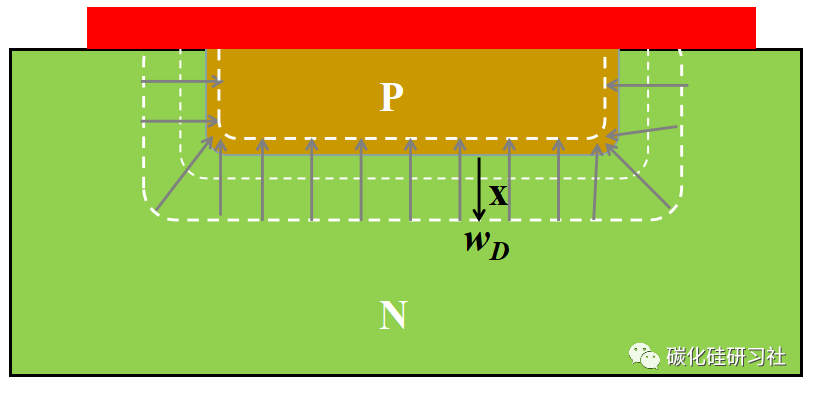

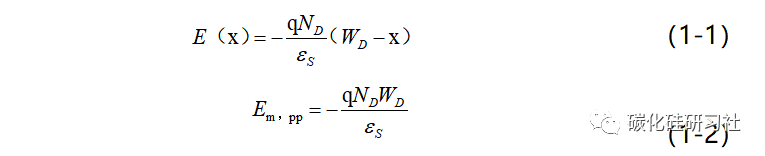

对于平面结,在横向上电场强度分布均匀,在一定纵向深度内,电场强度的变化只与耗尽层深度有关,见公式 1-1,同一深度电场强度相同,并且 PN结界面处的电场强度最大,见公式1-2。公式中WD为耗尽层边界宽度,x为耗尽层内的任一宽度,从公式可以看到,随着反向偏压的持续增大,耗尽层边界不断展宽,WD值持续增大,耗尽层内电场强度不断增大,当耗尽层边界展宽到一定程度,具有最大电场强度的PN结界面处首先达到其临界击穿电场强度,器件发生击穿。

图3 反向耐压时PN结电场示意图

图4 柱面结耗尽示意图

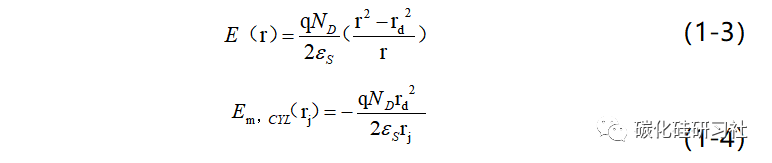

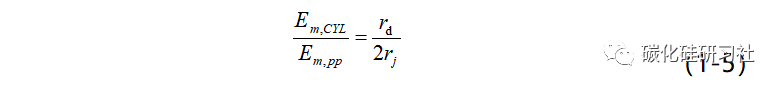

对于柱面结,电场强度会在此处发生集中,柱面结的电场强度见公式1-3,公式中rj为PN柱面结半径,r为柱面结处耗尽层半径的任意距离,rd为柱面结耗尽层边界半径,柱面结峰值电场也出现在PN结处,即rd=rj时,考虑到承受高压时,耗尽层最大半径远超PN结柱面半径,柱面结的最大电场强度可以近似表达为公式1-4。

将公式1-2 和公式1-4做対比,可以得到在同一反向偏压下柱面結和平面结电场强度之间的关系,见公式1-5。因为,rd>>rj,所以柱面结承受的电场强度是平面结的几至几十倍,当反向偏压达到一定程度,柱面结首先达到临界电场强度,提前发生击穿,从而降低整个器件的耐压能力。因此需要采取一定的结构降低有源区边缘的柱面结曲率效应的影响,降低柱面结处的电场集中,提高PN结击穿电压,这种结构即为终端区结构。

02

IGBT 失效场合、机理、原因

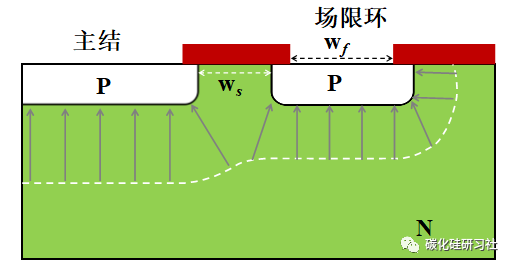

终端区设计的目的都是为了降低有源区边缘的柱面结或球面结曲率效应的影响,从而降低柱面结或球面结处的电场集中。下面我们以场限环结构为例来具体说一下终端区的工作原理。

图5 场限环结终端工作原理

场限环围绕在有源区外围,和有源区具有相同的掺杂类型,场限环无任何电位连接,采取浮空设置。其分压的原理即是:场限环放置在有源区主结的耗尽层内,当主结施加反向偏压时,场限环因为处于耗尽层内,其电压为0至所施加的反向偏压中间的任意值,在外加反向偏置电压一定的情况下其值大小和距离主结的宽度Ws有关,最终施加在N区和场限环之间的反向偏置电压为主结纵向反偏电压与场限环电位之差,所以耗尽时场限环处的耗尽层要较主结处的耗尽层窄。在耗尽过程中,主结的耗尽层和场限环的耗尽层不断扩展,最终相交连接起来,降低了有源区主结边缘柱面结曲率,减小了电场集中,从而提高主结的击穿电压。

场限环设计中有两个关键因素,其一是场限环距离主结的距离Ws,距离过大,主结耗尽层扩展不到场限环,击穿电压和没有场限环设置时一样;距离过小(可以想象为无限接近,有源区面积外扩一圈),它的电势基本上等于主结上的电势,仅仅是将最大电场转移到场限环的柱面结处,依然限制了击穿电压的提高,因此此间距需要合理设置。其二是场限环的环宽,环宽过窄,即使距主结的间距己经设在最佳位置,依然不能有效地减少耗尽层的曲率;环宽过宽,则浪费芯片面积,因此也需要合理设置。

03

终端区设计注意事项

1、足够的击穿电压

首先要守好其本分,击穿电压要满足芯片或器件的应用需求,尽管由于柱面结的存在,理论上无法达到平行平面结的击穿电压,但是一个好的终端结构应该尽量向平面结电压逼近。

2、减小终端尺寸

在芯片面积一定的情况下,终端尺寸越大,终端区面积越大,有源区面积就越小,会降低芯片的通流能力。因此尽量选用小尺寸的终端结构,提高有源区面积占比,增大通流能力。

3、可靠性考虑

终端设计时也要考虑钝化体系的选择,提高器件的可靠性。尽量选择一些机械性能好、柔韧性好、不容易开裂,内部电荷少,临界击穿电场高,抗外部离子沾污能力强,不易水解、不吸潮以及不易与外界发生化学反应的材质。

4、成本考虑

终端区设计时除性能上的考量外,还要兼顾其制造成本,在设计时最好可以兼容有源区工艺,减少光刻步骤,降低工艺制造成本。

04

本文小结

实际制造工艺过程中,PN结在有源区边角处形成柱面结和球面结,受柱面结和球面结曲率效应影响,使得电场在此处集中,导致器件提前击穿。终端结构即是用来降低有源区边缘柱面结和球面结曲率效应的影响,从而减少柱面结和球面结处的电场集中,提高器件击穿电压。由此来看,终端区所谓的浪费芯片面积也是不得已而为之。终端设计需要兼顾击穿电压、终端尺寸、可靠性和经济成本。

审核编辑:刘清

-

IGBT器件的防静电注意事项2025-05-15 2137

-

设置射频网络分析仪的测试条件有哪些注意事项2025-05-06 1128

-

功率逆变器应用采用宽带隙半导体器件时栅极电阻选型注意事项2023-11-23 1742

-

功率器件终端区设计的必要性、工作原理及注意事项2023-11-14 5229

-

擦除FLASH零等待区期间需注意事项2023-10-23 663

-

功率信号源操作注意事项有哪些2023-07-14 1342

-

使用 CMOS 和 BiCMOS 逻辑器件时的功耗注意事项-AN2632023-02-07 638

-

电机控制:终端应用需要考虑的具体注意事项2022-11-01 869

-

地址配置的必要性、方法及注意事项2022-09-09 1883

-

TDA8035器件所用引脚有哪些注意事项2022-01-17 1067

-

工控机使用有哪些注意事项2021-10-29 2016

-

接口电路的必要性2021-07-29 1627

-

基于航迹数据的机场终端区进场效率分析2021-07-05 827

-

终端区管制运行效率的集成综合评估模型2021-04-15 826

全部0条评论

快来发表一下你的评论吧 !