SDRAM工作原理 SDRAM布局布线说明

存储技术

描述

SDRAM全称Synchronous Dynamic RAM,同步动态随机存储器。首先,它是RAM,即随机存储器的一种。用作与CPU的临时数据交换,速度快,可以随时随地读写,掉电不保留参数。这里的随时随地是指它可以在任意时间指定任意地址进行访问和读写操作。

然后,他是SDRAM,即同步的、动态RAM,动态是指结构致使其需要不断的刷新才能保证存储正常工作;同步是说其有一个同步时钟,可是保持跟CPU的时钟同步进行数据传输和接收。

目前,嵌入式系统更多的是采取支持双边沿传输的DDR(Double Data Rate) SDRAM。之前的SDRAM是单端时钟信号,在上升沿传输数据,而DDR的时钟,可以做到上升沿和下降沿传两次数据,速度就整体的翻倍了,并且采用的是抗干扰能力强的差分输出。

1.电压、频率介绍

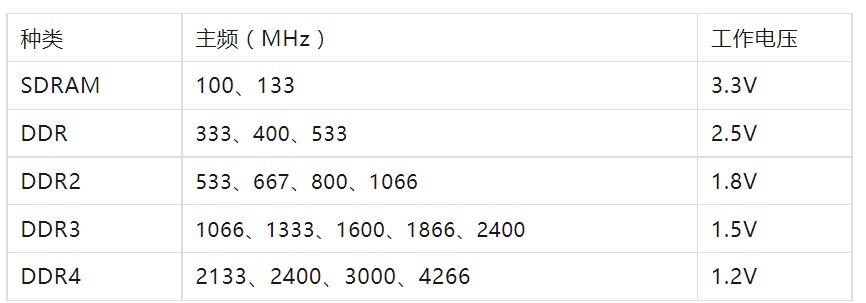

我们都知道频率越高,功耗就越大,所以越是频率快的,相应的电压就会越低,来让功耗更加合理。而DDR采取了预读取技术,让频率可以做到更高。DDR2采取了4bit预读取,DDR3采取了8bit预读取。因此他们的可以达到的频率和电压如下所示:

2.信号介绍

以DDR2为例。有如下信号:

CS、CLK P/N、CKE、CA(0:9)、DQ(0-31)、DQS P/N(0:3)、DM(0:3)、ZQ。还有电压Vss、Vcc。

下边一一介绍:

还有电源的就不赘述了,上边已经提到过了。

3.布线说明

由于DDR是同步的存储器,对数据的即时性要求很高,它还是执行CPU命令,与CPU连通的重要器件。因此,布线方面要求极多。DDR1/2因为频率稍低,跑在400mhz以下要求还少一些,就尽量做到线短、线齐就可以。(我敢这么说是因为曾经有一个项目,由于空间有限,CPU到DDR2的线走的是一塌糊涂,不堪入目,虽然平台SI仿真通过了,心还是悬着。等板子回来调试发现果然没有问题啊。。。)对于DDR3往上的产品,就老老实实好好走线吧。一般平台都有明确的要求要如何走CPU到DDR之间的线。大多数平台强烈建议这部分走线不要动,直接搬过去用就好了。如果要自己走,就会有严格的要求,要按照要求走,还要仿真通过(有的平台甚至会因为你不照着做而不想给你仿真)。每个平台都有自己的要求,一定要跟平台明确好要怎么来布线。通常不外乎如下几点:

1> 差分线成对、等长走,差分阻抗100ohm。

2> 分组走线、组与组之间要留有足够间距,组内尽量等长。

3> 尽量少打孔,尽量少走短线。

4> 控制好误差范围。

-

DDR SDRAM工作原理简介2023-03-07 4298

-

SDRAM与DDR布线指南.zip2022-12-30 642

-

SDRAM和DDR SDRAM等布线的原则是什么?2021-05-19 1761

-

SDRAM的基本工作原理是什么?怎么实现SDRAM控制器?2021-05-10 2136

-

如何实现Reg istered SDRAM接口电路的设计?2021-04-12 1030

-

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文2018-12-25 1741

-

关于SDRAM电路的设计2018-06-11 4505

-

DRAM、SDRAM及DDR SDRAM之间的概念详解2018-06-07 95256

-

SDRAM工作原理 DRAM控制器系统设计架构2018-04-30 6005

-

SDRAM工作原理2012-08-13 7790

-

SDRAM设计详细说明2010-04-22 1161

-

SDRAM的工作原理2010-03-26 1125

-

SDRAM与DDR布线指南2010-03-18 994

-

使用Verilog实现基于FPGA的SDRAM控制器2009-06-20 2508

全部0条评论

快来发表一下你的评论吧 !