ADC对连续外部信号进行采样的概念和用法-以M031/M032为例

电子说

描述

M031/ M032 内建逐次逼近式模拟数字控制器 (SAR ADC),支持 12 位分辨率,每秒可实现两百万次采样 (Msps)。内建模拟多任务器 (Analog Multiplexer), ADC 输入信号可选择从外部管脚或者内部电压。利用 PDMA 功能,ADC 可以在没有 CPU 参与的情况下运行,执行最大采样率,最小化系统电流消耗,或允许 CPU 执行其它工作项目。

完整应用笔记讨论了 ADC 一般操作流程、软硬件注意事项及 PDMA 的使用方法。最后范例程序以 PDMA 和 ADC 来展示连续采样外部信号的流程。

概述

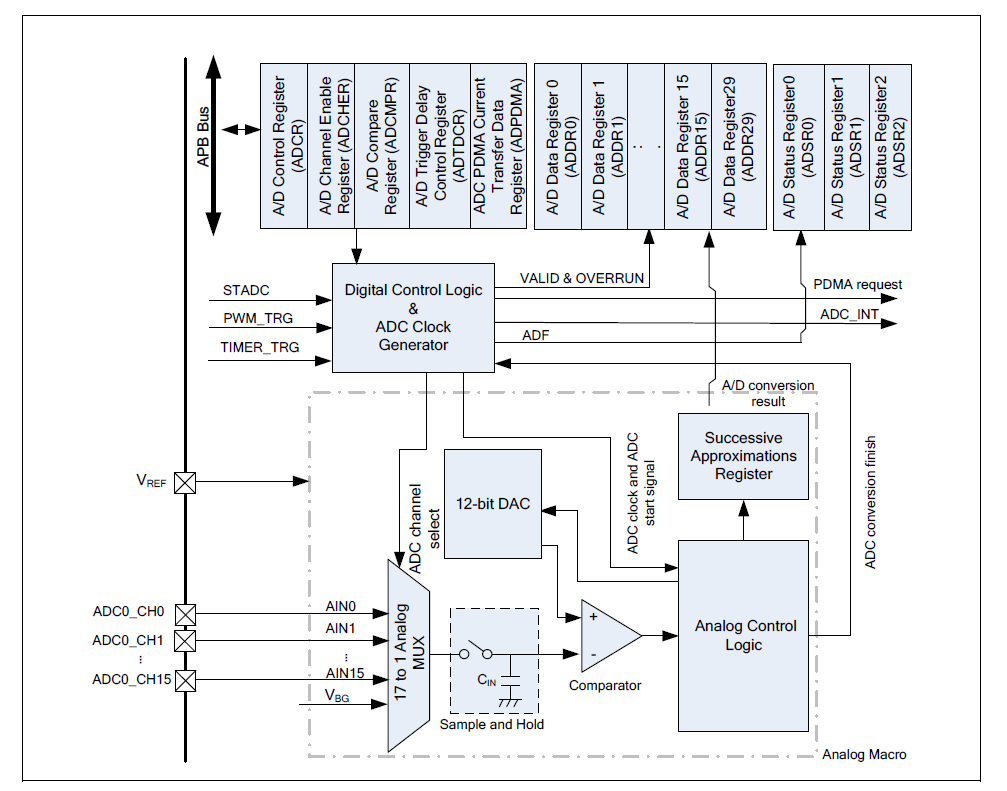

下图说明输入信号,参考电压选择和寄存器的内部连接方式,并包含以下功能:

一组 12 位分辨率 SAR ADC 并带独立 VREF 管脚

多达 16 路的单端输入通道或 8 组全差分仿真输入通道

1 个内部输入通道 band-gap voltage (VBG)

A/D 转换开始条件:

软件向 ADST 位写1

外部 (STADC) 管脚触发

Timer 0~3 溢出脉冲触发

PWM 事件触发

每个信道的转换结果储存在相应数据寄存器内,并带有有效和覆盖标志

支持 PDMA 传输模式,将转换结果储存在用户指定的目标地址

ADC 控制器框图

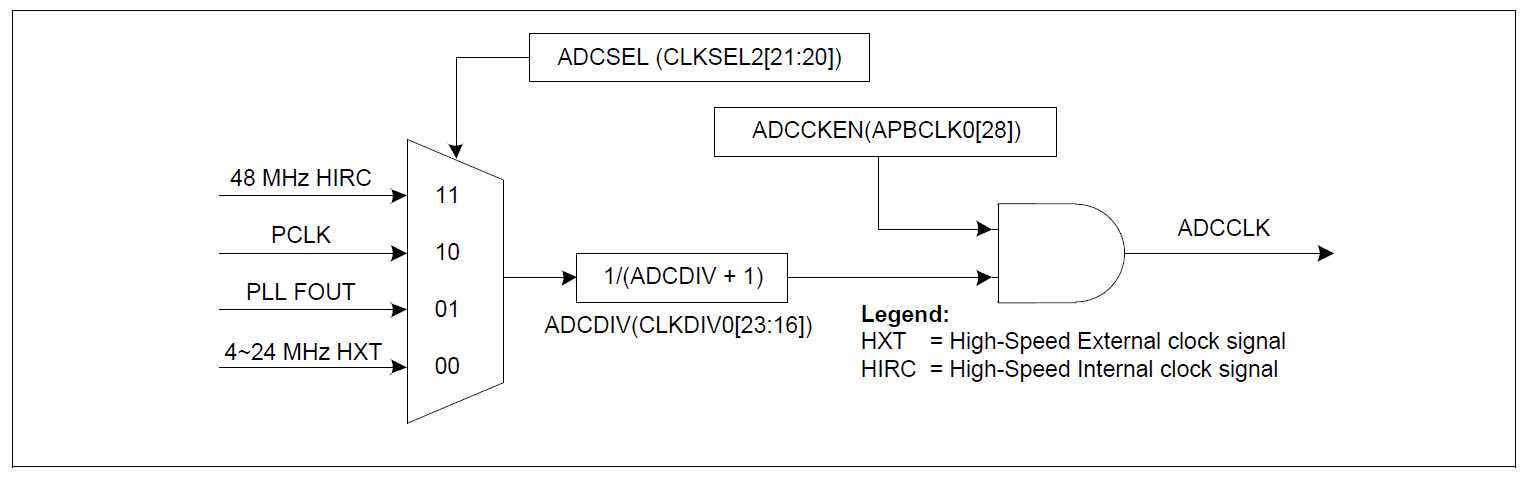

一般操作:时钟源选择

ADC 具有一组 8-bit 预分频器,按照以下列公式得出 ADC 时钟频率 (ADCCLK) 为:

ADC 时钟频率 (ADCCLK) = (ADC 时钟源频率) / (ADCDIV + 1);其中 M031/ M032 ADC 时钟频率 (ADCCLK) 最大值为 34 MHz。使用者可以透过 PLL 倍频,产生 34 MHz 或者 68 MHz 频率。将 PLL 设定为 ADC 时钟源,并透过 ADCDIV 除频产生 34 MHz,即可让 ADC 运行在最高速度。

ADC 时钟源控制

输入模式选择

ADC 输入模式可以选择为单端输入或全差分输入。当 DIFFEN(ADC_ADCR [10]) 为 1,ADC 为差分输入。

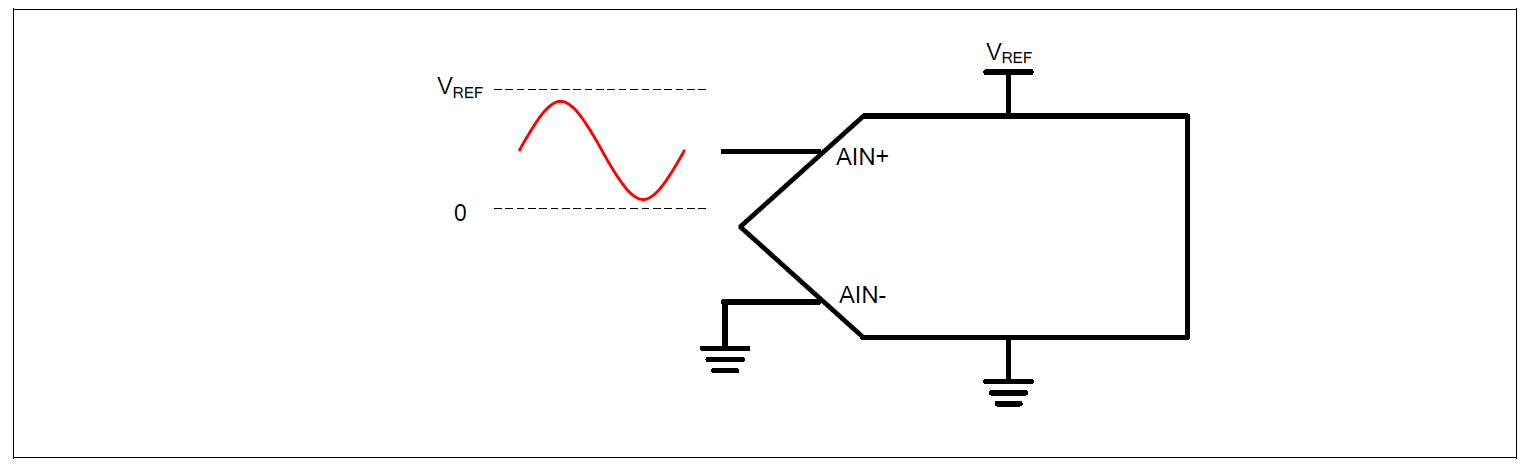

单端输入

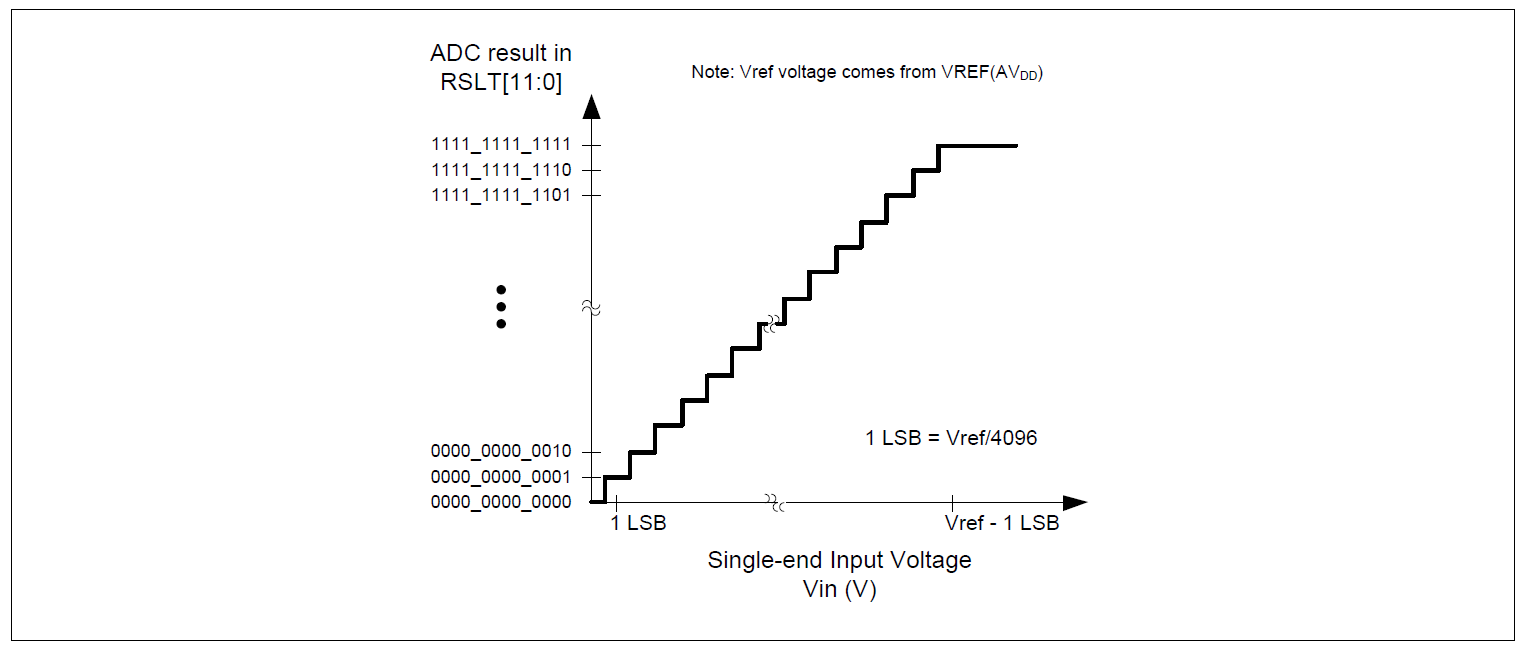

如图「ADC 单端输入信号」所示,在单端输入模式下,AVSS 或者 VSS 为 ADC 负端输入的信号 (AIN-),外部输入电压为 ADC 正端输入的信号 (AIN+)。如「ADC 单端输入模式转换结果映像图」所示,在 0V 和参考电压 (V REF ) 之间,切分出微小电位阶。其数字结果以 0 到 4095 的无符号数,表示输入电压位于 0V 和参考电压 (V REF ) 之间的位置。

ADC 单端输入信号

ADC 单端输入模式转换结果映像图

全差分输入

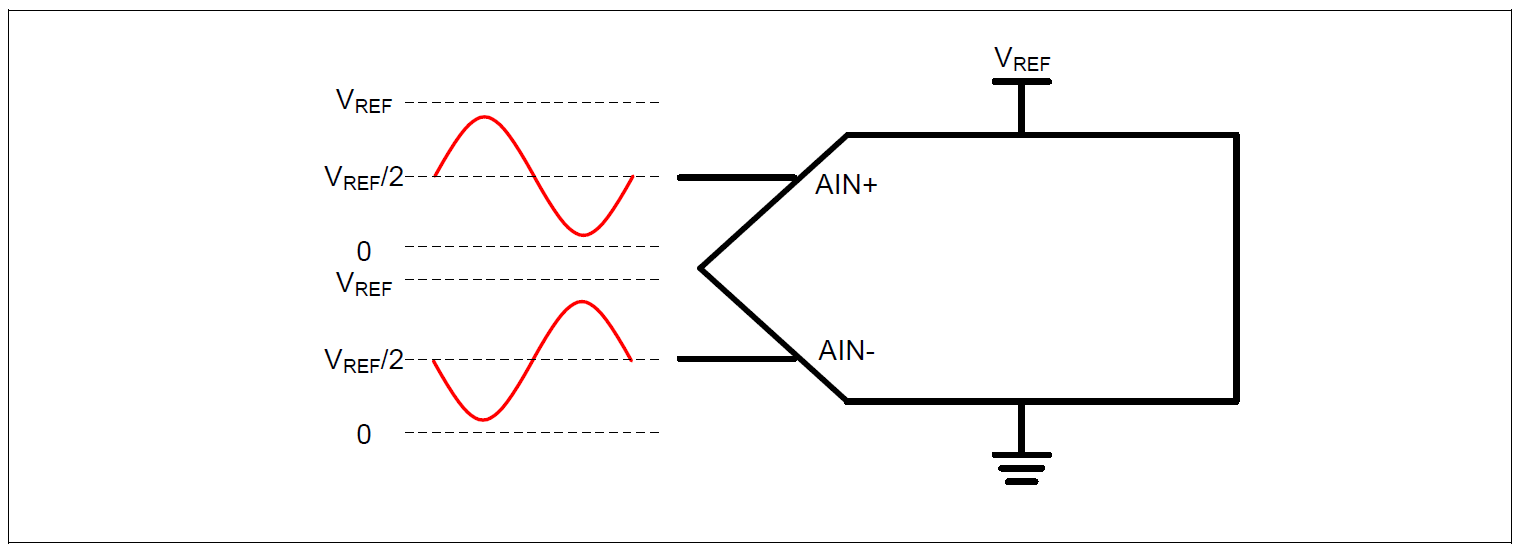

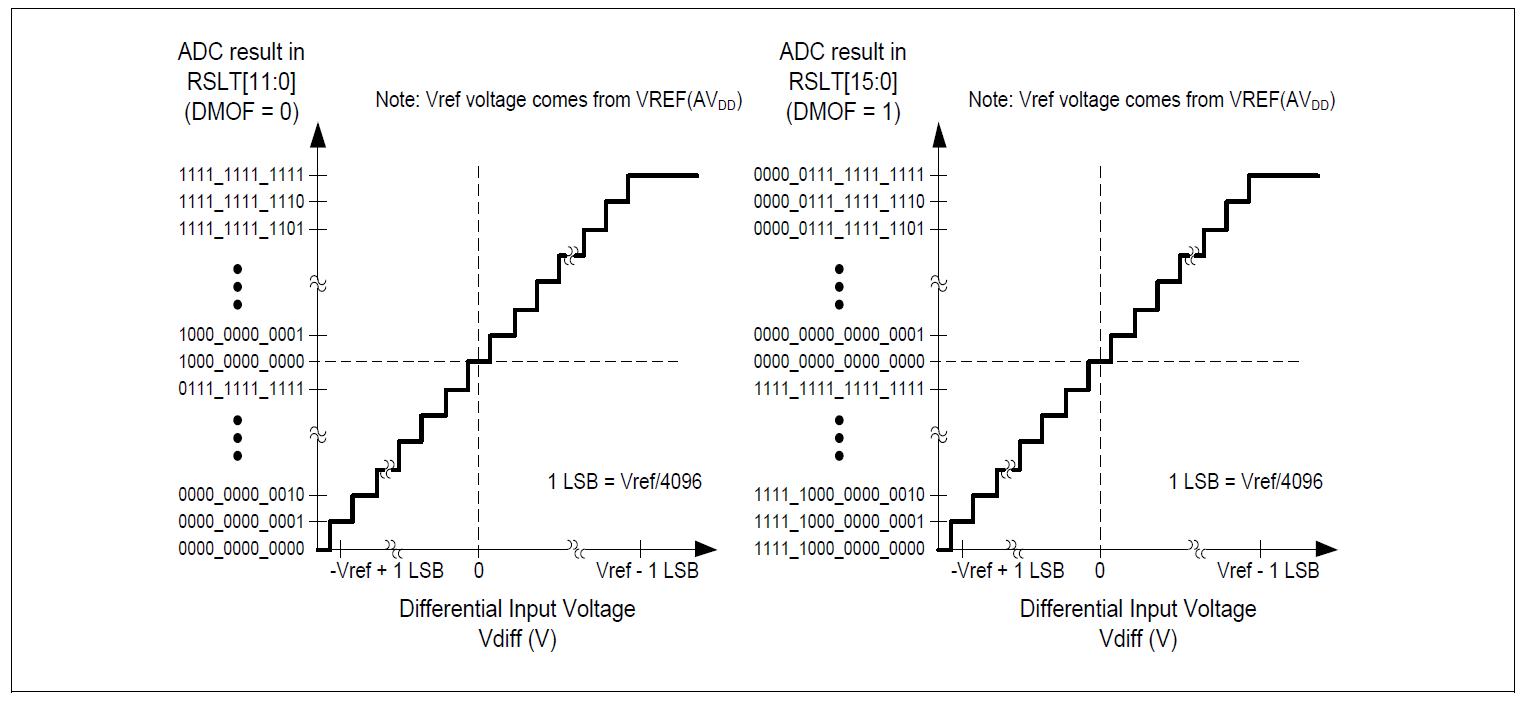

如图「ADC 全差分输入信号」所示,在全差分输入模式下,测量值是两个输入信号之间的差值,两个输入信号必须为 180° 反相信号,并固定共模电压为 VREF/2。由于一个输入管脚被定义为正输入管脚 (AIN+) 而另一个被定义为负输入管脚 (AIN-),因此根据哪个输入信号更高,差值可以是正的或负的。如「ADC 全差分输入模式转换结果映像图」所示,当 DMOF(ADC_ADCR [31]) 设置为 1 时,转换结果是以二的补码码形式表示的有符号数,或者当 DMOF(ADC_ADCR [31]) 设置为 0 时,转换结果是以二进制格式表示的无符号数。

ADC 全差分输入信号

ADC 全差分输入模式转换结果映像图

结论

完整的应用笔记基于应用角度,介绍模拟数字转换器的规格和特性。然后说明如何透过外部参考电压管脚 VREF、TSMP 设定及校准,最小化 ADC 误差并获得最佳 ADC 精准度的方法和应用设计规则。一旦用户掌握了这良好工作知识,就可以依照应用要求,基于速度、精准度及计算能力选择最适合软硬件设计参数。另外在 ADC 运行过程中,介绍利用 PDMA 快速地搬移数据或者利用数字比较器功能来侦测温度传感器、压力传感器及声音传感器,减少进出 ADC 中断次数,降低 CPU 负担,让 CPU 可以处理更多任务。

-

如何使用 M031/M032 系列微控制器 (MCU) 读取触摸屏信号并分析手指触摸的位置?2025-08-20 749

-

使用M032 ISP函数将UART处理器映射为SRAM2023-08-31 521

-

M031如何执行USB设备远程唤醒功能2023-08-30 736

-

如何使用M031/ M032系列微控制器读取触摸屏信号和分析手指触摸位置2023-08-29 598

-

码农的最爱!超好用新唐旗舰微控制器M031/M032系列帮你摆脱996魔咒!2023-08-10 3077

-

M031系列的输出电压范围是多少?2023-06-13 509

-

新塘单片机M031/M032系列规格书2022-05-05 1265

-

M031和M032系列微控制器的数据手册免费下载2020-07-06 1646

-

新唐科技M032 系列简介2020-02-29 4311

全部0条评论

快来发表一下你的评论吧 !