景芯SoC项目之DFT debug

描述

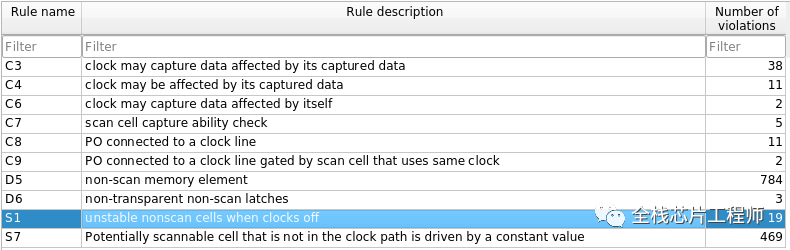

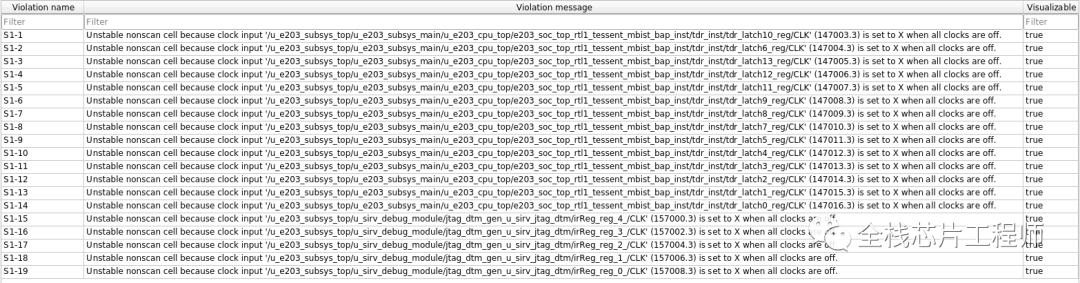

景芯SoC项目是个付费培训项目,项目数据在服务器上。景芯SoC在tessent完成edt occ插入并且仿真OK后,去综合,然后做scan chain insertion就一堆error S1,首先是28个S1 violation报告出来,

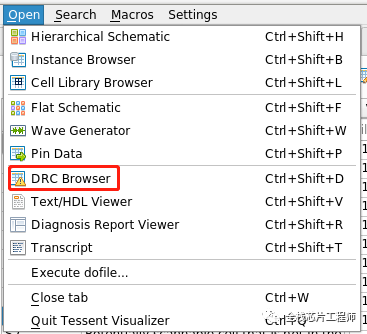

open vi 打开GUI,选Open -> DRC Browser

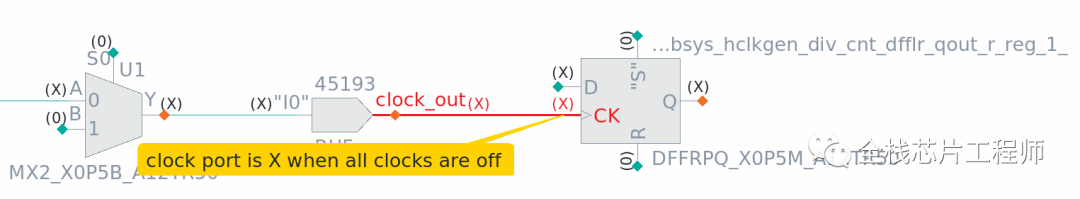

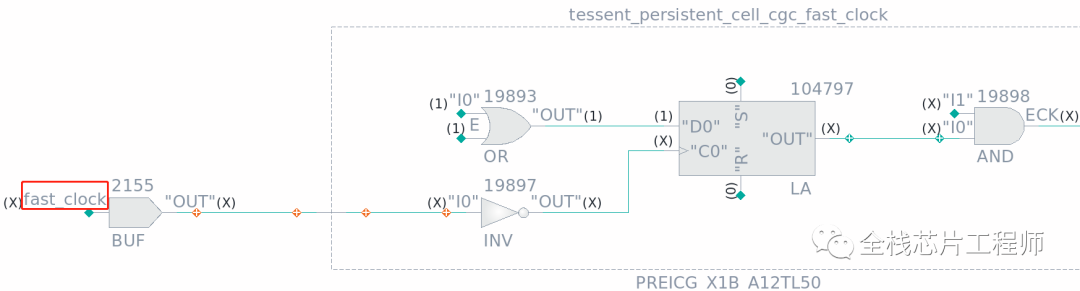

继续往前追踪,发现是PLL的高频时钟输出x

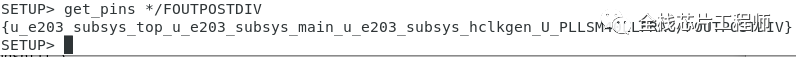

在网表get_pins找到PLL的输出CLK pin:

# get_pins */FOUTPOSTDIV

add_clocks 0 u_e203_subsys_top_u_e203_subsys_main_u_e203_subsys_hclkgen_U_PLLSM40LLFRAC/FOUTPOSTDIV

然就解决了9个S1 violation,剩下19个怎么解决呢?具体参见知识星球。

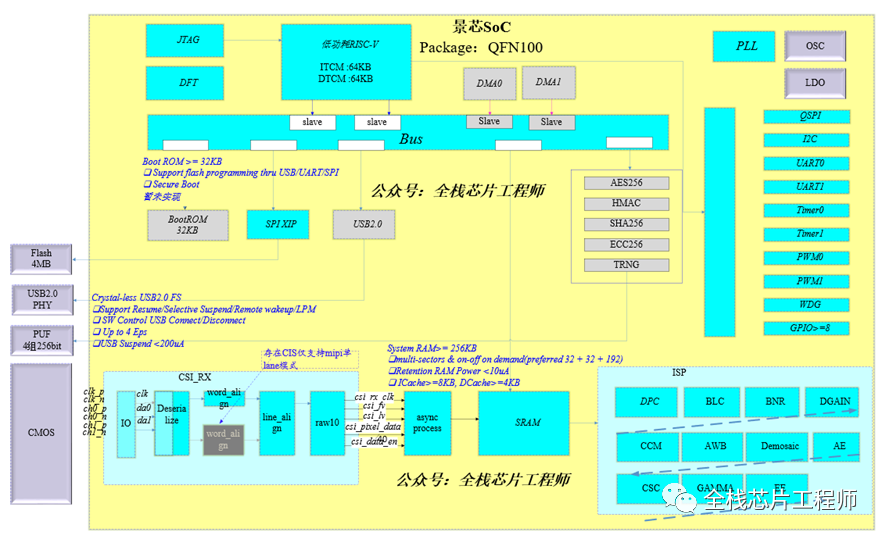

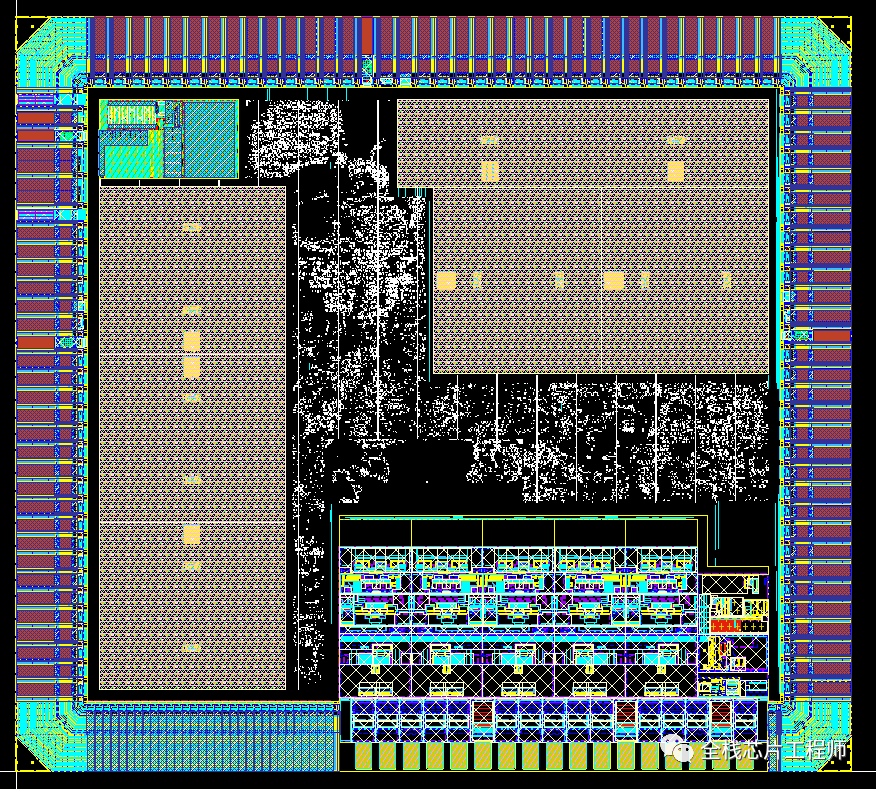

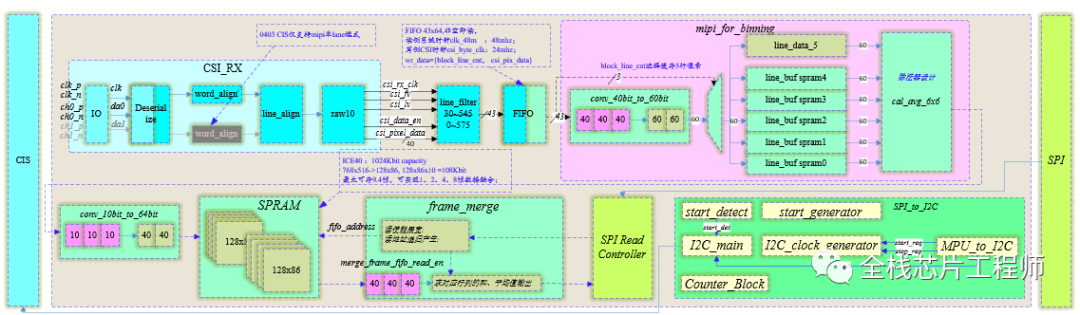

【全网唯一】景芯SoC是一款低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、CNN、QSPI、UART、I2C、GPIO、百兆以太网等IP,采用SMIC40工艺设计流片。

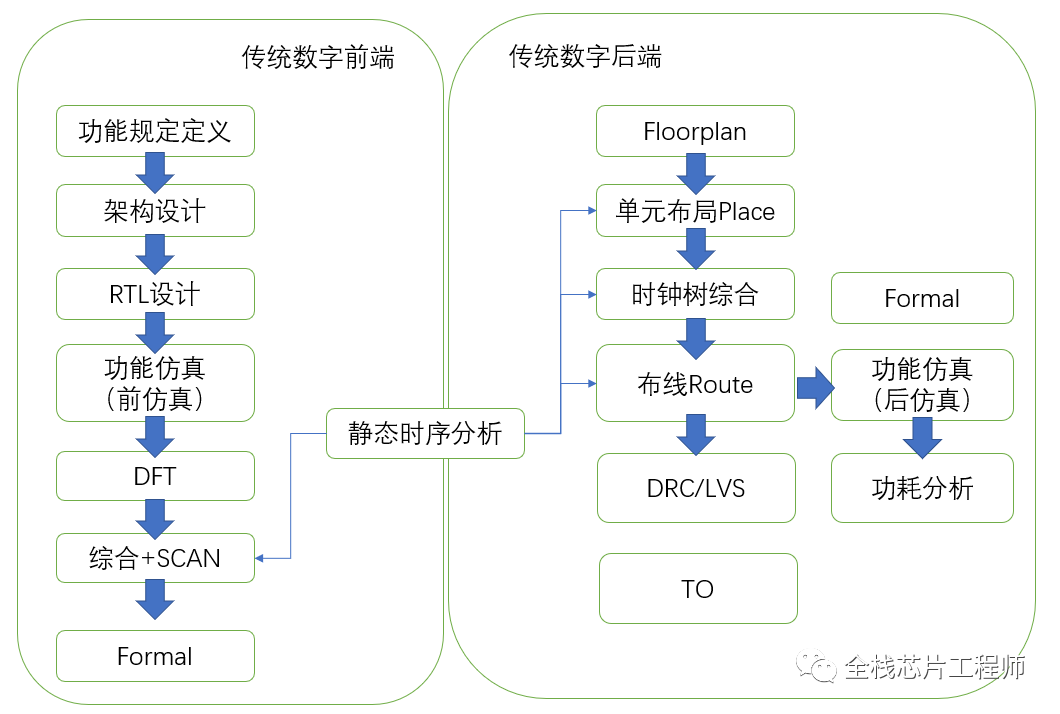

培训数据包括SoC前端设计、DFT设计、低功耗UPF设计、布局布线,提供服务器供大家实践!带你从算法、前端、DFT到后端全流程参与SoC项目设计。更多内容参见知识星球!

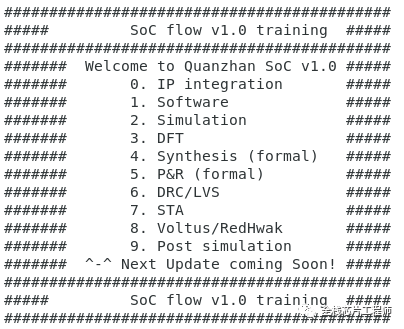

一键式完成C代码编译、仿真、综合、DFT插入、形式验证、布局布线、寄生参数抽取、PT分析、DRC/LVS、后仿真、形式验证、功耗分析等全流程。V1.0工程仿真如下,部分流程仍在开发中。

SoC一键式执行flow

MIPI设计

ISP图像处理

isp_blc - 黑电平校正

isp_bnr - 拜耳降噪

isp_dgain - 数字增益

isp_demosaic - 去马赛克

isp_wb - 白平衡增益

isp_ccm - 色彩校正矩阵

isp_csc - 色彩空间转换 (基于整数优化的RGB2YUV转换公式)

isp_gamma - Gamma校正 (对亮度基于查表的Gamma校正)

isp_ee - 边缘增强

isp_stat_ae - 自动曝光统计

isp_stat_awb - 自动白平衡统计

仿真结果:

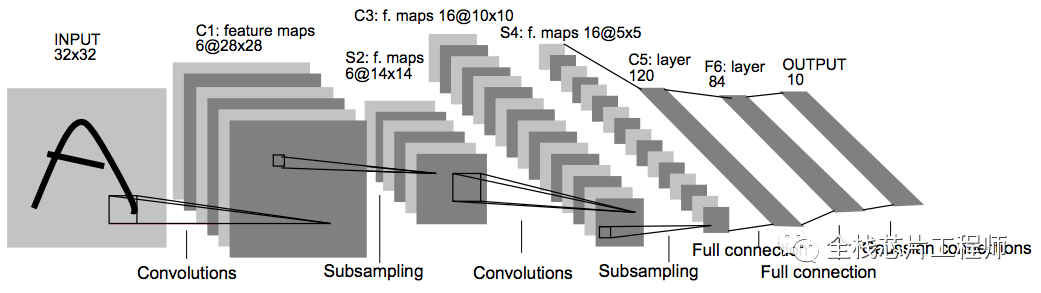

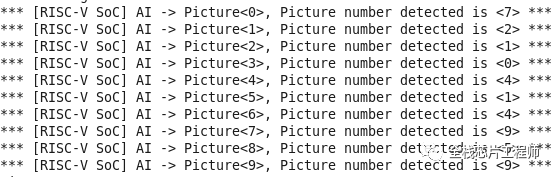

CNN图像识别

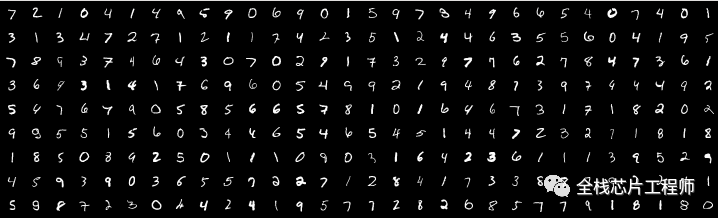

支持手写数字的AI识别:

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

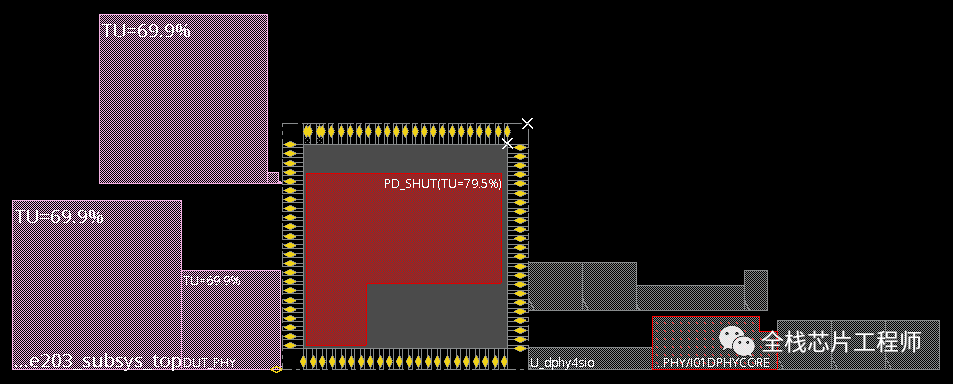

UPF低功耗设计

支持UPF低功耗设计(含DFT设计):

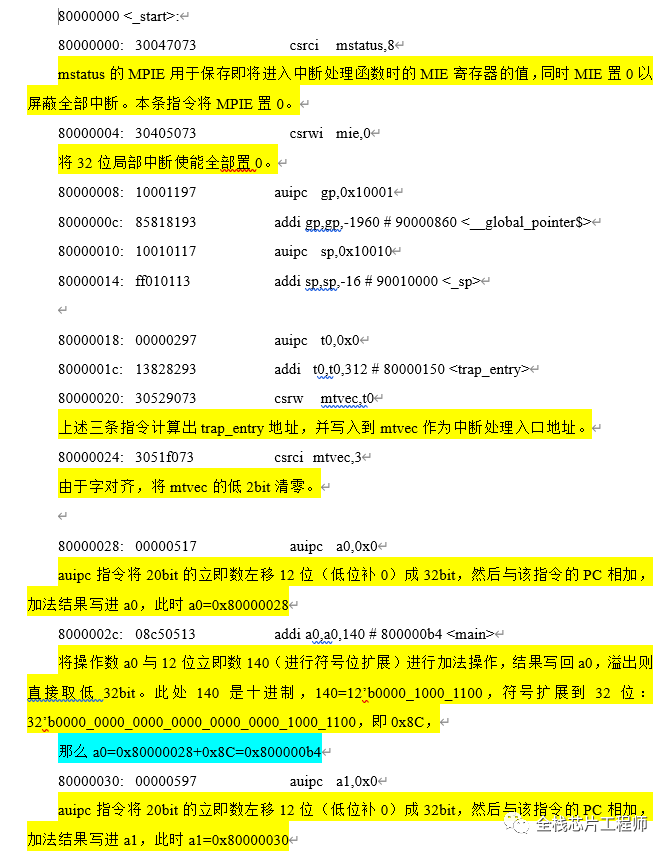

CPU启动指令分析

审核编辑:汤梓红

-

DFT设计—MBIST算法测试2023-12-09 8922

-

DFT和BIST在SoC设计中的应用2011-12-15 6782

-

急招DFT工程师(base地上海\西安)2017-04-14 4082

-

什么是DFT,DFT是什么意思2010-06-07 31686

-

分层DFT技术如何实现在最大化SoC2022-11-23 1820

-

一个典型设计的DFT组件2022-11-30 1706

-

处芯积律自研SOC项目2023-02-07 4750

-

景芯SoC的Spyglass检查2023-08-15 3740

-

景芯SoC/MCU v2.0重磅升级!9.1号涨价了2023-09-01 3103

-

SoC芯片设计中的可测试性设计(DFT)2023-09-02 4618

-

记录一次解决RT-Thread创建基于ART-PI的示例项目可以下载但却无法debug的问题2023-10-12 1277

-

DFT如何产生PLL 测试pattern2023-10-30 3685

-

一文了解SOC的DFT策略及全芯片测试的内容2023-12-22 5179

全部0条评论

快来发表一下你的评论吧 !