在不同应用场景下DPU不同的性能要求阐述

描述

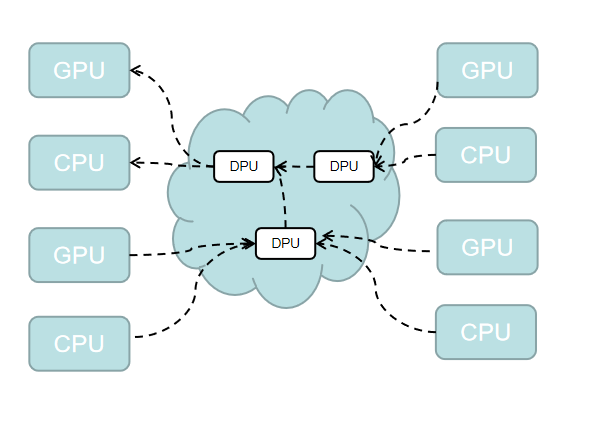

DPU本质上是通过DPU卡上资源,解耦计算、控制、存储,利用CPU、GPU、FPGA加速器等异构处理单元,通过以智能卡为接口的网络实现高效的数据分发和调度。市面上流行的DPU产品基本上都实现了3类功能卸载,包括网络功能卸载、存储功能卸载、安全服务卸载。

DPU网卡直接将数据送达GPU和虚拟机CPU,时延3~4微秒。同时DPU卡通过自身的加速模块,实现了数据处理效率的提升,控制能力的卸载。从某种角度来看,DPU 是一个强IO型的板卡系统,其IO带宽几乎与网络带宽等同,能够直接进行数据内容处理,以及复杂计算。

| DPU功能示意图

DPU通用架构

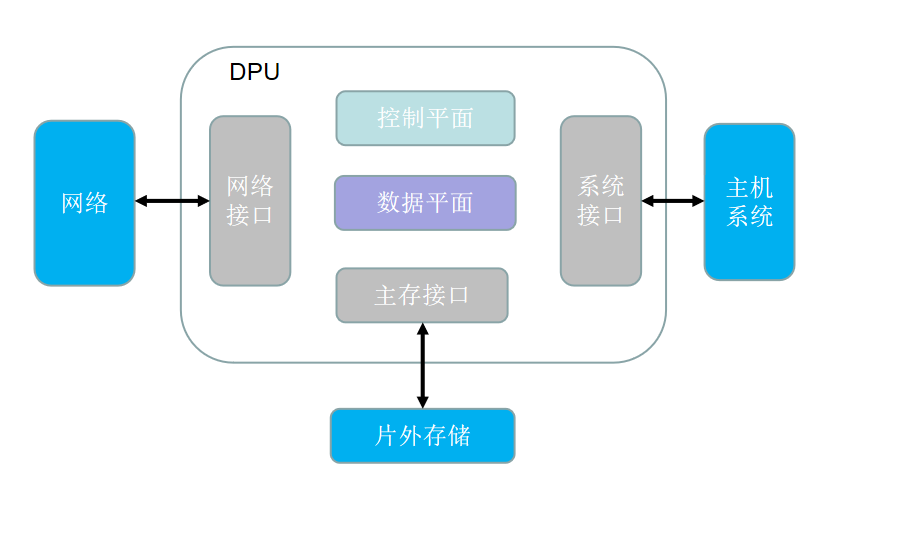

通常,DPU板卡包括控制平面、数据平面及接口平面三个组成部分。

| DPU参考架构

控制平面

控制平面负责DPU网卡的运行管理、计算任务和计算资源的配置,以及虚拟机的管理。控制平面通常由通用处理器核来实现,如ARM、MIPS等,运行标准Linux系统。控制平面与数据平面交互的驱动程序进行了深度优化,以提升数据交互、任务调度效率。控制平面的主要功能包括运行管理、计算任务和计算资源配置、虚拟机管理等功能。

# 运行管理

运行管理包括设备的安全管理和实时监控。安全管理模块包括信任根、安全启动、安全固件升级以及基于身份验证的容器和应用的生命周期管理。实时监控模块动态监测DPU各子系统、各处理核,实时监测流量,记录设备访问日志。

# 计算任务和计算资源配置

根据计算任务实时配置处理单元间的通道,以及各处理单元参数。根据处理单元资源利用情况实时调度任务。

# 虚拟机管理

卸载虚拟机管理,隔离数据和资源,记录运行状态,通过vDPA(Virtual Data Path Acceleration)框架等技术协助虚拟机热迁移。

数据平面

数据平面负责高速数据包处理、虚拟化协议加速、安全加密、流量压缩、算法加速等功能。

# 高速数据包处理

OvS解析、匹配和处理,RDMA远程数据传输加速,处理带宽达到100Gbps、200Gbps、400Gbps,具备有状态数据处理能力,能够记录各连接信息,能够在多连接间无缝切换。

# 虚拟化协议加速

支持SR-IOV、VirtIO、PV加速,支持VxLAN、Geneve Overlay卸载、VTEP卸载。

# 安全加解密

IPSec和TLS加解密加速,安全算法加密。

# 流量压缩

实时压缩/解压缩数据,加速地址转换和地址重映射、数据流变换。如面向多媒体流、CDN和4K/8K 视频的 流量整形加速等

# 其他算法加速

NVMe 存储协议、大数据分析SQL加速。

接口平面

接口平面包括三个方面系统接口平面、网络接口平面、主存接口平面。

系统接口平面

主要负责DPU与其他处理平台(如X86、ARM、GPU、FPGA等)或高速外部设备(SSD等)的集成。DPU板卡数据传输量大,带宽要求高,通常基于PCIe实现接口平面,可以分为EP(Endpoint)类和RC(Root Complex)类两种。EP类接口 DPU作为其他处理平台的从设备。

支持硬件设备虚拟化功能,如SR-IOV和VirtIO,并且可以灵活地支持多种类型的设备,如NIC、Storage、Compute等。RC类接口 DPU作为主设备与加速平台或外设连接。部分数据处理卸载到第三方加速平台,支持DMA方案。

网络接口平面

负责DPU与网络的相连,以以太网接口、FC接口为主。通常需要借助专门的网络协议处理核加速网络包的处理。包括:L2/L3/L4层的ARP/IP/TCP/UDP网络协议处理、RDMA、数据包交换协议、网络虚拟化协议,实现100G以上的网络包线速处理。

主存接口平面

是DPU与缓存的接口。缓存用于存储数据平面的中间结果,实现处理核之间的数据通信,包括DDR和HBM接口类型;其中DDR可以提供大容量缓存(512GB以上);HBM可以提供大存储带宽(500GB/s以上)。

DPU的架构设计

DPU的多种架构的设计主要是指DPU 数据平面的设计。

在DPU的组成框架中,控制平面主要用作CPU的卸载,数据平面则是用作各种专用功能、算法的加速。控制平面通常借助通用服务器实现。数据平面包含了各种专用的处理核,以及可编程的处理模块,提升数据的处理速率。以应用特征为依据,可以把应用分为“IO密集型”和“计算密集型”两类。

IO密集型应用有较高的输入和输出带宽,数据直接来自于IO,具备流式特征,要求线性处理,如路由转发应用、数据加密应用、压缩应用等。

IO密集型处理器芯片的构建方式:以CPU或者专用加速器为核心构造主体计算架构,前者可称之为控制中心模式,后者为数据中心模式。DPU偏向于数据为中心的结构,集成了更多类别的专用加速器,在获得机制性能的同时牺牲了指令灵活性。

DPU要处理更多的网络IO,包括外部以太网、内部虚拟IO。同时DPU通常也会配置少数通用核(如ARM、MIPS)等来处理一定的控制面任务,通过运行轻量级的操作系统来管理DPU上的异构核资源。

# 数据平面是DPU设计的关键,数据平面通常需要解决4类问题:

1.异构处理核多,需要解决处理核之间的功能解耦、协同配合问题,需要妥善处理好网络、存储、安全、虚拟化、业务的卸载加速。

2.高并发的数据处理,并行计算、并行数据流,核心数量众多,规模通常达到几百个。

3.片上互联问题,包括处理核之间的数据互联,核间的数据一致性问题。

4.高效易用的编程方式。

构成DPU的处理核包括GPU、FPGA、ASIC、NP、类脑芯片。

GPU(Graphics Processing Unit)图形处理器。在浮点运算、并行计算方面,GPU可以提供优秀的性能,执行类型高度统一的、相互吴以来的大规模数据处理效率高。GPU中逻辑运算单元(ALU)多,控制器功能简单,缓存少,擅长高强度的并行计算。GPU可以将大规模、非结构化的数据分解成独立模块,分配给各个流处理集群(SMM)。每个流处理集群再次把数据分解,分配给调度器,调度器将任务放入自身所控制的计算核心core中,完成最终的数据处理任务。

FPGA(Field Programmable Gate Array):是在PAL、GAL、CPLD等可编程期间的基础上发展起来,作为专用集成电路领域中的一种半定制电路而出现,解决了定制电路的不足,无指令、无需共享内存。寄存器和片上内存由各自的控制逻辑,不需要仲裁和缓存。通过编程可定义单元配置和链接架构,具有较强的灵活性。流水线并行和数据并行,实时性最强,灵活性最高。但是只适合定点运算。FPGA内部有很多可配置逻辑模块(CLB),通过对CLB的配置来实现逻辑功能。FPGA带有丰富的片上存储资源,可以大大减少访问时延(访问DRAM存储大约是访问寄存器存储延迟的几百倍以上)。FPGA可硬件编程,可进行静态重复编程和动态系统重配置。

ASIC(Application Specific Integrated Circuit):根据产品的需求进行特定设计和制造的集成电路,能够在特定功能上进行强化,具有更高的处理速度和更低的能耗。但是研发成本高,研发投入周期长,只有用量足够大时才能够分摊前期投入,降低成本。

NP芯片由微码处理器和协处理器组成,多个微码处理器并行运行,可以通过编制微码控制处理流程。复杂的标准操作,如内存操作、路由表查找、QoS拥塞控制、流量调度采用硬件协处理器来提高处理性能。NP芯片具有丰富的高速I/O接口,包括物理链路接口、交换接口、存储器接口、PCI/PCIE总线接口等,通过内部高速总线连接在一起,具有很强的硬件并行处理能力。

类脑芯片:类人脑芯片架构是基于神经形态的架构,模拟人脑处理过程,感知世界、处理问题。此类架构芯片功能类似于大脑袋额神经突触,处理器类似于神经元,而其通讯系统类似于神经纤维。通过神经元网络系统,计算机可以感知、记忆和处理大量不同的信息。类脑芯片有望形成自主认知的新形势,突破传统计算机体系结构的限制,实现数据并行传送、分布式处理,以极低功耗实时处理大量数据。

SoC架构:基于多核SoC的DPU使用大量嵌入式CPU核来处理分组,可编程性比ASIC好,可以使用标准的DPDK代码在linux环境中运行。但是在40Gb以上的高带宽场景,CPU核数显著增加,数据包处理的复杂度提升,效率降低,且延时增大。对于有状态的数据流往往只映射到一个CPU核心/线程,以防止状态共享和单流中的无序处理。

众观市面流行的DPU型板卡,实现各不相同。Intel IPU Oak Springs Canyon基于Agilex FPGA和Xeon-D CPU实现。Intel IPU(Mount Evans)基于ASIC实现,通过PCIe链接4个Xeon处理器,加速引擎包含:vSwitch、防火墙、虚拟路由、NVMe、QAT(量化感知)。Xilinx的 Alveo系列加速卡,融合了FPGA、MP SoC和ACAP。这些DPU处理场景各有侧重,难以形成有效比较。

各类实现方式的性能比较

DPU与CPU、GPU等处理芯片构成统一的计算平台,高效支撑已有应用,并为未来应用提供必要的运行基础。对于DPU在网络、存储、计算、安全方面的加速性能,《专用数据处理器(DPU)性能基准评测方法与实现》中提出了对DPU的评测标准,可以归纳为:

网络能力

表项(会话)规模,表征DPU网络支撑节点规模能力。

吞吐能力,表征DPU网络数据包的转发处理能力。

建表性能,表征DPU支持并发会话或路由学习的能力。

时延性能,表征DPU转发处理数据包的效率。

网络可观测能力,表征DPU的统计和遥测能力。

确定性网络能力,表征DPU网络的可靠数据传输能力。

存储能力

DPU上存储加速卸载的主要场景是NVMe-oF。

NVMe-oF存储的I/O读写能力,表征DPU存储的读写能力。

NVMe-oF存储的吞吐能力。

NVMe-oF存储的时延性能,表征DPU存储的数据读写和传输效率。

NVMe-oF存储的QoS能力,表征DPU存储的可靠I/O读写能力。

计算能力

计算能力包括大数据计算加速、ML/AI算法加速和视频编解码等。

计算业务的吞吐能力,表征DPU计算业务处理能力。

计算业务的时延性能,表征DPU计算业务处理效率。

计算业务的并行处理能力,表征DPU并行处理能力。

计算业务的能效比,表征DPU计算业务处理效能。

安全能力

安全策略规模,表征DPU上支持的安全策略规模。

安全业务的吞吐能力,表征DPU加解密和安全过滤匹配查询的能力。

安全业务的时延性能,表征DPU安全处理的效率和效能。

安全业务的并发会话规模,表征DPU安全并行处理能力。

不同厂商的DPU定位不同、功能各有差异,网络、存储、计算、安全、管理各有所侧重。作为最终用户,必须首先明确自身需求,在此基础上,选择合适的测试指标体系和具体的测试模型,才能对同类产品有比较清晰的了解。

不同应用场景的性能要求

随着云技术、5G等技术的发展,DPU将在云网络、存储、安全、电信与边缘计算等场景广泛应用。

云网络应用场景

云网络场景具体包括网络功能卸载,包括虚拟交换机功能的卸载、虚拟主机接口的硬件加速、网络协议的卸载。虚拟交换机卸载,解决报文头分析,L2/L3转发策略、Overlay网络报文封装/解封装。

虚拟主机接口的硬件加速,为虚拟主机提供virtion-net硬件接口,提升网络I/O性能。RDMA/RoCEv2卸载实现NVMe-oF协议卸载,在target端,对NVMe、RDMA、TCP等协议进行硬件加速,在initiator端,通过PCIe的P2P机制在网络接口和其他PCIe设备之间构建快速通道。

存储接口的硬件加速:将virtio-blk接口硬件化,virtio-blk或者NVMe接口通过SPDK和远端的存储节点进行对接,也可以直接对接DPU上的存储设备。存储应用的卸载卸载SPDK,提供vhost-blk、vhost-nvme-vhost-scsi Target等组件,通过减少VM事件数目,实现对virtio-blk、 KernelNative NVMe、SCSI驱动的加速。Service Mesh卸载卸载服务之间的网络调用、限流、熔断和监控。

存储应用场景

存储应用场景通过DPU卸载存储,统一管控和运维存储资源,提供硬件级别的QoS服务,对服务器呈现虚拟的virtio-blk,虚拟的NVMe等PCIe存储设备,为服务器提供提供统一的存储设备,同时支持裸金属、虚拟和容器场景。DPU统一管理内置存储、DAS存储、SAN存储,卸载本地存储协议和网络存储协议,实现存储的统一管理。提供基于设备层面的数据加解密、数据完整性校验、数据压缩解压缩等功能。

安全应用场景

安全应用场景通过DPU实现基于信任根的安全启动,实现数据传输安全、存储安全。DPU卸载零侵入管控组件,提供从硬件到软件各个层次的安全保证。基于信任根的安全启动,可编程实现的分布式防火墙、数据传输安全、数据存储安全。DPU中的一次性非易失性存储区中存放公钥,作为安全启动的可信根计算基础。在DPU固件法布施,采用数字签名系统的私钥进行加密。安全启动时,采用逐级验签的方式,确保系统固件的安全性、可靠性。防火墙卸载,支持租户定义自身的防火墙过滤规则,保护面向互联网的工作负载和VM之间的流量,隔离租户本地网络与服务提供商的虚拟网络。

DPU支持虚拟机数据传输加密,通过卸载IPSec VPN,识别VM流量,触发IPSec IKE协议和目的端协商,完成身份认证和加密参数协商,建立隧道。DPU支持RPC调用数据传输加密,主要指基于TLS协议的HTTP,HTTP2协议。DPU卸载存储数据的加解密功能,通过识别租户远端云盘访问请求,启动存储加解密引擎,加密写入云盘的数据,解密从云端读取的数据,实现存储安全。

电信与边缘计算场景

在电信与边缘计算应用场景下,DPU应用于云RAN、虚拟化边缘网关、VNF加速、边缘微服务器等多个环节,可以实现UPF-U(用户数据面)卸载,保证QoS、时延和带宽,可以卸载N3接口(采用GTP-U协议进行用户数据的隧道传输),N4接口中传输SMF需要通过UPF接收或发送的报文,以及N6接口。UPF或者SDN控制器向DPU下发rte-flow规则实现UPF-U的硬件卸载。此外,为了满足UPF的管理要求,DPU通过开放自动化管控接口,实现了资源的统一调配。

小 结

DPU逐渐应用于云网络、存储、安全、电信与边缘计算等场景,不同应用场景对DPU的要求不尽相同,因而要给出通用化DPU的性能、功能比较非常困难。在实际的应用中,建议结合具体应用场景,针对特定方向进行比较,选择最优性价比的产品。

审核编辑:刘清

-

敏捷合成器的技术原理和应用场景2025-02-20 762

-

PCBA分析仪的技术原理和应用场景2024-12-04 5103

-

测试接收机的技术原理和应用场景2024-12-03 5195

-

OTA测试暗箱的技术原理和应用场景2024-11-14 3918

-

宽带放大器的技术原理和应用场景2024-11-13 3935

-

无线通信测试平台的技术原理和应用场景2024-11-06 3813

-

太阳膜测试仪的技术原理和应用场景2024-09-29 4851

-

智能IC卡测试设备的技术原理和应用场景2024-09-26 4322

-

IaaS+on+DPU(IoD)+下一代高性能算力底座技术白皮书2024-07-24 5379

-

DPU性能评测系统框架与测试流程2022-12-02 4140

-

大禹智芯宣布加入欧拉开源社区,助力构建DPU行业发展新生态2022-08-15 1253

-

DPU应用场景系列(二) 存储功能卸载2022-05-19 3695

-

业内首部白皮书《DPU技术白皮书》——中科院计算所主编2022-03-14 3801

-

MOS管的应用场景2018-11-14 6516

全部0条评论

快来发表一下你的评论吧 !