基于NMOS与PMOS晶体管构成的传输门讲解

模拟技术

描述

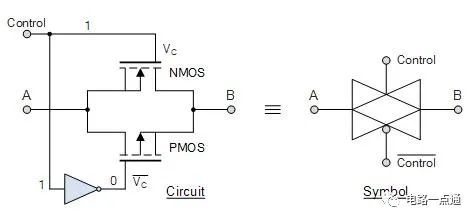

传输门是由外部施加的逻辑电平控制的NMOS和PMOS晶体管组成的双向开关。

传输门

将PMOS和NMOS器件并联连接在一起我们可以创建一个基本的双边CMOS开关,通常称为“传输门”。注意,传输门与传统的CMOS逻辑门完全不同,因为传输门是对称的,或双边的,即输入和输出是可互换的。

这个双边操作显示在下面的传输门符号中,它显示了两个指向相反方向的叠加三角形,表示两个信号方向。

CMOS传输门

两个MOS晶体管与NMOS和PMOS的栅极之间使用的反相器并联连接,以提供两个互补的控制电压。当输入控制信号V C 为低电平时,NMOS和PMOS晶体管都截止,开关打开。当V C 为高电平时,两个器件都被偏置为导通,开关闭合。

因此当V C <时,传输门充当“闭合”开关/ sub> = 1,而当V C = 0作为电压控制开关工作时,门用作“开路”开关。指示PMOS FET栅极的符号气泡。

传输门布尔表达式

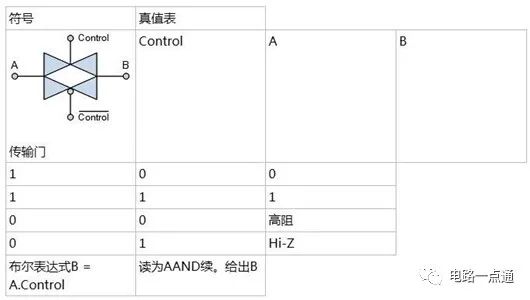

与传统逻辑门一样,我们可以使用真值来定义传输门的操作表和布尔表达式如下。

传输门真值表

从上面的真值表我们可以看出,B处的输出不仅依赖于输入A的逻辑电平,还依赖于存在的逻辑电平。控制输入。

因此,B的逻辑电平值被定义为A AND Control,它给出了传输门的布尔表达式:

B = A.Control

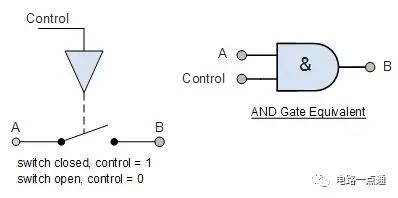

由于传输门的布尔表达式包含逻辑AND功能,因此可以使用标准的2输入AND门实现此操作,其中一个输入是数据输入,而另一个是控制输入,如图所示。

和门实现

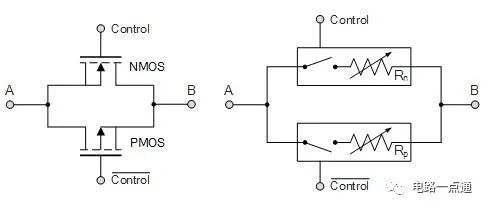

关于传输门,单个NMOS或其他两个要考虑的问题单个PMOS本身可以用作CMOS开关,但两个晶体管并联的组合具有一些优点。FET沟道是电阻性的,因此两个晶体管的导通电阻有效地并联连接。

作为FET导通电阻是栅极 - 源极电压的函数,V GS ,当一个晶体管由于栅极驱动而变得较不导通时,另一个晶体管接管并变得更导通。因此,两个导通电阻(低至2或3Ω)的组合值与单个开关晶体管本身的情况相比或多或少保持不变。

传输门导通电阻

小结

连接P沟道FET(PMOS)和N沟道FET(NMOS),我们可以创建一个固态开关,使用逻辑电平电压进行数字控制,通常称为“传输”门“。

传输门,(TG)是双向开关,其中任何一个端子都可以是输入或输出。除输入和输出端子外,传输门还有一个称为控制的第三个连接,其中控制输入将门的开关状态确定为开路或闭路(NO / NC)开关。

此输入通常由数字逻辑信号驱动,该信号在地(0V)和设定的直流电压(通常为VDD)之间切换。当控制输入为低电平(控制= 0)时,开关打开,当控制输入为高电平(控制= 1)时,开关闭合。

传输门的作用类似于电压控制开关,作为开关,CMOS传输门可用于切换通过全范围电压(从0V到V DD )的模拟和数字信号。

在单个栅极内将NMOS和PMOS晶体管组合在一起意味着NMOS晶体管将传输良好的逻辑“0”但是差的逻辑“1”,而PMOS晶体管传输良好的逻辑“1”但是逻辑“0”。因此,将NMOS晶体管与PMOS晶体管并联连接可提供单个双向开关,为单个输入逻辑电平控制的CMOS逻辑门提供高效的输出驱动能力。

-

一文详解NMOS与PMOS晶体管的区别2025-07-14 22191

-

什么是MOS管?NMOS、PMOS和三极管的区别2023-02-03 19846

-

NMOS管和PMOS管的定义2023-02-16 10447

-

NMOS管的工作原理及导通特性2023-02-21 27603

-

四种常用晶体管开关电路(2种NMOS,2种PMOS)2016-08-30 64331

-

PMOS管封装-详解PMOS管封装及PMOS管作用2018-11-27 5211

-

NMOS与PMOS晶体管开关电路2020-09-03 26814

-

PMOS晶体管工作原理 pmos晶体管的各个工作区域2023-02-11 19002

-

什么是传输门(模拟开关)2023-05-09 3269

-

为什么PMOS的闪烁噪声低于NMOS?2023-09-20 4315

-

pmos和nmos组成构成什么电路2023-12-07 7438

-

nmos与pmos符号区别2023-12-18 12544

-

如何设计一个nmos管和一个pmos管的开关电路2023-12-21 9977

-

NMOS晶体管和PMOS晶体管的区别2024-09-13 9360

-

PMOS晶体管的饱和状态2024-09-14 4918

全部0条评论

快来发表一下你的评论吧 !