如何对传统的非DFX设计进行调试呢?

描述

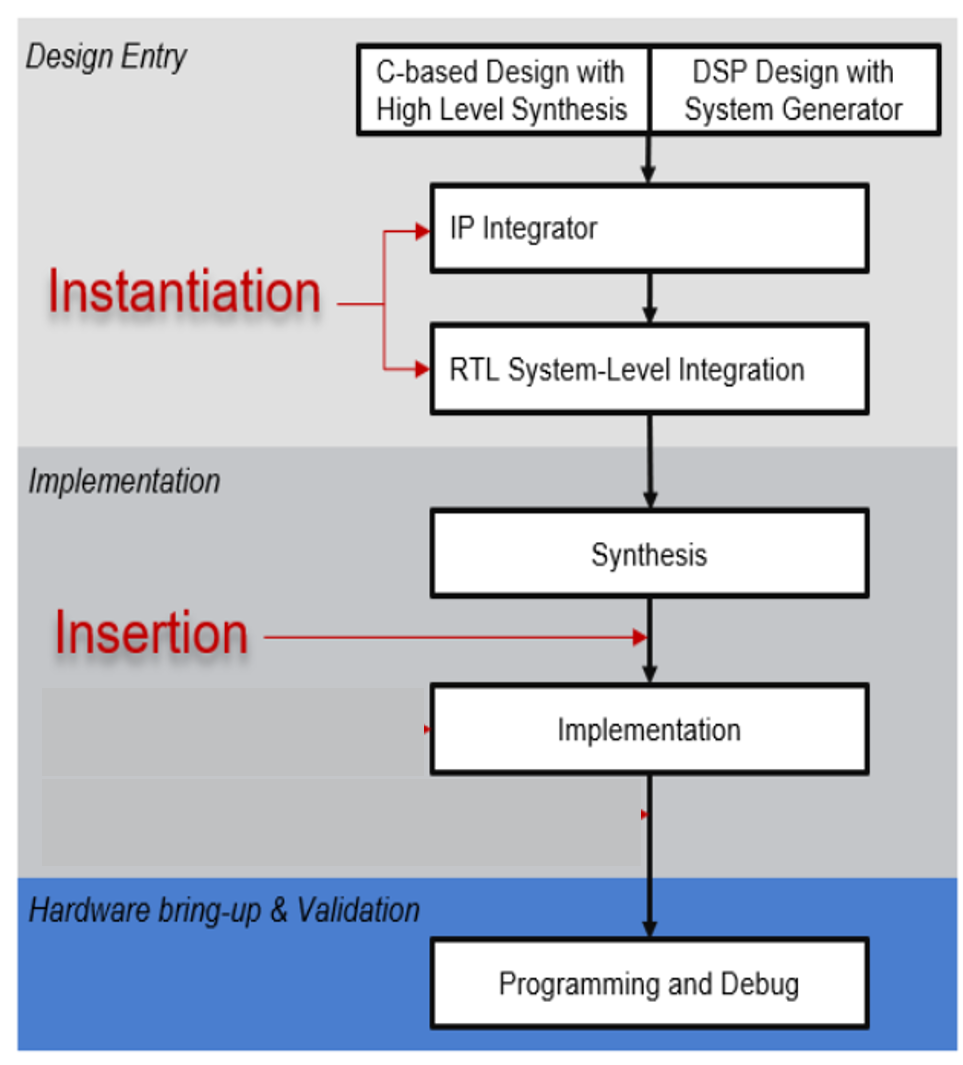

对传统的非DFX设计进行调试时,一个重要环节是插入ILA(Integrated Logic Analyzer,集成逻辑分析仪)。可以采用如下图所示的两种方式。方式1是实例化方式,即在RTL代码或者BD中实例化ILA。如果图中红色字体“Instantiation”所示。方式2是网表插入方式,即在综合后的网表中插入ILA。

不难看出方式1是在综合之前完成,而方式2则是在综合之后完成。方式1需要手工例化ILA,同时将待测网线连接到ILA的测试端口,这个过程稍显繁琐,尤其是待测信号需要穿越多个层次到达ILA所在层次时,但也确保了待测信号能够百分之百被观测到(不会被工具优化掉)。方式2更为自动化,在综合后的网表中找到待测信号将其标记为debug(本质上是将其属性mark_debug设置为true)。但有可能出现待测信号名字发生改变或者彻底被优化掉而无法找到的情形。

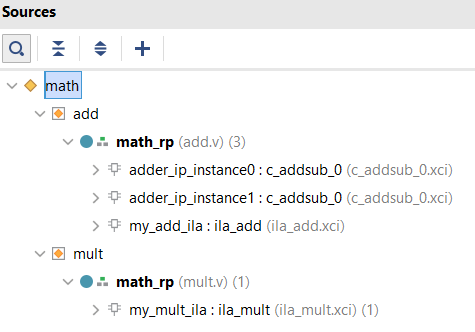

对于DFX设计,那么就只能使用实例化方式插入ILA。但即便如此,仍有一些特殊之处。为便于说明,我们看一个实际案例。这个DFX设计中的RP(Reconfigurable Partition)为math,该RP下有两个RM(ReconfigurableModule),分别为add和mult,如下图所示。

每个RM中均包含一个ILA。这个ILA无论参数配置是否一致,都要分别调用ILA IP Core,单独例化。这是DFX设计所要求的,即每个IP都要以唯一的方式存在于RM中。

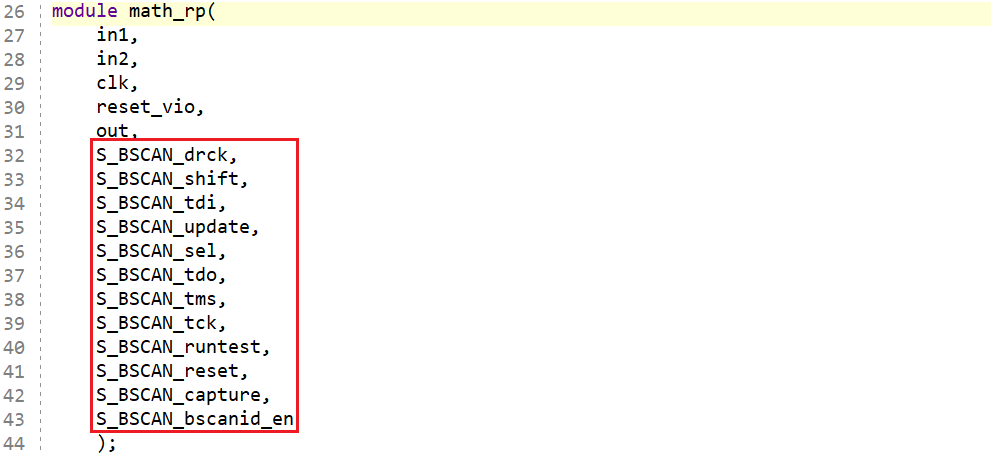

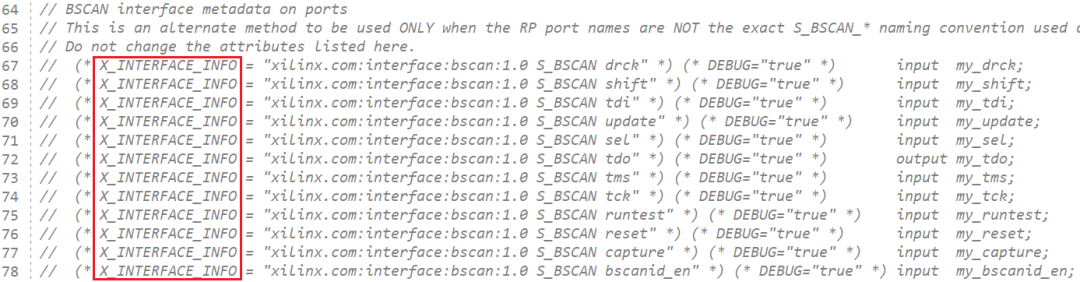

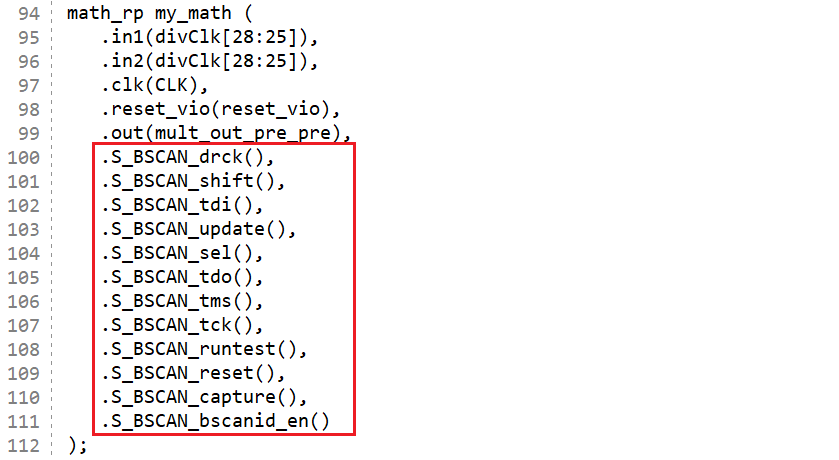

到这里我们看到的例化ILA的方式与传统的非DFX设计并没有什么不同。但是在每个RM的顶层,需要添加12个BSCAN端口,如下图所示。这12个端口最终会与dbg_hub相连。这里要求端口名字必须与图中红色方框内的名字完全一致,如果不一致,则要通过属性X_INTERFACE_INFO设定。

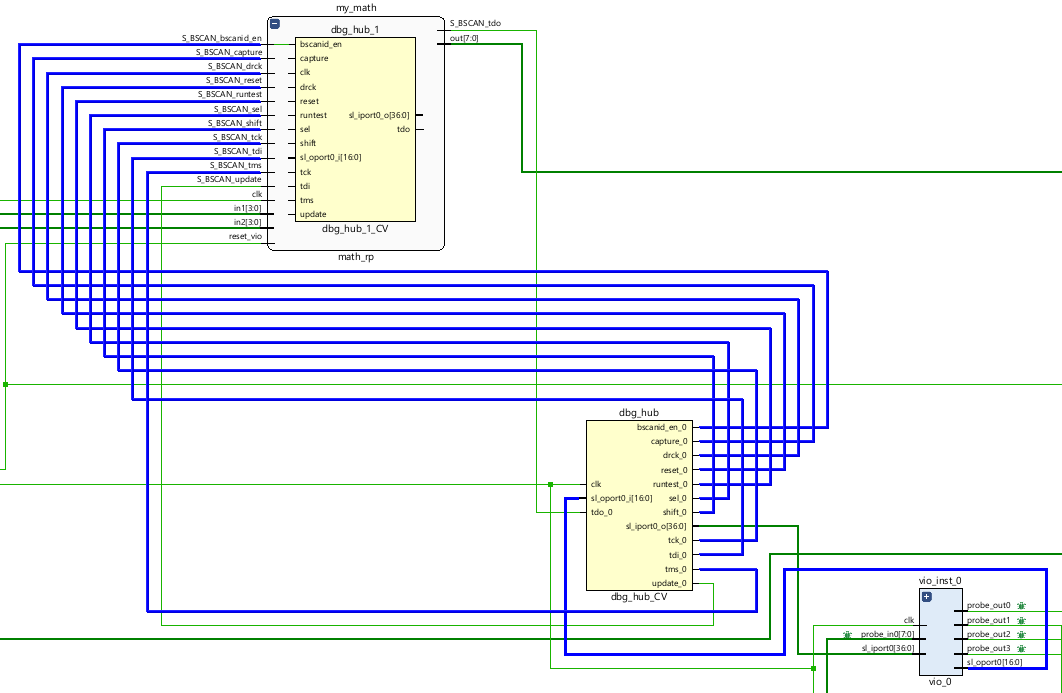

在整个设计的顶层,对RM进行实例化时,这12个端口的端口映射为空,如下图所示,如果使用的是VHDL,端口映射内填写open。

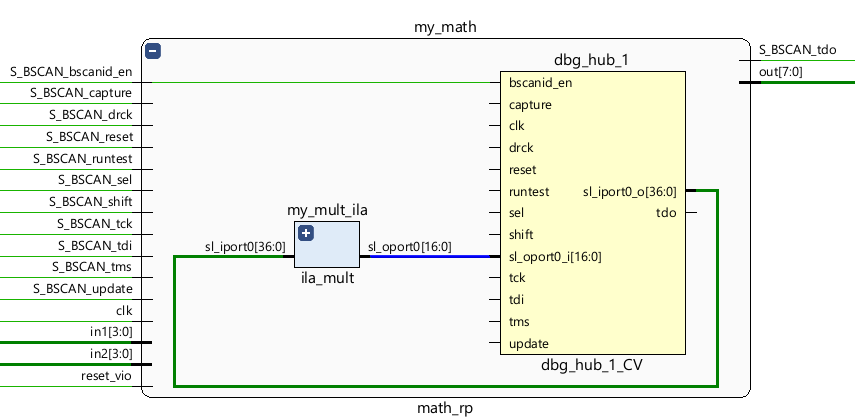

在综合阶段生成的网表中,dbg_hub是以黑盒子的形式存在,在设计顶层和RM内分别有一个dbg_hub,如下图所示。dbg_hub与ILA的连接关系由工具自动处理,无需人工干预。

在综合阶段生成的网表中,dbg_hub是以黑盒子的形式存在,在设计顶层和RM内分别有一个dbg_hub,如下图所示。dbg_hub与ILA的连接关系由工具自动处理,无需人工干预。

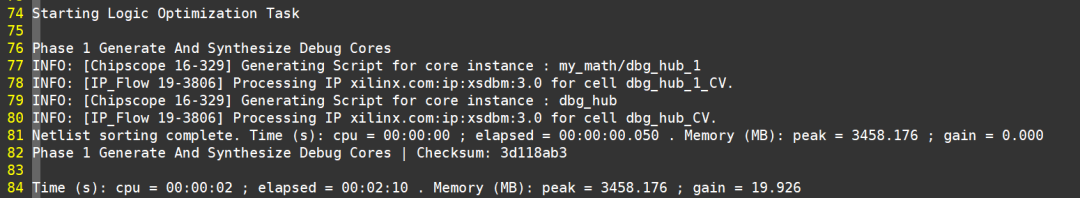

实际上,在opt_design阶段,Vivado会自动生成dbg_hub,这可在runme.log文件中查看到,如下图所示。

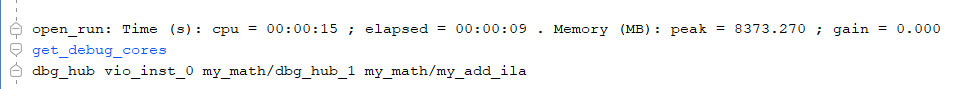

打开布线后的网表文件,执行命令get_debug_cores,可以看到当前网表中的ILA、VIO和dbg_hub。如下图所示,设计顶层和RM中各有一个dbg_hub。

如果某个RM中并没有使用ILA或VIO,而其他RM中至少有一个使用了ILA或VIO,那么所有的RM都要列出上文提到的12个BSCAN端口,以确保所有RM接口的一致性。

审核编辑:刘清

-

采用UltraScale/UltraScale+芯片的DFX设计注意事项2024-01-18 2179

-

DFX可制造性设计与组装技术2023-12-11 1735

-

DFX设计如何分析2023-11-09 1990

-

什么是DFX技术?DFX设计一定要执行设计规则检查吗?2023-09-21 10268

-

屏蔽网线和非屏蔽网线如何进行选择呢2022-12-26 5745

-

HarmonyOS对DFX能力的要求2021-12-17 5349

-

简述DFX理念与产品研发(一)2021-09-28 4315

-

对传统的CML动态比较器的MC仿真总结是什么?2021-06-22 2327

-

互联网经济对传统会计的冲击及思考2021-06-15 979

-

网络、数字技术对传统音频的影响及对策是什么?2021-06-07 2127

-

如何对传统应用进行容器化改造2020-04-24 1701

-

allegro软件的绝对传输延迟是什么,绝对传输延迟应该怎么设置呢?2020-04-15 4985

-

PCB板DFX工艺性要求2016-07-26 1524

全部0条评论

快来发表一下你的评论吧 !