基于GD32F303的高频DC/DC变换器解决方案

描述

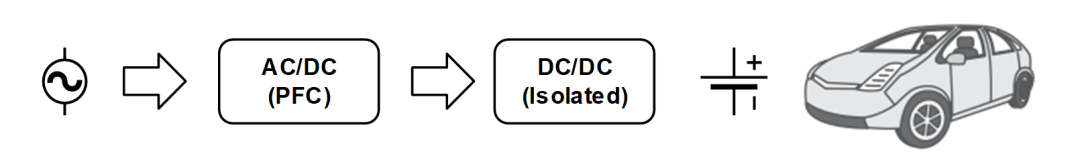

车载充电器(OBC)是电动汽车和混合动力汽车的重要组成部分(HEV)。OBC通常由一个AC/DC(功率因数校正电路)和一个隔离式DC/DC转换器,如下图所示:

典型两级式OBC架构

随着电池容量的增加,OBC需要设计更高的功率。与OBC的功率容量越来越大相反的是,由于车内空间和冷却能力有限,因此功率密度和效率等规格也越来越高。高效率和高功率密度成为OBC的两个关键要求。宽带隙(WBG)功率器件的技术发展和应用,例如碳化硅(SiC)器件和氮化镓(GaN)器件,因其更高的开关速度、更低的开关损耗以及更低的导通电阻温度依赖性,在很多场合已经成为传统硅(Si)器件的优越替代品。

系统简介

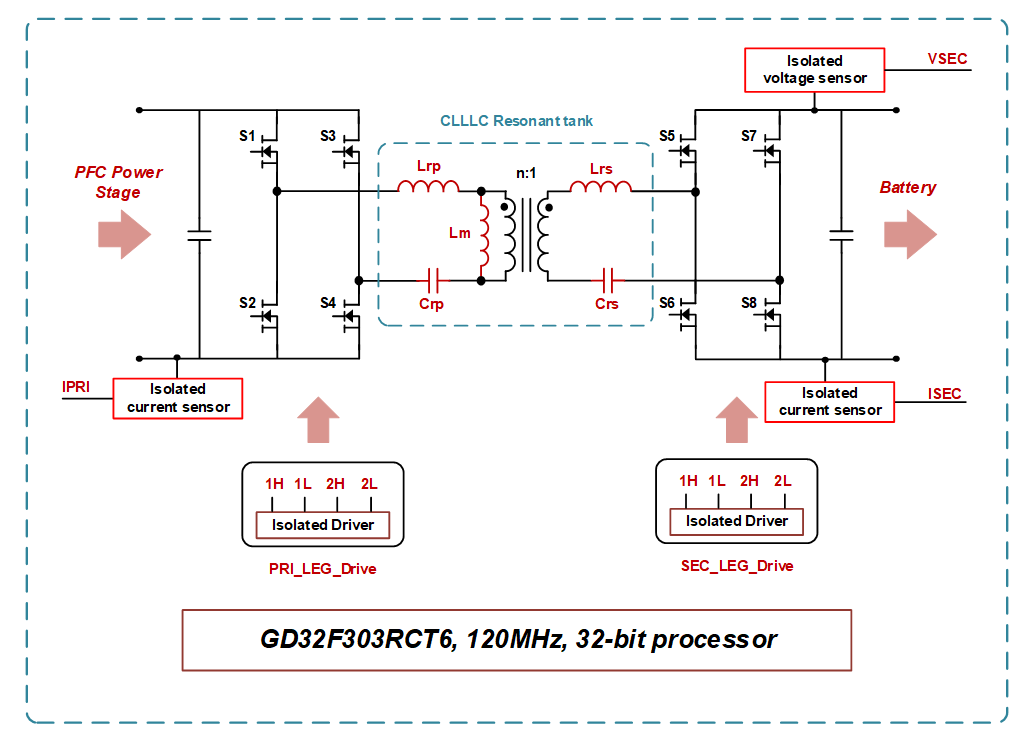

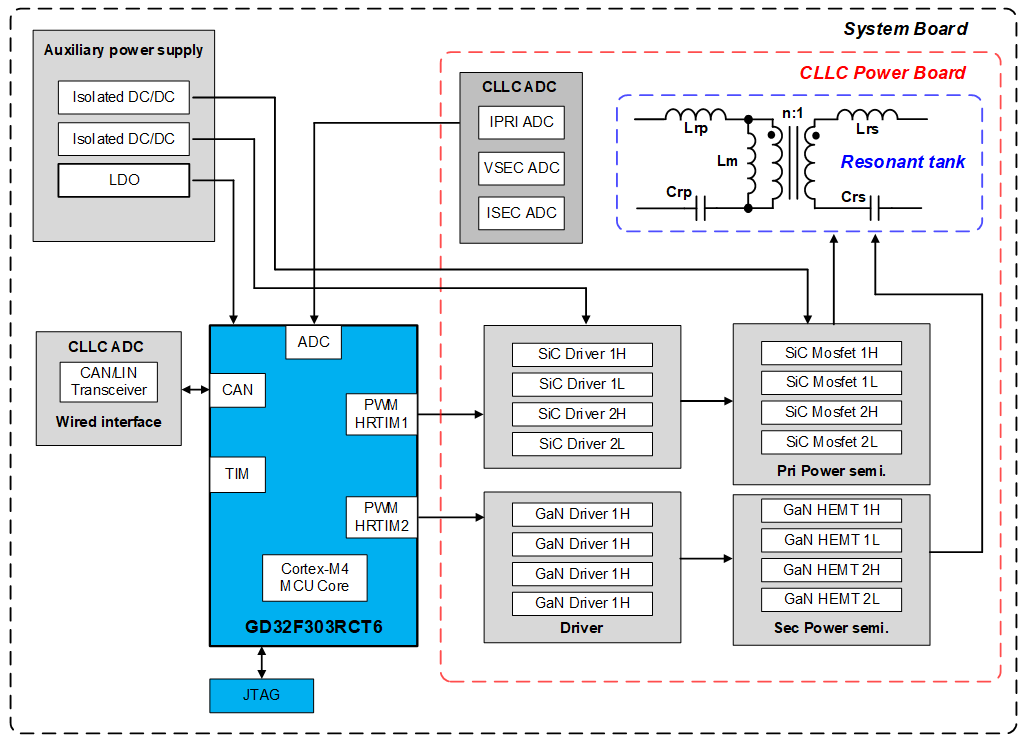

CLLC(电容-电感-变压器-电感-电容)电路拓扑,具有对称谐振腔和软开关特性以及更高频率工作的能力,是实现OBC高效、高功率密度的良好选择。CLLC拓扑的设计、控制和实施架构,如下图所示:

CLLC隔离DC/DC拓扑架构

采用GD32F303RCT6微控制器:得益于HRPWM定时与ADC采样的高精度,使得CLLC将设计频率提高到500kHz在数字控制的可实现性上,变成了可能,从而为整机系统的高功率密度和高效率综合优化提供了控制保障

GD32F303精准的PWM边沿控制:采用无传感器的同步整流控制技术,可进一步减少整机的硬件成本。

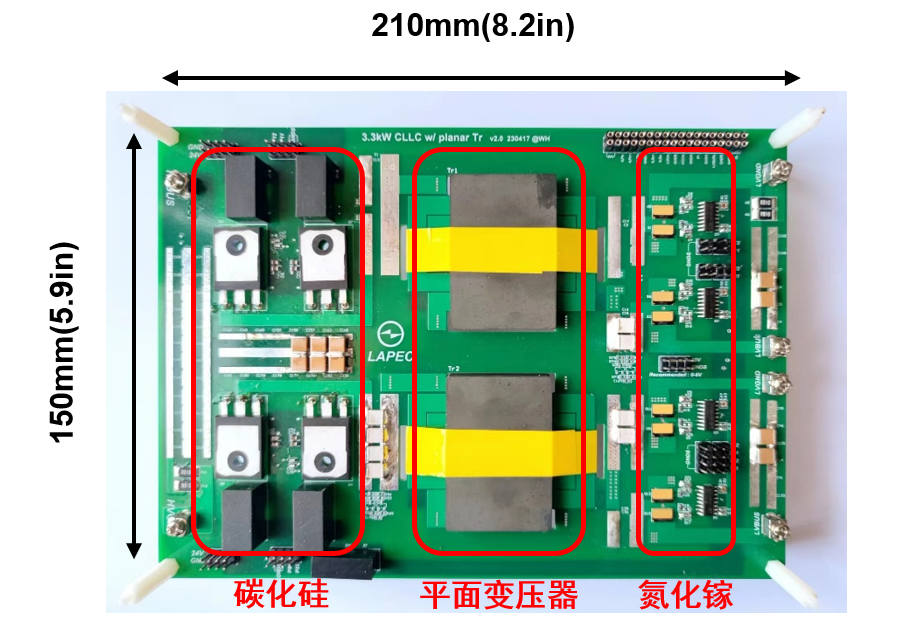

独有专利支撑的平面磁集成优化方案:有效提升了整机系统效率,同时磁性元件采用PCB绕组减少了人工绕制变压器的人力成本。

系统关键参数规格列下表所示:

| 参数 | 规格 |

| 原边电压 (Vprim) | 500V-840V DC |

| 副边电压 (Vsec) | 250V-450V DC |

| 功率 (Po) | 3.3kW Max |

| 输出电流 (Iout) | 11A Max |

| 效率 | Peak 97.5% |

| PWM开关频率 (fs) | 额定500kHz (400kHz-600kHz) |

但是与传统的移相全桥、不对称LLC拓扑相比,CLLC谐振变换器存在两个谐振电感与一个变压器,占据整个车载充电器体积的25%以上,这严重影响了变换器功率密度,因此减小磁性元件的体积成为提高车载充电器功率密度的一种重要方法,前述提高开关频率可以有效减小磁性元件的体积,但由于磁芯材料和功率器件限制,通过无限制的抬升开关频率来减小磁性元件体积的做法并不可取。

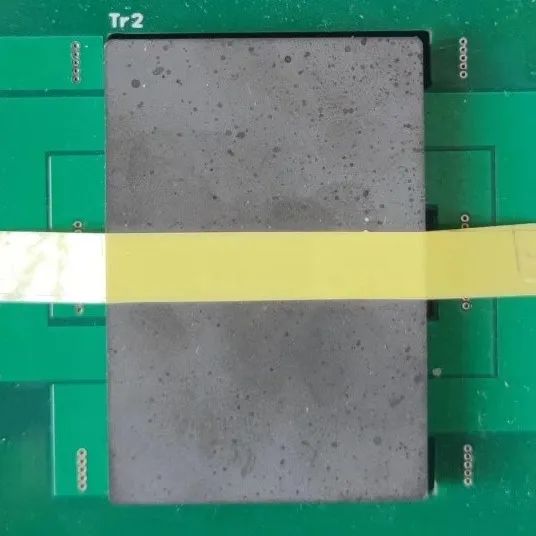

另一个提高功率密度的方法是使用磁集成技术,将同一个变换器中的多个磁性元件以电磁场基本理论为约束集成在一付磁芯上,如在CLLC拓扑上,将原边电感、变压器、副边电感集成至一个磁芯中,同时结合宽禁带器件的使用,可以将整体设计体积压缩至一个非常可观的体积内。

绕线式与平面集成变压器示意图

而在效率的提升方面,除了使用性能更好的宽禁带器件外,磁性元件的损耗优化也是一个突破方向,使用PCB铜箔作为绕组配合平面变压器的使用,相对传统利兹线绕制的变压器在损耗、散热性能上均存在较大优势,且自定义设计的磁芯在各种体积要求的工况均能满足设计要求。

3.3kW双向CLLC实验样机

无传感器同步整流策略

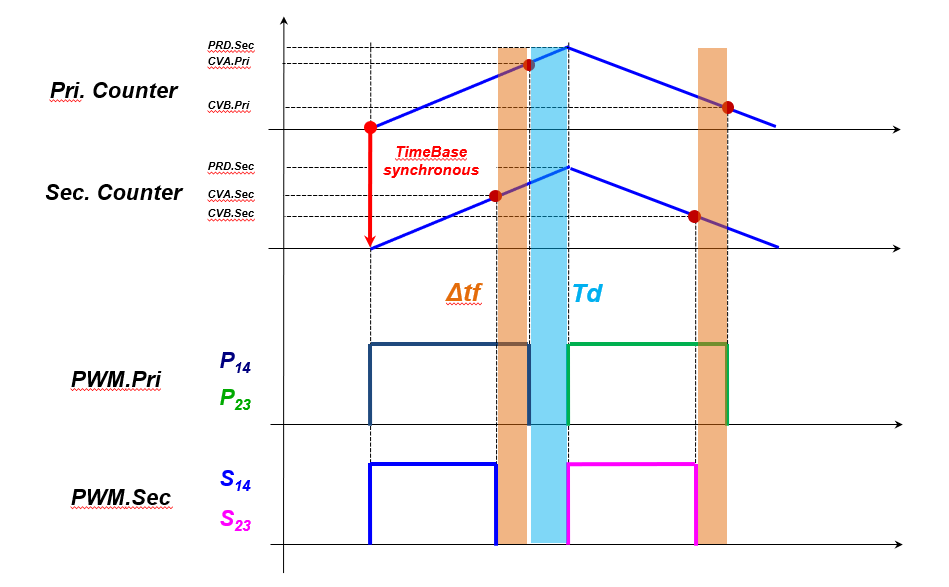

原副边调制策略分别为:原边驱动信号频率来自闭环控制的计算结果,控制调频实现对输出电压的控制;同步整流控制策略为:副边同步整流信号的上升沿与原边信号一致,下降沿由控制器实时计算出的副边管导通时间控制。

双向CLLC正向传输功率同步整流策略

使用此方法同步整流,仅需借助控制器本身对PWM上升沿和下降沿的位置精准控制,能省去传统基于电压或电流检测方案进行的同步整流的检测芯片。

软件系统框架

系统软硬件配合框图

2个HRPWM高分辨率PWM中断,最大定时频率600kHz。要求具有精准的对上升沿和下降沿的控制。

8路12位ADC采样,分别用于采样输入电压、输入电流、原边谐振电流、输出电压、输出电流、副边谐振电流,原边谐振电容电压、副边谐振电容电压。

2个普通定时器TIMER,用于控制逻辑定时。

CAN总线通信用于系统状态监测。

审核编辑:汤梓红

-

【GD32 MCU 移植教程】2、从 GD32F303 移植到 GD32F5032024-08-31 3817

-

GD32F303为什么启动慢?2024-02-22 3354

-

基于GD32F303的高频DC/DC变换器解决方案2023-11-06 1875

-

GD32F303固件库开发2023-07-27 2825

-

GD32F303固件库开发(15)----外部中断EXTI2023-07-26 3344

-

AN029 GD32F103程序在GD32F303和GD32F403芯片上运行DSP2023-02-27 903

-

兆易创新GD32F303 ARM 32位微控制器2022-03-03 1586

-

DC-DC变换器的基本电路2021-11-17 4087

-

DC-DC变换器解决方案2021-11-16 1078

-

【GD32F303】星空派介绍2021-09-11 5430

-

利用AP的高频推挽DC-DC变换器设计方案2018-09-29 3739

-

选择最佳DC/DC变换器的要点及途径2014-06-05 3658

-

DC/AC高频变换器电路图2009-07-17 3863

全部0条评论

快来发表一下你的评论吧 !