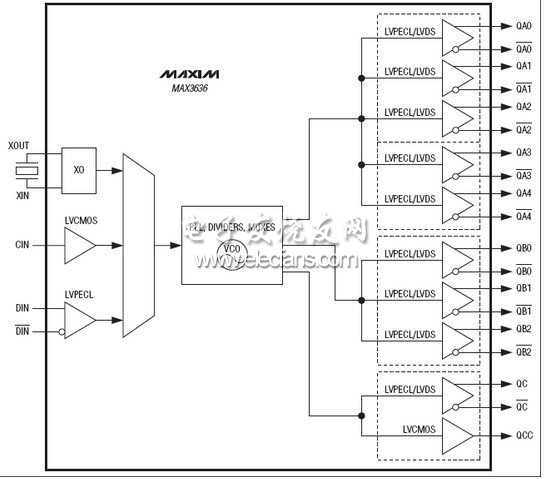

MAX3636宽频率范围可编程时钟发生器

芯片引脚图

728人已加入

描述

MAX3636是一个高度灵活,高精度锁相环(PLL)时钟发生器为下一代网络设备的要求低抖动时钟发生器和强大的高速数据传输的分布进行了优化。优异的电源噪声抑制,以及引脚可编程的LVDS / LVPECL输出接口。 MAX3636提供9个差分输出和一路LVCMOS输出。每个输出的频率和输出接口,可单独编程,使这一设备系统板上的多个晶体振荡器和时钟分配IC的理想替代品,节约成本和空间。

这3.3V IC采用7mm x 7mm,48引脚TQFN封装,从-40 ° C至+85 ° C。

关键特性

输入

水晶接口:18MHz的到33.5MHz

LVCMOS输入:15MHz的至160MHz

15MHz到350MHz的差分输入:

输出

LVCMOS输出:可达160MHz

LVPECL/ LVDS输出:可达800MHz

三个人的输出银行

引脚可编程分频器

引脚可编程输出接口

VCO调谐范围宽(3.60GHz至4.025GHz)

低相位抖动

0.34psRMS(12kHz至20MHz)

0.14psRMS(1.875MHz到20MHz)

优异的电源噪声抑制

-40° C至+85° C工作温度范围

3.3V电源

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入剖析RC2121xA:高性能汽车可编程时钟发生器的卓越之选2025-12-29 55

-

MAX9491工厂可编程、单PLL时钟发生器技术手册2025-04-27 743

-

LMH1983高度集成的可编程音频/视频(AV)时钟发生器数据表2024-08-21 328

-

具有14个可编程输出的LMK03806超低抖动时钟发生器数据表2024-08-20 384

-

CY25200可编程时钟发生器英文手册2023-02-14 479

-

低抖动高精度时钟发生器MAX3625B相关资料分享2021-05-18 1106

-

可编程音频时钟发生器MAX9485相关资料分享2021-04-02 1714

-

AK8140A可编程多时钟发生器评估板简介2020-07-27 2289

-

IDT推出其低功率可编程时钟发生器2017-09-28 9015

-

基于lmk03806的高性能可编程时钟发生器的设计与fpga实现 毕...2013-05-03 3372

-

DS1086 EconOscillator 可编程时钟发生器2012-03-22 2997

-

首款可编程时钟发生器的便携音频子系统发布2011-08-10 1248

-

高精度时钟发生器MAX945x的元件选择和性能测试2009-04-22 1340

-

MAX9489/MAX9471多输出时钟发生器构建集成时钟源2008-10-04 1178

全部0条评论

快来发表一下你的评论吧 !