PCB中缝合过孔的基础知识

PCB设计

描述

缝合过孔是您经常看到的分布在PCB表层周围的东西。如果正确使用敷铜,就能理想地计算出适当的过孔间距缝合,以便过孔阵列抑制串扰/干扰。另一种选择是用作层间的多个并联连接,可以提供低电阻和阻抗,因此它们可以在直流或交流中提供高电流。

在本指南中,我将介绍缝合过孔的一些标准用途以及何时应在PCB中使用它们。PCB设计的这一领域在一些设计人员中可能会引起争议,因为它与敷铜有关,而大多数设计通常不需要敷铜。无论您对敷铜有何感受,缝合过孔在低频和高频的PCB中都有重要的用途。

PCB中缝合过孔的基础知识

缝合过孔是简单的结构:它们是周期性的过孔阵列,通常在PCB叠层上接地。通过这种方式,它们可以在多层的接地网之间建立连接。请注意,过孔阵列的一种用法涉及跨层的电源连接(见下文)。这些结构在RF设计中也有重要用途,这有时会导致缝合过孔被误用。

让我们更详细地看一下其中的每种用途:

典型用法:连接接地

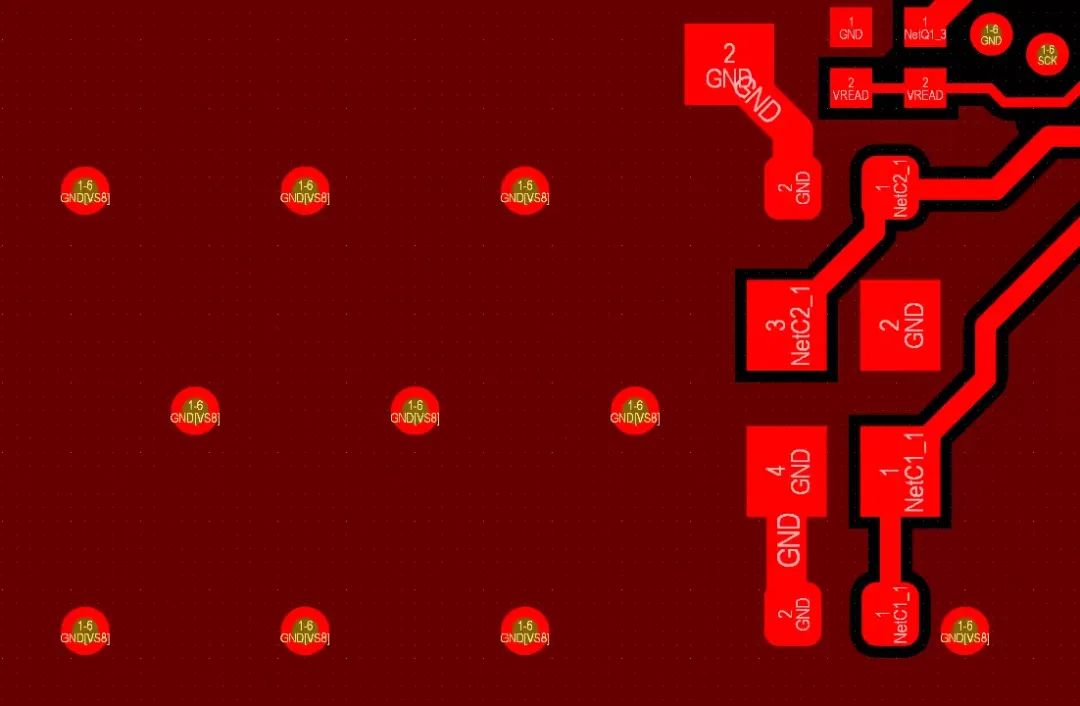

缝合过孔的标准用法是跨多层连接接地。在多层PCB中,通常会有一个以上的铜区域被分配到同一个接地网。缝合过孔是一种有用的工具,可用于将这些连接到任何位置,并确保沿PCB中参考平面传播的任何返回电流的阻抗尽可能小。

请注意,没有要求使用周期性缝合过孔来跨接地进行这些连接。地线确实需要在某处连接,而且多个连接可能更合适,以确保回流路径容易导航到电源回流点。

通过过孔进行层过渡

这是连接到GND的缝合过孔真正显示其价值的一个领域。数字电路和RF电路中的层转换需要有清晰的接地参考,以控制信号沿PCB互连的传播。进行层转换时,缝合过孔阵列中附近的过孔可以执行与走线下方接地层相同的功能。

通常,如果您在PCB中放置缝合过孔阵列,则在通过信号过孔的层过渡附近可能会有一个缝合过孔。在某些情况下,这可能可以正常工作,而且您可能不必担心过孔过渡区域内的噪声排放或对噪声的敏感性。在信号过孔附近存在接地缝合过孔应该足以抑制噪声,特别是对于慢速GPIO、I2C、UART或其他慢速数字协议(同样适用于低频模拟)。

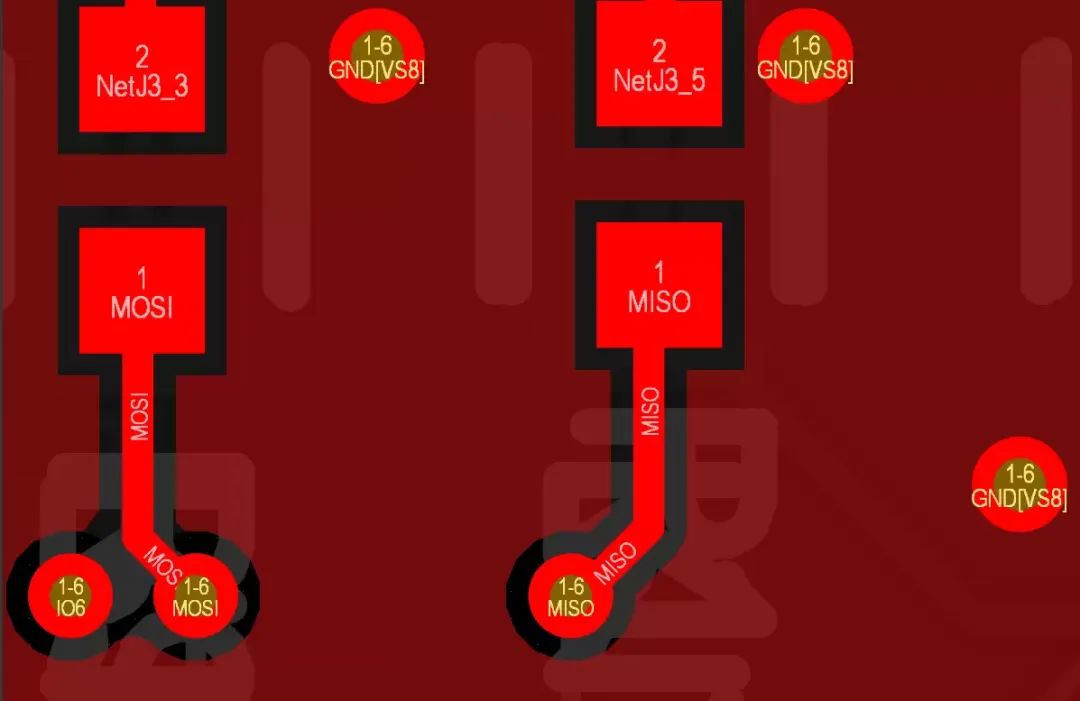

这些缝合过孔在自动应用后恰好落在这些MISO和MOSI线附近,它们会提供足够紧密的接地回路吗?

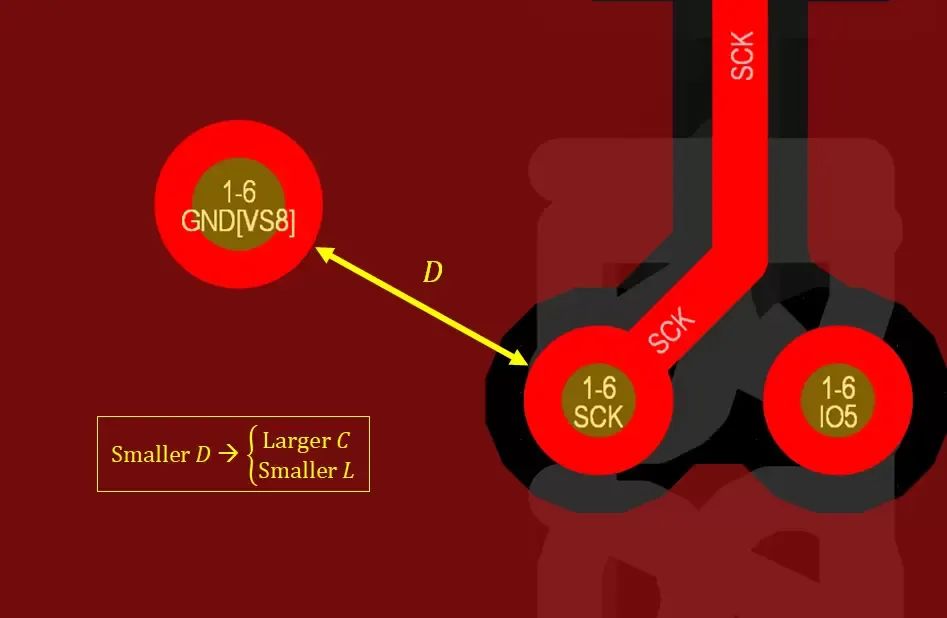

对于高速数字和RF,情况有所不同,您需要在信号过孔附近有一个专门设计的缝合过孔阵列。通过阵列进行缝合的目的是为沿着缝合过孔边缘感应的回流提供低阻抗路径。在这些过渡中放置缝合过孔的另一个原因是将包含此信号的电磁场限制在由缝合过孔界定的过孔结构内。

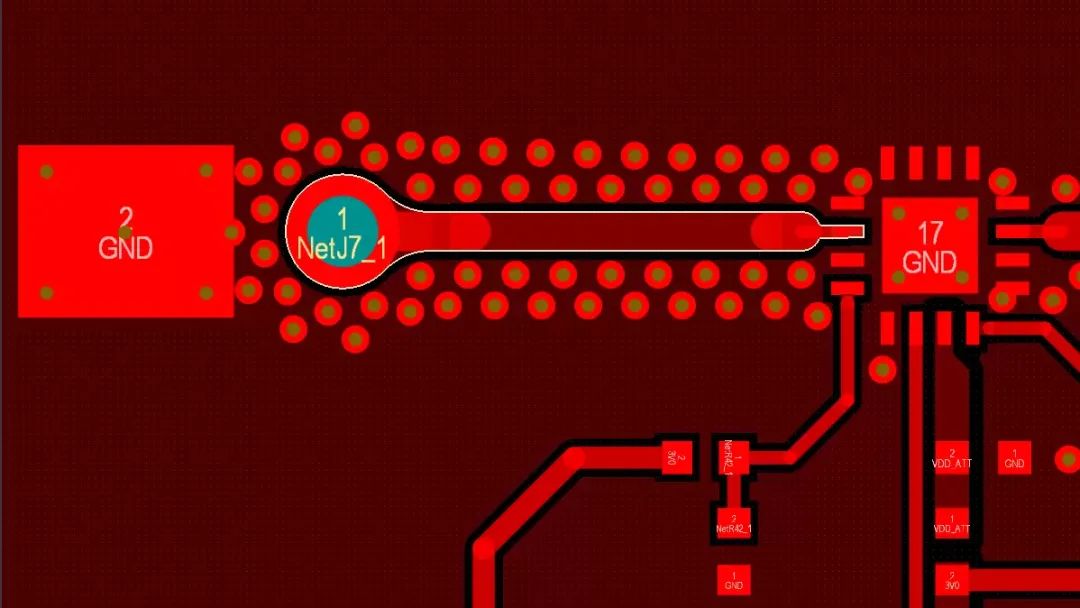

此电路板的背面有一个连接器安装,然后将信号传输到顶层(此处以红色显示)

这种情况下的噪声抑制机制有时称为“屏蔽”,就好像过孔可以防止电磁波耦合到受害互连中。这在某种程度上是正确的。使缝合过孔结构靠近信号过孔,可通过两种方式降低噪声:

过孔区域的回路电感较低,因为过孔离地较近。

离地更近会导致信号过孔/接地过孔在过孔沿途的总电容中占主导地位。

第二点等同于通过使接地层更接近信号走线来降低寄生电容。我在本文中展示了这如何减少与其他信号网络的寄生电容耦合,预计这里会出现同样的结果。

缝合过孔和反焊盘影响过孔阻抗

在上一节中修改电容和电感的真正结果是,在层过渡中放置缝合过孔将决定过孔阻抗。一个相关的部分是反焊盘,理想情况下它应该与缝合过孔相交,因此它们将一起修改阻抗。由于缝合过孔排列和层过渡周围反焊盘尺寸的存在,大多数过孔阻抗计算器完全无法计算实际的过孔阻抗。

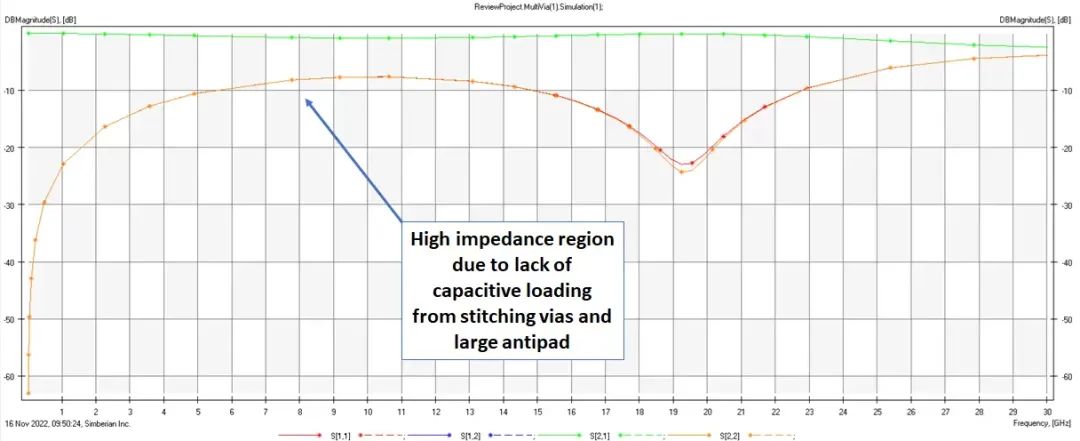

尽管穿过接地层的缝合过孔和反焊盘确实会影响阻抗,但在频率超过约3-5GHz之前,过孔的输入阻抗不会明显偏离50欧姆(或约100欧姆差分)。在低频时,无需担心有多少缝合过孔和反焊盘尺寸会影响过孔阻抗;您很可能不会注意到任何影响,因为过孔在电力方面会非常短。在约5GHz以上,这一点非常重要,因为错误放置的缝合过孔和大型反焊盘将无法提供足够的电容负载,从而导致阻抗达到约100欧姆的电感过孔转换。下面显示了一个没有缝合过孔和大型反焊盘的过孔过渡示例的S参数。

S11图显示了由于缺少缝合过孔和大型反焊盘而导致的电容负载不足的影响,我们可以清楚地看到过孔转换不能支持~3GHz以上的信号带宽

在这种情况下,缝合过孔对中档频率下差分对电容负载的影响并不是最强的。当信号过孔间距较大时,缝合过孔对信号过孔阻抗的影响较大。当信号过孔靠得更近时,反焊盘是过孔阻抗的更大决定因素。当信号过孔互相靠近并且反焊盘较小时,您可能不会注意到缝合过孔的任何影响。

缝合过孔提供屏蔽吗?

简短的回答为“是”,但仅限于某些频率。当以提供屏蔽为目的使用时,设计人员有可能只是猜测过孔之间所需的间距。在某些情况下,我们所说的波导屏蔽最好称为电场约束。不管您想怎么称呼它,缝合过孔都可以阻止电磁波传播到某个最大频率。

对于要抑制的给定频率,过孔之间的间距应约为:

这种专门用于阻挡电磁波传播的缝合过孔的间距要求与用于将波限制在PCB上的波导内的要求相同。

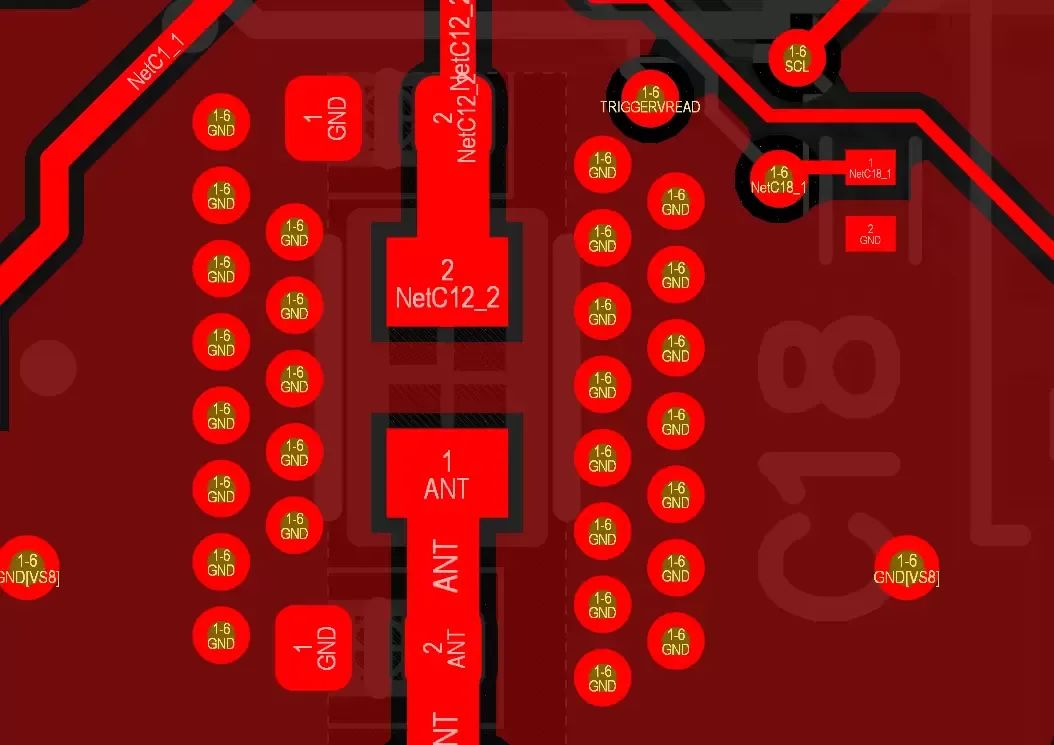

用作天线馈线的接地共面波导示例如下所示。在此示例中,间距为20密耳,根据上述等式,这适用于屏蔽高达43GHz的频率。如果附近有高速信号传输,我们可以期待沿着这条馈线的高屏蔽效果,这将有助于抑制进入RF线路的串扰。

带缝合过孔的共面波导

这里需要注意的是,缝合过孔并不是解决噪声的灵丹妙药,它们不会给您提供消除最佳布线实践的借口。即使您以上述方式使用了缝合过孔,仍应为RF电路板实践良好的布局和布线策略。

电源缝合过孔

当用于电源系统的PCB布局时,缝合过孔通常不会以大间距的典型排列方式布置。事实上,在这些设计中,您可能根本看不到它们用于大型接地敷铜区。然而,缝合过孔阵列可用于在电源网上创建低电阻层过渡。这将允许过孔在层间以低损耗传输大量电流。

来自稳压器电路的电源网络多边形上的8个过孔阵列示例

传输一定量的电流需要多少个缝合过孔?这取决于典型过孔的直流电阻。对于典型的过孔钻孔直径和焊盘尺寸(10/20密耳)以及1密耳的孔壁镀层厚度,过孔电阻约为1.5mOhm,热阻约为180°C/W。如果您试图通过此过孔引入20A直流电,您将消耗600mW的功率,并且您可以预期过孔的温度会增加108°C。

为了将温升保持在可接受的范围内,我们希望在一个阵列中使用多个过孔。如果我们并联使用10个这样的过孔,那么每个过孔将承载2 A DC,并且每个过孔(以及整个阵列)的预期温升将为1.08°C。这应该显示如何使用温升目标来确定缝合过孔数量的限制。

自动缝合过孔布置

如果我们注意到缝合过孔的布置涉及在电路板周围定位和放置大量过孔,并且具有精确的间距,那么这对于大多数CAD工具来说可能很难做到。更简单的CAD工具会强制手动放置缝合过孔,然后可能会在电路板周围复制粘贴每一行/每一列以形成阵列。

Altium Designer在PCB编辑器中包含了一个简单的实用程序,可以按照用户定义的尺寸和间距来放置缝合过孔。您可以通过选择过孔模板或设置自定义过孔尺寸和层过渡来放置缝合过孔。您可以从PCB编辑器内的“工具”菜单访问此功能。阅读更多有关此功能的文档。

那么,有没有客观上“正确”的方式来使用缝合过孔呢?答案有时并不那么明确。我已经展示了一些实例,其中缝合过孔阵列用于非常特定的目的:

如果您只需要接地(无高速/RF),缝合过孔很方便但并非必需

如果提供跨层参考,缝合过孔也方便低速信号以最大限度地减少EMI

如果提供电力,间隔紧密的过孔可以提供高电流,同时最大限度地减少温度升高

对于高速信号的转换,您不能依靠随机放置的缝合过孔来保证信号的完整性

这使得屏蔽成为缝合过孔的尺寸、间距和位置方面的突出问题。要了解更多信息,请阅读这篇关于PCB布局中覆铜的文章,了解缝合过孔对噪声耦合和EMI的一些影响。

当您需要使用最佳CAD功能和自动化工具来构建PCB时,请使用Altium Designer中的全套产品设计工具。当设计完成并准备将文件递交给制造商时,Altium 365平台可以轻松地协作并共享您的项目。

审核编辑:汤梓红

-

PCB绘制基础知识2025-01-21 574

-

PCB过孔设计的基础知识2024-11-05 3118

-

PCB过孔的基础知识与设计验证2024-01-05 3561

-

PCB中缝合过孔的基础知识2023-08-11 5423

-

PCB应变测试基础知识2022-02-18 2312

-

PCB的基础知识详细介绍2020-11-25 2860

-

PCB设计缝合地过孔的添加步骤2020-10-09 15116

-

Altium Designer19 添加缝合过孔操作2019-10-29 10705

-

为什么AD9中找不到缝合过孔?2019-09-19 3969

-

PCB过孔的设计需要注意什么?PCB过孔和背钻的技术知识详细说明2019-09-14 7524

-

如何解决Altium放置缝合过孔不被卡的问题?2019-09-04 3416

-

过孔结构的基础知识与差分过孔的设计与实现2017-10-27 1315

-

PCB基础知识2016-07-26 789

全部0条评论

快来发表一下你的评论吧 !