半导体制造工艺解析

制造/封装

描述

WCMP是电子束检测应用最重要的一层,这一层的功能主要体现在:可以使工程师遇到器件的漏电和接触不良问题。EBI的应用可以帮助提升成品率,减少半导体ict技术开发的周期,并缩短提高成品率所需的时间。

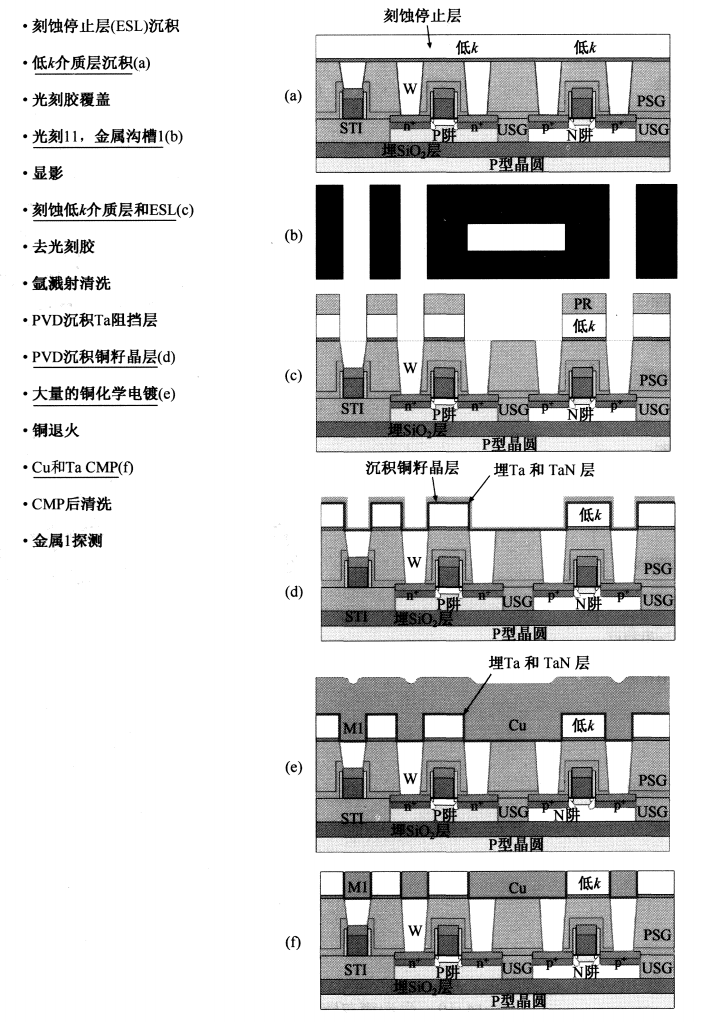

下图显示了金属1单镶嵌工艺铜互连技术。硅氮化碳(SiCN)是一种致密材料,它可以用于代替氮化硅作为阻隔层防止铜扩散,在铜互连工艺中也可以作为刻蚀停止层(ESL)。与硅氮化物k=7~8)相比,SiCN具有较低的电介质常数k=4〜5),因此,使用SiCN可以降低ILD层的整体介质常数。最常用的低%电介质材料是PECVD SiCOH,它被广泛用于互连工艺。阻挡层和铜籽晶层使用PVDI艺沉积,通常使用离化金属的等离子体提高底部的覆盖。由于低k电介质的机械强度比硅酸盐玻璃小,因此具有低k电介质的铜CMP过程向下的研磨力要低于使用USG或FSG材料。金属1 CMP后,测试结构中首先进行电特性测量。微小的探针接触测试结构的探针接触区,并利用电压或电流测试器件的电性能。为了避免铜氧化降低成品率,铜CMP和覆盖层沉积之间有一个时间限制,所以利用光学检测和电子束检测系统进行缺陷的检测通常在覆盖层沉积后进行。

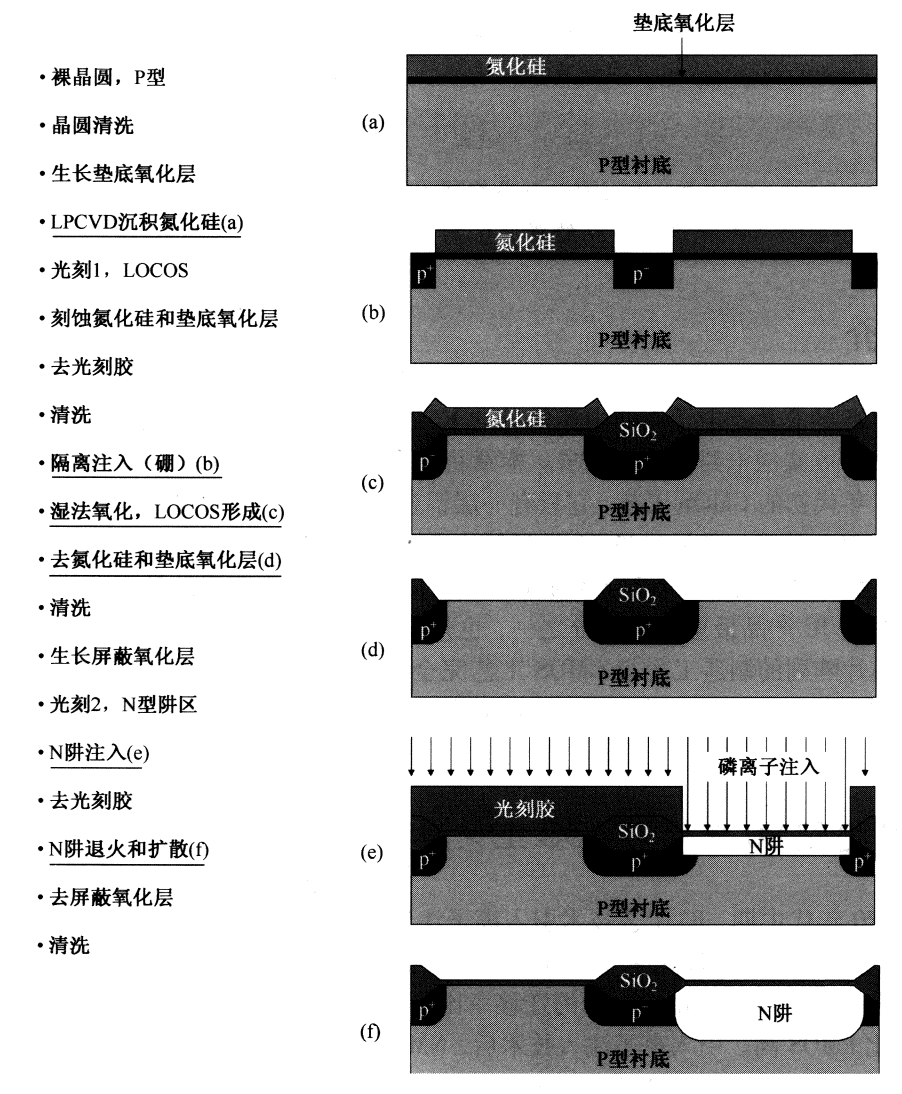

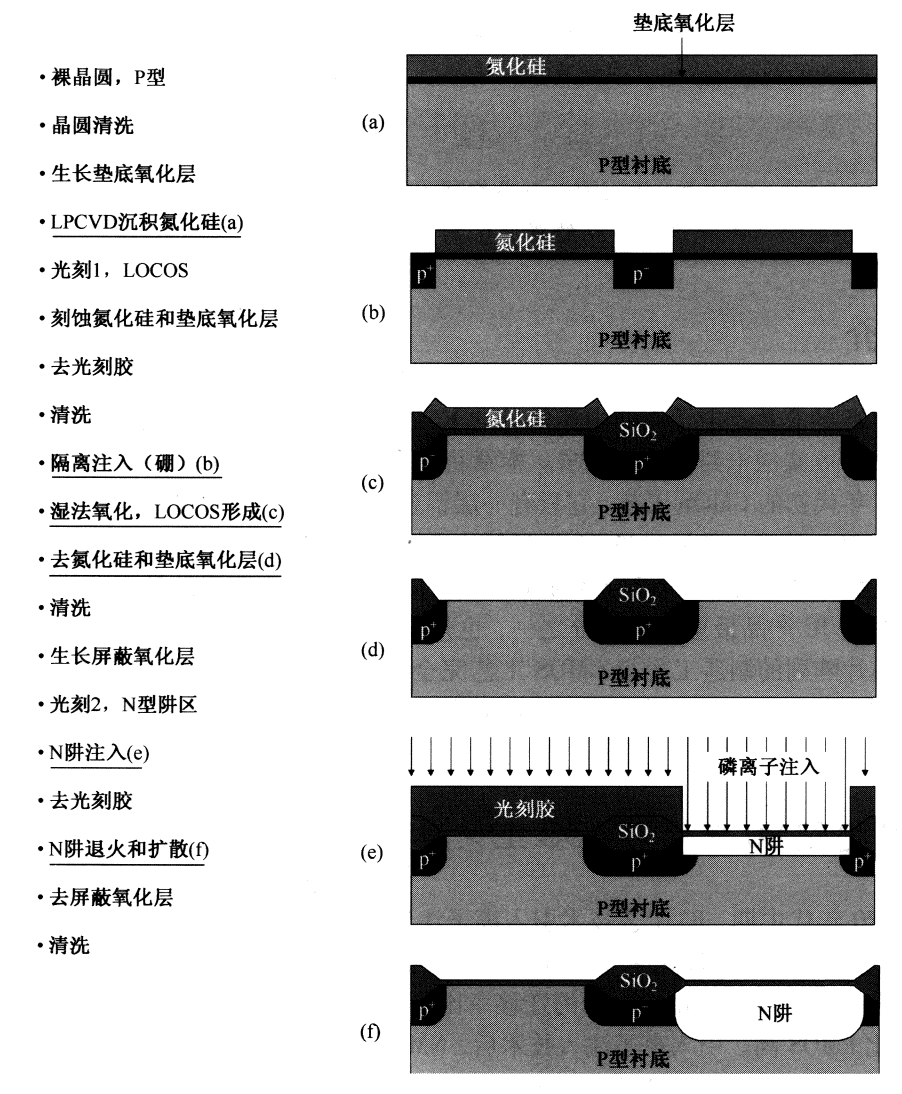

双镶嵌工艺通常用于铜金属化,需要两次介质刻蚀过程。至少有三种不同的方法形成双镶嵌铜金属化工艺需要的带孔槽。一种方法是首先刻蚀沟槽,然后刻蚀通孔(见下图)。另一种方法是埋硬掩膜,首先通过刻蚀通孔并停止于刻蚀停止层,然后用沟槽掩膜同时形成通孔和沟槽(见下图所示)。下图显示了先沟槽形成方法。先通孔和先沟槽这两种工艺都被用于IC制造中的铜金属化制程。

低左电介质刻蚀工艺中,刻蚀停止层通过等离子体中刻蚀副产品发射的光信号定义通孔和沟槽的深度。使用F/O可以刻蚀PE-TEOSUSG和SiCN。对于埋硬掩膜双镶嵌刻蚀(见下图所示),需要低k电介质对SiCN的高选择性。

钽(Ta)、氮化钽(TaN)以及二者的结合,可以用于铜阻挡层以防止铜通过介电层扩散到硅衬底中,这种扩散可能会毁坏晶体管。利用铜籽晶层进行化学电镀(ECP)大量的铜去填充狭窄的沟槽和通孔。铜籽晶层沉积后马上电镀大量的铜非常重要,因为即使在室温条件下,铜也可以迅速自退火。退火后的铜籽晶层有较大的晶粒尺寸和粗糙表面,从而在ECP过程中导致沟槽和通孔内产生空洞,并使成品率下降。

电镀铜后,在约250摄氏度的炉中退火以增加晶粒尺寸并降低电阻率。当Cu和Ta通过CMP工艺从晶圆表面去除后,仅仅在沟槽和通孔中留下金属形成互连线。通常利用晶圆表面的反射率判断金属CMP工艺的终点,因为大多数金属都有非常高的反射率,当金属被研磨完到达电介质表面后,反射率会大大降低,这表明刻蚀到了终点。

审核编辑:汤梓红

-

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测2025-04-15 1799

-

半导体制造工艺之光刻工艺详解2023-08-24 3398

-

#半导体制造工艺 概述电子技术那些事儿 2022-10-15

-

两种标准的半导体制造工艺介绍2022-03-14 8383

-

MEMS工艺——半导体制造技术2021-04-08 4480

-

半导体制造的难点汇总2020-09-02 4946

-

半导体制造教程之工艺晶体的生长资料概述2018-11-19 1550

-

半导体制程2018-11-08 5568

-

半导体制造技术经典教程(英文版)2014-03-06 26559

-

《半导体制造工艺》学习笔记2012-08-20 68064

-

半导体制造2012-07-11 5187

-

想了解半导体制造相关知识2012-02-12 6677

全部0条评论

快来发表一下你的评论吧 !