讲解一下SRAM型FPGA在轨会遇到的问题及其影响

存储技术

描述

SRAM型FPGA属于核心元器件,因此对SRAM型FPGA进行抗辐照加固设计非常必要。今天贫道主要给大家布道一下SRAM型FPGA在轨会遇到的问题及其影响。

1

**************SEE分类

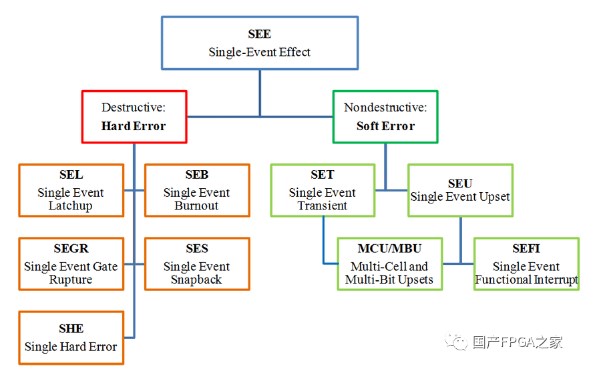

SRAM型FPGA空间应用下面临的主要问题是单粒子效应和总剂量效应。如图1所示,单粒子效应包括单粒子闩锁SEL,单粒子翻转SEU,单粒子瞬变SET和单粒子功能中断SEFI。SEL属于硬错误,可能会导致FPGA器件损伤。而SEU,SET和SEFI则属于软错误,一般不会对器件造成损伤,但会影响FPGA功能。

图1 元器件单粒子效应的分类

2

TID

经常听说某国产元器件TID指标大于100Krad or 150K rad,为啥要定义这个指标呢?不同轨道的航天器遭受的年剂量是不一样的,比如LEO轨道遭受的只有几Krad[si],GEO轨道年剂量可能达到100Krad[si],而MEO轨道年剂量最高可达数百Krad[si]。

这里提到的指标是典型的3mm铝屏蔽下的年剂量,乘以卫星的使用寿命,并考虑2~3倍的抗辐射设计余量(RDM),就是型号任务通常的抗总剂量要求。为了满足总剂量的要求,可以通过设备机箱进行屏蔽,也可以通过整星设计,设备机箱结合其他结构件组合屏蔽。一般到元器件层面总剂量指标大于100Krad能满足型号任务的需求。

3

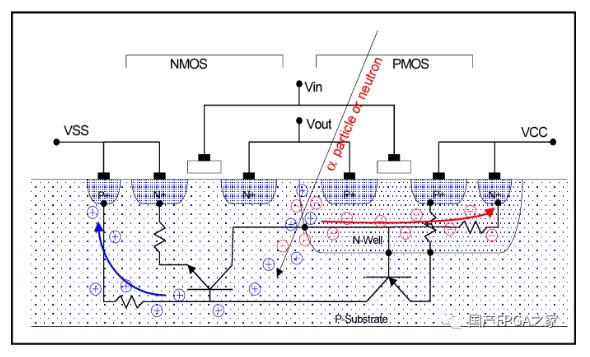

**************SEL

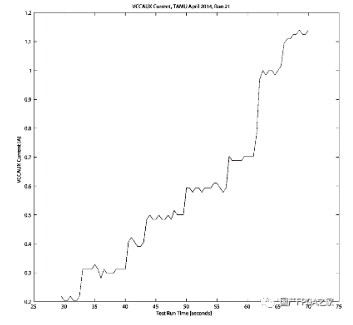

目前主流的SRAM型FPGA是CMOS工艺,由于天然的寄生效应,一个NMOS和一个PMOS串联起来产生PNPN结构。受单粒子效应的影响,PNPN会处于导通状态且不断电会一直处于导通状态,影响管子使用寿命。随着导通的管子数量增多,外在表现就是电流会阶梯型上升。某国产宇航级的FPGA会在芯片内部进行SEL特殊加固设计, 指标达到84 Mev.cm^2/mg板级设计不需要考虑额外的抗SEL设计。

工业级的FPGA则必须要在板级设计中考虑电源的监测和管理。由于电路的阶梯型上升特点,只对一级电源进行监测缺点是灵敏度不够,发现不了潜在的闩锁。最好对每路电源进行监测,提高灵敏度,一旦发生异常,采取断电重启。

图2 CMOS电路中的寄生效应

图3 发生SEL后电流阶梯型上升

4

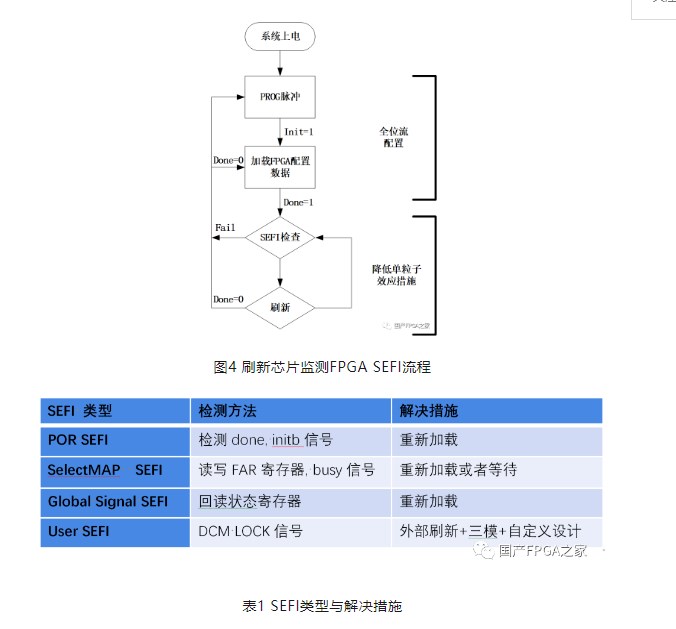

SEFI

SEFI分为应用级SEFI和器件级SEFI。如表1所示,器件级SEFI包括POR SEFI,SelectMAP SEFI,FAR SEFI和全局信号的SEFI。一般需要通过外部的刷新电路对器件级SEFI进行监测,并采取相应的应对措施。某国产宇航级的FPGA会在芯片内部进行SEFI特殊加固设计,指标达到37 Mev.cm^2/mg,极大增强了FPGA在轨稳定运行的能力。

应用级SEFI需要把由SEU导致的用户层面逻辑功能异常刨除掉,专注一些基础性的一般性的东西,否则应用级SEFI就是一个模糊不清的概念。本文中应用级SEFI指的是时钟SET、复位毛刺和MMCM/PLL/DCM的功能异常,下面对应用级SEFI分类进行说明。

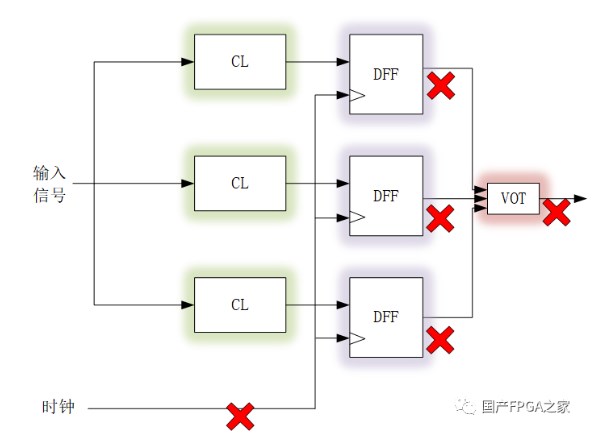

1)时钟SET

如图5所示,尽管对电路做了TMR加固,但时钟信号的SET会导致该时钟域下的所有寄存器发生SEU,最终Voter判定结果错误,TMR加固失效。

图5 时钟毛刺

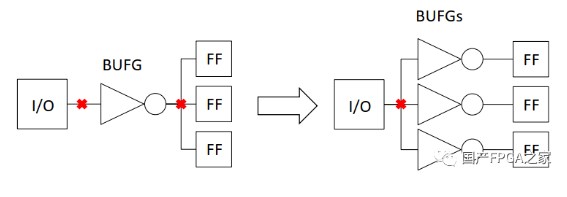

对时钟网络推荐采用GTMR策略,时钟IO不做TMR,对BUFG做TMR。加固前单点失效路径是整个时钟routing,加固后单点失效路径是IO到BUFGs的交汇处,通常单点失效路径截面大为减少。

图6 GTMR有效降低时钟网络SET概率

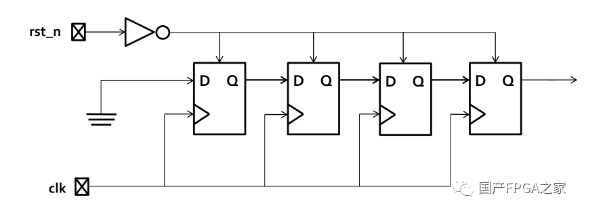

2)复位毛刺

FPGA加载时用GSR来控制寄存器和状态机初值,因此并不需要额外产生复位信号来做初值控制。比如,不需要复位的寄存器(如数据流相关的寄存器)不设计外部复位,用GSR做初值控制。对复位毛刺很敏感的寄存器和状态机,可以改用同步复位,同步复位比异步复位消耗资源多一些,但比异步复位对毛刺敏感性低。

图7 异步复位同步释放电路

如果外部异步复位扇出较多的寄存器,可以用GTMR加固策略。复位信号经过3个BUFG走全局时钟专用网络,单路复位毛刺翻转影响不了另外两路复位信号对应的寄存器。

3)MMCM/PLL/DCM

MMCM/PLL/DCM的LOCK信号为高并不代表功能一定正常,因此建议开发一种缓解方案,例如通过计数器来检测MMCM/PLL/DCM输出故障。一旦MMCM/PLL/DCM发生故障,进行复位操作。

5

**SEU**

单粒子翻转SEU可以发生在FPGA任意的资源上,比如配置SRAM、配置逻辑电路、用户逻辑DFF和块存储器等。

配置SRAM的SEU直接影响的是查找表LUT的值和互连资源的连接关系。查找表值的错误会导致用户逻辑功能出错,逻辑错误向下传播还可能导致时序单元出错。此外如果LUT用作了分布式RAM或者移位寄存器SRL,那么还会导致存储数据出错。

互连出错可能导致用户逻辑连接出错,连接错误向下传播可能导致时序单元出错。互连出错还可能导致互连产生短路,引起静态功耗增加。

触发器DFF的SEU会导致用户逻辑状态出错和FSM状态机出错。流水寄存器状态出错的影响仅限于单个时钟周期,因此影响比较小。FSM状态机出错可能会造成严重的影响。如图8 所示,状态机如果发生翻转至为定义的状态,那会导致状态机锁死,用户功能无法恢复。

图8 状态机发生SEU导致锁死

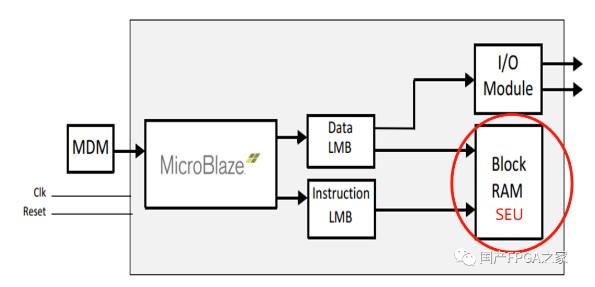

BRAM块存储器发生SEU可能会造成功能出错。当BRAM资源用作ROM,ROM存储重要的参数,重要参数发生错误会导致用户功能受到严重影响。比如FPGA内部跑软核,程序存储在FPGA内部的BRAM资源中,BRAM程序区的SEU会导致指针乱跳,程序跑飞。

图9 软核存储器发生SEU导致程序跑飞

战术总结

对于SRAM型的FPGA而言,单粒子效应SEE可产生严重的影响。

审核编辑:刘清

-

单粒子翻转引起SRAM型FPGA的故障机理阐述2020-01-26 8259

-

如何利用Verilog HDL在FPGA上实现SRAM的读写测试2025-10-22 4554

-

那位高人可以讲解一下电机的控制电路及其保护措施?谢谢2011-05-17 4594

-

Xilinx SRAM型FPGA抗辐射设计技术研究2012-08-17 3045

-

为什么没有大神做视频讲解一下VHDL呢2013-08-03 6162

-

有会FPGA数据采集的吗?一起交流一下!2015-07-16 3866

-

FPGA对两片SRAM的乒乓读写操作2017-10-14 9438

-

怎么提高SRAM工艺FPGA的设计安全性?2019-08-23 2169

-

详细的讲解一下I/O模式下的程序与MM模式下的程序调试2022-02-24 970

-

讲解一下MOSFET的构造2023-02-14 958

-

简单讲解一下时控开关手动如何打开或者关闭2020-11-19 20362

-

探讨一下关于贴片机在使用过程中会遇到的问题2020-11-25 2051

-

以STM32F407ZGT6单片机来讲解一下扩展外部SRAM2021-04-08 6025

-

SRAM型FPGA在轨会遇到的问题及其影响2023-08-11 3802

-

SRAM型FPGA的抗辐照加固设计2023-08-15 6466

全部0条评论

快来发表一下你的评论吧 !