并行Nand Flash的结构和基本工作过程

存储技术

描述

Storage-5---并行Nand Flash

引言:并行Nand Flash是中等容量存储方案的理想选择,相比于SPI Nand Flash,性能更优,但体积较大,使用并没有后者广泛,多使用在嵌入式,物联网,工业等领域。

1.结构

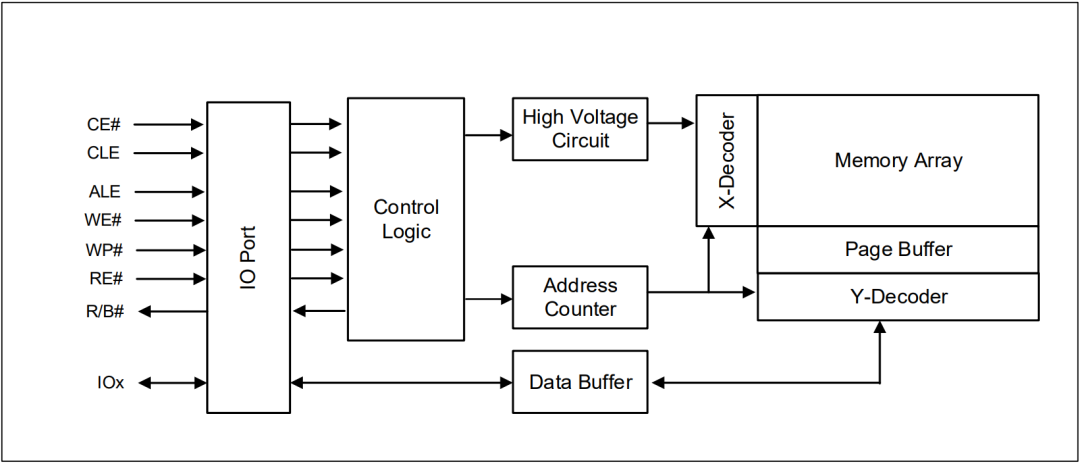

并行Nand Flash的结构如图5-1所示,虽然eMMC也是并行Nand Flash的一种,但二者不能混为一谈,接口和遵循的标准都不相同。

图5-1:并行Nand Flash基本结构

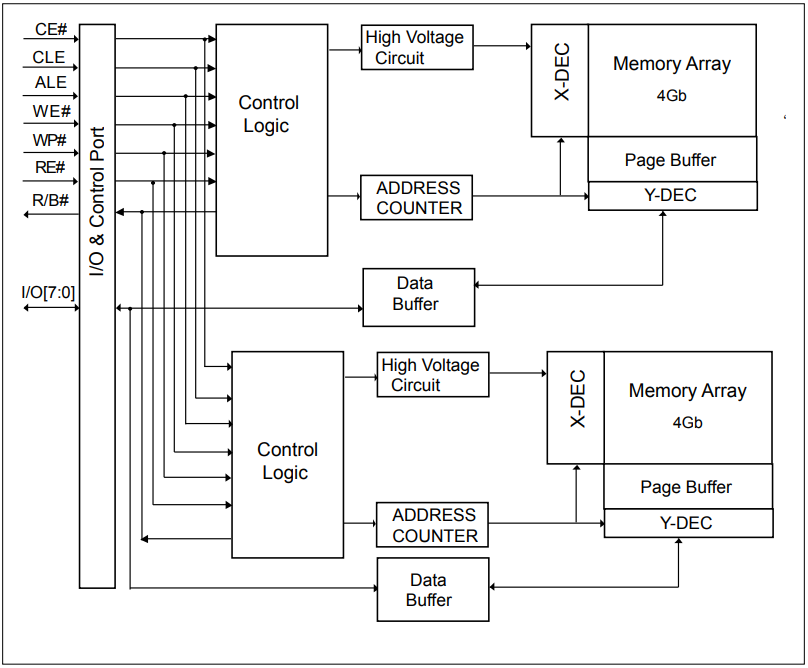

并行Nand Flash由存储阵列、页缓冲器、编码器,地址计量、数据缓冲器、逻辑控制器、接口几大部分构成,同时容量的扩展也支持多片叠封如图5-2。增强的体系结构和接口,支持高速缓存程序功能,允许在将数据寄存器复制到闪存阵列时将数据插入高速缓存寄存器。当长文件被写入存储器时,这种流水线程序操作提高了程序吞吐量,还实现了缓存读取功能。当连续页面必须流式传输时,此功能可以显著提高读取吞吐量。

图5-2:双片叠封的并行Nand Flash

2.接口

并行Nand Flash的I/O引脚(IO[0:7]或者IO[0:15])用于输入命令、地址和数据,并在读取操作期间输出数据,所以并行Nand Flash不是全双工传输,某一时刻只能是输入或者输出。当芯片被取消选择或输出被禁用时,I/O引脚浮动到高Z。并行Nand Flash数据线宽度可选x8或者x16,信号线模式有非同步Asynchronous和Synchronous同步两种,数据采集模式:SDR/DDR,引脚及其定义功能如下:

CE#:片选,如果没有检测到CE信号有效,那么Nand Flash设备将保持待机模式,不对任何控制信号做出响应。

WE#:写使能,WE#负责将数据、地址或命令写入Nand Flash设备中。

RE#:读使能,RE#允许数据输出数据缓冲器。

CLE:命令锁存使能,当CLE为高时,在WE#信号的上升沿,命令被锁存到Nand Flash命令寄存器中。

ALE:地址锁存使能,当ALE为高时,在WE#信号的上升沿,地址被锁存到Nand Flash地址寄存器中。

I/O[7:0]:数据总线(针对x16部件的输入/输出[15:0])

WP#:写保护

R/B#:就绪/忙

如果并行Nand Flash器件忙于擦除、编程或读取操作,R/B#信号将变低(R/B#信号为漏极开路,需要采用上拉电阻)。

3.传输速度和容量

并行Nand Flash非标/ONFI标容量可以做到8Gb,顺序读取速度可以做到25ns。它还结合了从一个页面到另一个页面的回拷贝程序功能,而无需将数据传输到外部缓冲存储器或从外部缓冲存储器传输数据,从而允许优化缺陷块管理,例如当页面编程操作失败时,数据可以直接编程到同一阵列部分内的另一个页面中,而无需耗时的串行数据插入阶段。

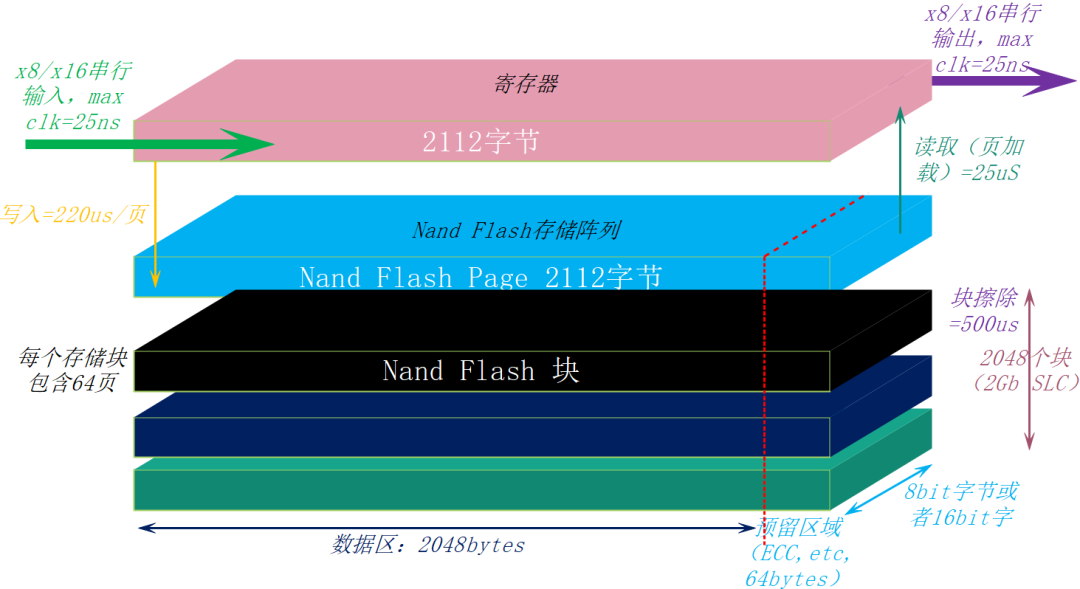

图5-3:SLC Nand物理结构

图5-3是并行Nand Flash的物理结构,存储阵列由2048(2Gb)个可单独擦除的2112×64字节块组成。其中预留区域64x8列位于列地址2048~2111之间,2112字节的数据寄存器连接到存储器单元阵列,用于在页读取和页编程操作期间在I/O缓冲器和存储器之间进行数据传输,编程和读取操作以页为基础执行,而擦除操作以块为基础执行。

4.基本工作过程

并行Nand Flash的地址使用8个I/O多路复用传输,这样可以保持主板设计的一致性,大大减少了引脚数量,还可以支持系统升级到更高的容量。

并行Nand Flash通电时自动读取,当WE#变低,命令、地址和数据都通过I/O写入,而CE#变低,这些都会被锁定在WE#的上升边缘。命令锁存器使能(CLE)和地址锁存器启用(ALE)分别用于通过I/O引脚多路传输命令和地址。有些命令需要一个总线周期,例如重置命令、状态读取命令等只需要一个循环总线。其他一些命令,如页面读取、块擦除和页面编程,则需要两个周期:一个周期用于设置,另一个周期执行。

-

NAND Flash的基本原理和结构2025-09-08 7723

-

单片机应用系统的结构与工作过程2017-07-05 2452

-

Nand flash驱动工作原理2018-07-17 2188

-

NAND Flash的储存结构与接口设计2020-11-05 3870

-

传感器的原理结构及工作过程2009-11-23 3125

-

IPOA的工作过程是怎样的?2010-04-07 762

-

NAND_Flash结构与驱动分析2016-03-17 941

-

演示Nand Flash读写操作过程2018-06-15 7953

-

浅谈EEPROM和flash的区别 及 nor flash和nand flash2018-10-07 25575

-

什么是pSLC Nand Flash2020-07-22 6372

-

NAND Flash 的存储结构以及NAND Flash的接口控制设计2020-11-03 5641

-

SPI Nand Flash简介2021-12-02 5299

-

Nand Flash工作原理2022-02-10 1779

-

NAND Flash 原理深度解析(下)2023-09-22 5510

-

从NOR Flash 到 NAND Flash 和SD NAND,从底层结构到应用差异2026-03-05 381

全部0条评论

快来发表一下你的评论吧 !