SerDes的基础知识

电子说

描述

SerDes的简介

SerDes 是SERializer串行 器/DESerializer解串器的简称,这种主流的高速的时分多路复用(TDM)点对点的串行通信技术可以充分利用通信的信道容量,提升通信速度,进而大量的降低通信成本。目前,商用基于SerDes架构的通信协议最高可实现单通道112Gbps的速率。

SerDes的主要作用就是把并行数据转化成为串行数据,或者将串行数据转化为并行数据的,能提供比并行传输更高带宽。

实际上PCIE,JESD204B等复杂协议都是基于SerDes协议,常见的电SerDes就PCIE等协议来说,更接近物理层,所以SerDes通常又被称之为物理层(PHY)器件。

正是因为SerDes的强电气属性,使得 Serdes具有以下优点:

①减少布线冲突(非独立时钟嵌入在数据流中,解决了限制数据传输速率的Signal时钟的Jilter问 题);带宽高 ;

②引脚数目少 ;

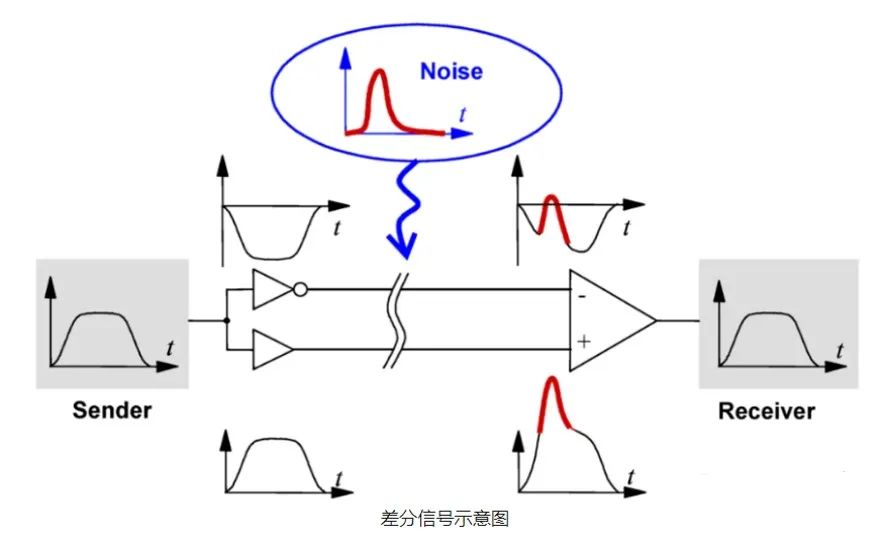

③抗噪声、抗干扰能力强(差分传输);

④降低开关噪声;

⑤扩展能力强;

⑥更低的功耗和封装成本;

SerDes的分类

SerDes支持非常多的的主流工业标准,比如Serial RapidIO ,FiberChannel(FC),PCI-Express (PCIE),Advanced Switching Interface,Serial ATA(SATA),1-Gb Ethernet,10-Gb Ethernet(XAUI),Infiniband 1X,4X,12X等。根据SerDes的结构的不同可以将其分为四类:

①并行时钟SerDes:将并行宽总线串行化为多个差分信号对,传送与数据并联的时钟。这些SerDes 比较便宜,在需要同时使用多个SerDes 的应用中,可以通过电缆或背板有效地扩展宽总线;

②8B/10B编码SerDes(最常见的结构):将每个数据字节映射到10bit代码,然后将其串行化为单一 信号对。10位代码是这样定义的:为接收器钟恢复提供足够的转换,并且保证直流平衡(即发送相 等数量的‘1’和‘0’)。这些属性使8B/10B编码SerDes 能够在有损耗的互连和光纤传输中以较少的信号失真高速运行;

③嵌入式时钟SerDes:将数据总线和时钟串化为一个串行信号对。两个时钟位,一高一低,在每个 时钟循环中内嵌串行数据流,对每个串行化字的开始和结束成帧,并且在串行流中建立定期的上升边沿。由于有效负载夹在嵌入式时钟位之间,因此数据有效负载字宽度并不限定于字节的倍数;

④位交错SerDes:将多个输入串行流中的位汇聚为更快的串行信号对。

SerDes的结构

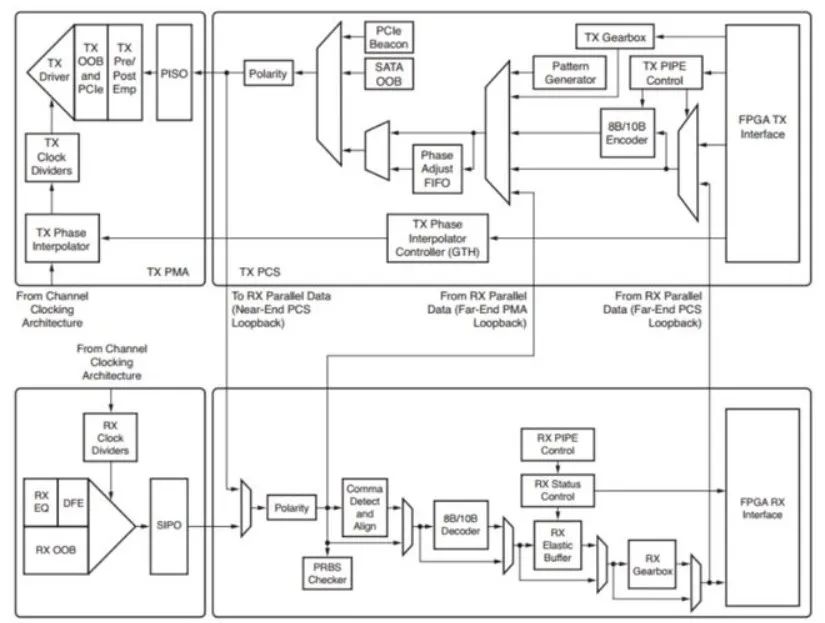

SerDes收发器内部包括高速串并转换电路、时钟数据恢复电路、数据编解码电路、时钟纠正和通道绑定电路,为各种高速串行数据传输协议提供了物理层(PHY)基础。而主流的8B/10B编 码SerDes则主要由物理介质相关子层( PMD)、物理媒介适配层(Physical Media Attachment,PMA)和物理编码子层( Physical Coding Sublayer,PCS )所组成,且收发器的 TX发送端和RX接收端功能独立。

SerDes收发器内部的电路物理层结构图

各物理层的作用:

①PCS层,负责数据流的编码/解码,是标准的可综合CMOS数字逻辑,可以通过逻辑综合实现 软硬综合实现。

②PMA层,是数模混合CML/CMOS电路,负责负责串化/解串化,是理解SerDes区别于并行接 口的关键。

③PMD层,负责串行信号通信。

涉及到的相关模块:

①TXPLL:这个模块主要使用具有1ps以下的抖动的时钟为参考,输出数GHZ级的时钟。

②RXCDR(时钟恢复):这个模块是一个复杂的控制回路,作用是来追踪传入数据的平均相位, 并不管Path上的任何SI或失真,通常是通过复杂的相位旋转器或CDR驱动的锁相环来完成的。

③TXdriver:这个模块把序列化模块转化为差分信号。

④RX均衡器:此模块用连续的时间均衡器以及DFE(裁决反馈均衡器)来均衡高速效应,通常 需要一个自动增益的电路来促进均衡效果,RX均衡器通常以状态机逻辑和软件的形式来实现

自动校准。

转化过程:

①发送(TX)即并转串,简单的来说就是并行信号通过FiFO,传递给内部的8b/10b编码器、扰码器,防止数据连0/1,之后传递给串行器进行转化,经过均衡器均衡后,由驱动发出。

②接收(RX)即串转并,简单的来说就是输入的串行信号经过线性均衡器均衡后,去除了高速时钟的jilter后,CDR从数据中恢复Caputure时钟,并通过解串器转为对齐的并行信号,由驱动发出。

SerDes底层硬件

SerDes底层硬件包括早期的LVDS和现在CML:SerDes信号层采用的LVDS工作在155Mbps~1.25Gbps之间,而CML(电流模式信号)在600Mbps和10+ Gbps。因此现在SerDes一般使用CML。但是LVDS和CML信号可以互通,但要有外接电阻做电平转换。

高速逻辑电平的特性

LVDS、CML、LVPECL之间是有区别,但都使用差分传输Differential Transmission 信号传输的一种技术,区别于传统的一根信号线一根地线的非平衡型单端Single End Transmission 做法,差分传输在这两根线上都传输信号,这两个信号的振幅相同,相位相反。在这两根线上的传输的信号就是差分信号。信号接收端比较这两个电压的差值来判断发送端发送的逻辑状态。在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

审核编辑:刘清

-

QC基础知识2010-06-02 1539

-

SERDES的作用 SerDes基础知识详解2024-01-04 9313

-

labview基础知识2018-03-08 6600

-

通信基础知识教程2010-03-04 972

-

软板基础知识2006-06-30 1590

-

电子电路基础知识2008-01-15 249716

-

电池基础知识(集全版)2009-11-10 3010

-

电池隔膜基础知识2009-11-17 1593

-

计算机基础知识介绍2015-12-03 1037

-

使用Eclipse基础知识2016-02-26 1004

-

synplify基础知识说明2016-06-17 2318

-

电源管理基础知识电源管理基础知识电源管理基础知识2017-09-15 1754

-

优质LDO基础知识分享2023-03-26 2538

-

高速接口SerDes基础知识总结2023-12-13 5895

-

射频与微波基础知识2024-01-16 1885

全部0条评论

快来发表一下你的评论吧 !