案例分析:电磁干扰对辐射TIS的影响

描述

对于一个射频工程来说,在无线网络中,射频模块有传导TRP和传导TIS两项重要指标,而模块装上天线后,整机在OTA暗室中需测试TRP与TIS,在此我们将其定义为辐射TRP和辐射TIS。辐射TRP一般不会出问题,而辐射TIS容易受产品内部电磁噪声的干扰。所以说解决电磁干扰对于天线接收灵敏度的提升有着非常大的影响。

当辐射TIS不达标时,首先要考虑传导TIS是否达标,传导TIS和射频电路中的器件(如双工器的隔离度)、各节电路的匹配等因素有关。射频电路部分工作流程如下:

接收:

天线 →匹配电路 →双工器 →声表滤波器(SAW) →低噪声放大器(LNA) →混频器

发射:

天线← 匹配电路← 双工器← 功率放大器(PA)← 混频器

当传导TIS达标后,我们再处理产品内部的电磁干扰。电磁干扰是无处不在的,产品内部工作频率及其谐波频率高达1G以上,当干扰频率落在天线接收频率范围时,就会影响TIS。下面通过一些案例说明电磁干扰对辐射TIS的影响。

案例一:智能POS机中DDR时钟、屏的时钟和数据、地噪声影响4G天线TIS。

呈现问题:

智能POS机中,4G天线FDD ban5/8 在OTA暗室中测试TIS值为-78dB,辐射TIS不合格(合格值为-91dBm),而辐射TRP与模块传导TRP与TIS都达标。分析问题:传导TRP与TIS都达标,说明模块本身无问题;辐射 TRP达标,说明天线也没问题,而辐射TIS仅为-78dBm, 可以判定是产品内部电磁干扰影响了接收灵敏度。运用频谱仪侦测干扰源,发现CPU与DDR的时钟频率和屏的差分时钟、数据干扰很大(如下图)。

解决问题:

1. 通过软件适当降低DDR时钟的驱动能力,TIS值从-78dBm提升到了-80dBm, 用锡将CPU与DDR上方的屏蔽盖周围与PCB地良好焊接,TIS值从-80dBm提升到了-83dBm(用锡将屏蔽盖焊死不符合量产,后面改板将屏盖夹子去掉,将夹子改为金属框,金属框与PCB地良好焊接,然后屏蔽盖卡进金属框,测试TIS能达- 82dBm。)

小结:屏蔽盖的作用一是屏蔽空间辐射,作用二是承当地回路,减弱共模噪声。

2. 焊好屏蔽盖后,用导电布将屏排线屏蔽并两端接地,测试TIS值能达-86dBm 。(改板后在屏的差分时钟和数据对各串一颗90Ω的共模电感,同时将原来的屏FFC排线改为FPC排线,测试TIS能达-88dbm。

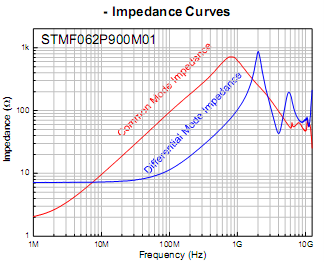

小结:下图是90Ω共模电感的频率特性曲线图,90Ω指的是频率在100MHz时的共模阻抗,共模阻抗随着频率的变化而变化,在800MHz-960MHz时的共模阻抗高达600Ω,所以共模电感对800MHz-960MHz的共模噪声有很好的抑制效果;FPC排线具备屏蔽效果,同时能给信号提供地回路。

3. 将屏后铁板与PCB地相接的导电棉去掉,只保留天线接地位的导电棉,测试TIS能达-91dBm,最终辐射 TIS 达标。

小结:地噪声传播的形式是电流,电流往阻抗低的方向流动,PCB上的地噪声会通过导电棉流向后盖金属,然后通过后盖流向天线的接地位。

案例二:智能音箱中频偏影响WIFI天线的TIS。

呈现问题:

智能音箱中2.4G WIFI天线 测试传导、辐射的TRP和TIS都不达标,天线的驻波比、回波损耗等参数正常。

分析问题:

传导TRP和TIS都不合格,说明模块本身存在问题;通过调节各电路的匹配,TRP和TIS没有明显提升,通过频谱仪查看发射频率,发现其频率偏移,频偏问题首先考虑晶振,因为晶振基准频率误差大,就会造成本地振荡信号频偏,本地振荡信号是合成发射和接收频率的一部分。

解决问题:

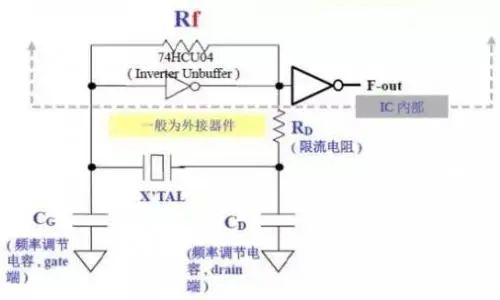

如下图,通过调节晶振两边的匹配电容CG和CD,最后取值10pF, 使发射和接收频率都在标准范围内,最终测试TRP和TIS合格。

小结:负载电容是晶振产生基准频率的一个参数,负载电容包含了CG、CD和走线寄生电容以及芯片端等效电容 ,走线寄生电容和芯片端等效电容不好把控,所以需要外围 CG、CD去调节。

案例三:行程记录仪中 DC-DC 和摄像头的噪声影响GPS天线的接收灵敏度

呈现问题:

行程记录仪中GPS天线测试辐射TIS不达标,而TRP与传导TIS都满足要求。天线的驻波比、回波损耗等参数正常,这样基本可以判定是产品内部电磁干扰影响了接收灵敏度。

分析问题:

运用频谱仪侦测干扰源,发现背光的DC-DC输出的纹波噪声和摄像头时钟的谐波干扰很大,实验的过程中,调节频的亮度和关闭摄像头,搜星数和星值都有提升,确定了背光和摄像头的噪声干扰了GPS天线的TIS。

解决问题:

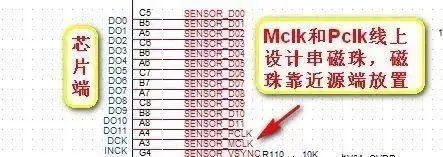

1.如下图,分别在MCLK和PCLK线上串120Ω磁珠,MCLK的磁珠靠近芯片端,PCLK线上的磁珠串在摄像头端,搜星数和星值有一定的提升。小结:磁珠放置的位置是靠近源端,这样就减弱了中间部分走线的辐射和耦合干扰。MCLK由芯片给出,而PCLK由摄像头发出。

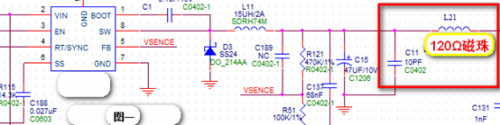

2. 如下图,DC-DC输出端增加一颗10pF的电容,然后在电容后串120Ω的磁珠滤除纹波,最后GPS搜星数和星值达标。

小结:通过计算,10pF左右的电容滤除1.575GHz的频率效过最佳,而磁珠的大小和放置的位置会影响DC-DC的转换效率,磁珠一般放置在电容之后。

总结:产品内部常见的电磁干扰有DDR、屏、摄像头等时钟的谐波噪声和DC-DC纹波噪声、地噪声等。PCB设计初期需考虑EMC设计,布好局、布好线,高频信号线设计串共模电感或磁珠的位置,电压线设计串磁珠和并电容位置等等,避免再次改板,缩短研发周期。

审核编辑:汤梓红

-

如何处理变频电路中电磁辐射引起的干扰2010-01-04 2352

-

电磁波是什么?电磁辐射是什么?2010-03-13 3294

-

电磁辐射(EMR)2017-03-14 6190

-

传导干扰和辐射干扰2019-05-30 12439

-

怎么做才能降低电磁辐射的干扰?2019-08-07 5056

-

如何用频谱分析仪测量电磁干扰和判断干扰发生源?2019-11-14 4385

-

如何查找电磁辐射骚扰原因以及电磁辐射干扰的整改步骤?2020-10-22 2232

-

如何去降低电磁感应的传导干扰和辐射干扰?2021-05-20 2685

-

电磁干扰与电磁兼容之二:传导干扰和辐射干扰2009-05-05 2276

-

电磁干扰是什么?2017-01-12 4215

-

电磁干扰对辐射TIS的影响2018-07-11 13775

-

电磁干扰与电磁兼容的传导干扰与辐射干扰的详细资料说明2020-08-06 1424

-

电磁干扰影响天线接收灵敏度案例分析2023-08-03 4611

-

电磁干扰与电磁辐射的区别 EMI电磁干扰与电力系统的关系2024-11-20 2278

-

现场解决EMC电磁辐射干扰:降辐射,查路径,锁源头2025-09-16 1081

全部0条评论

快来发表一下你的评论吧 !