如何利用55 nm BCD技术实现高性能SPAD呢?

描述

单光子雪崩二极管(SPAD)是各类应用需求量很大的器件,特别是在生物医学实践方面。以CMOS技术制备的SPAD凭借其低制造成本、可大规模量产以及与电路的单片集成能力等优势而备受关注。此外,随着“摩尔定律”等比例缩微,CMOS-SPAD的优势在像素分辨率、尺寸及功能等方面愈加突出。因此,诸多研究都在尝试开发基于先进CMOS技术的SPAD探测器。

据麦姆斯咨询报道,近日,韩国科学技术研究院(KIST)、瑞士洛桑联邦理工学院(EPFL)、延世大学(Yonsei University)和格罗方德半导体(GlobalFoundries)新加坡工厂的联合科研团队在IEEE Journal of Selected Topics in Quantum Electronics期刊上发表了以“SPAD Developed in 55 nm Bipolar-CMOS-DMOS Technology Achieving Near 90% Peak PDP”为主题的论文。该论文的第一作者为KIST和EPFL的Won-Yong Ha,通讯作者为EPFL的Edoardo Charbon、延世大学的Woo-Young Choi和KIST的Myung-Jae Lee。

这项研究报道了一种利用55 nm双极型CMOS-DMOS(BCD)技术实现的SPAD。为了在保持击穿电压(VB)小于20 V的情况下实现高性能,由p型轻掺杂漏极(PLDD)与高电压N阱(HVNW)层形成结。此外,SPAD上方的介电层被适当蚀刻,以减少多层反射。该SPAD在光子探测概率(PDP)、暗计数率(DCR)和时间抖动(Timing Jitter)等方面的性能出色,击穿电压低至16.1 V。

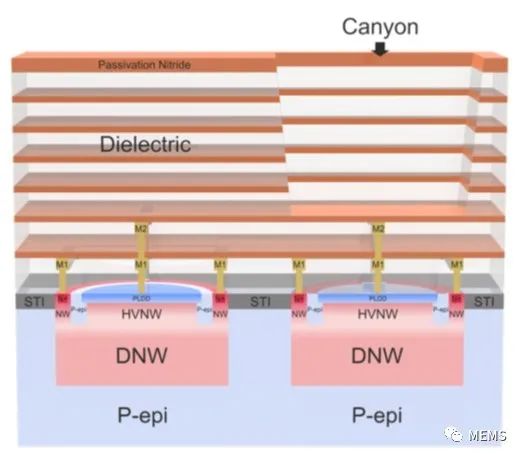

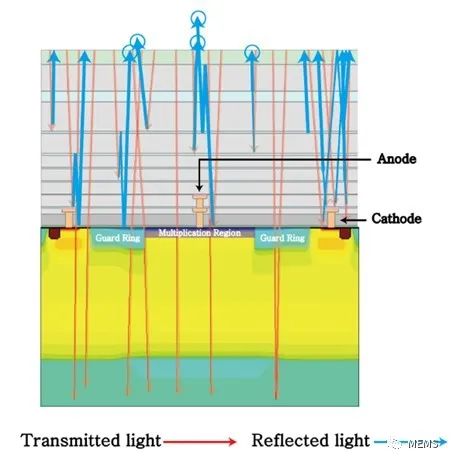

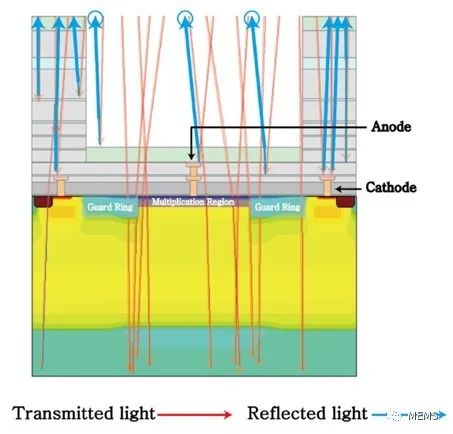

图1为两种SPAD结构的截面图,两种SPAD具有相同的器件结构,PLDD与HVNW层形成了直径9 μm的PN结,总直径达到14.4 μm,如图2所示。两层结构均是该技术的标准形式,其优势主要包括:(i)PLDD产生较少的注入引起的缺陷(implantation-induced defect),从而实现低噪声SPAD运行;(ii)HVNW利用PLDD层提供了适当的耗尽区,该区域足够宽,可以防止带间隧穿,但同时不过分宽,避免击穿电压显著增加。

图1 BCD-SPAD的横截面

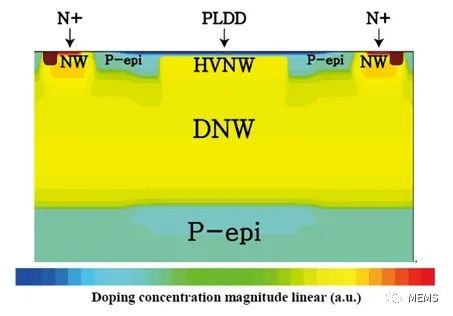

图2 BCD-SPAD的掺杂浓度分布图谱

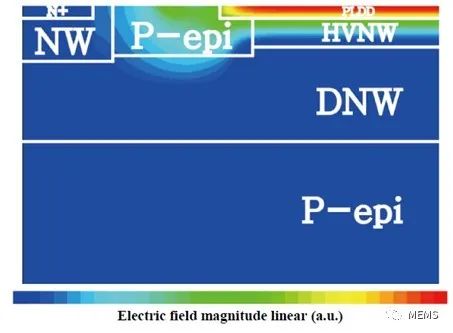

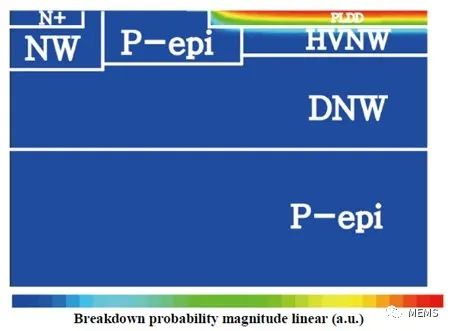

在击穿电压(VB)16 V、额外偏置电压(VE)7 V时,研究人员利用Okuto的雪崩击穿模型对SPAD进行了TCAD仿真,验证了SPAD的E场分布,仿真结果如图3至图6所示。

图3 利用TCAD仿真得到BCD-SPAD的电场分布图谱

图4 利用TCAD仿真得到BCD-SPAD的击穿概率分布图谱

图5 利用TCAD仿真得到无“峡谷”(canyon)BCD-SPAD的简化光线追踪结果

图6 利用TCAD仿真得到“峡谷”(canyon)BCD-SPAD的简化光线追踪结果

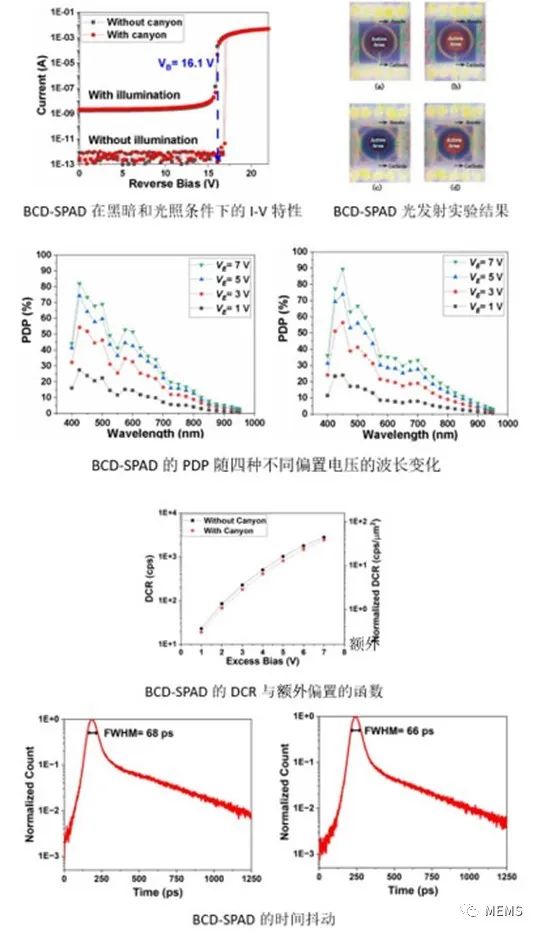

随后,研究人员对BCD-SPAD的I-V特性、光发射、PDP、DCR以及时间抖动进行了测试,结果如图7所示。

图7 BCD-SPAD相关性能测试

综上所述,这项研究开发并表征了一种利用55 nm BCD技术实现的高性能SPAD。利用BCD技术中的可用层,在低击穿电压(VB)下将SPAD结构优化为低噪声且高效率运行。为了提高其探测效率,研究人员使用“峡谷”(canyon)蚀刻来减少多层反射。当击穿电压(VB)为16.1 V,该SPAD在450 nm处峰值PDP为89.4%、DCR为38.2 cps/μm²;当额外偏置电压(VE)为7 V时,时间抖动为66 ps。研究结果表明,所提出的SPAD在多种生物医学应用领域具有巨大潜力。

这项研究获得了韩国科学技术研究院(KIST)合作项目(2E32242)的资助和支持。

审核编辑:刘清

-

CD4527B:高性能CMOS BCD速率乘法器的技术剖析与应用探索2026-04-18 83

-

创飞芯55nm BCD工艺OTP IP实现上架2025-05-30 1493

-

安森美推出基于BCD工艺技术的Treo平台2024-11-12 1659

-

如何实现PMSM高性能控制2021-08-27 1267

-

如何利用SMIC55nm工艺设计VCO版图?2021-06-24 2087

-

怎么才能实现高性能的PCB设计?2021-04-26 2070

-

如何利用专用晶圆加工工艺实现高性能模拟IC?2021-04-07 2717

-

看完秒懂,高性能数字电源技术与实现技巧2020-07-02 12901

-

如何利用28nm高端FPGA实现功耗和性能的平衡?2019-09-17 2915

-

如何设计利用差动放大器实现低损失、高性能全波整流器的电路?2019-08-02 1817

-

利用差动放大器实现低功耗、高性能绝对值电路2019-01-05 2408

-

如何利用二进制数实现BCD码的转换2018-05-19 29324

-

Altera率先交付高性能28nm FPGA量产芯片2012-05-14 2865

-

赛灵思高性能40nm Virtex-6 FPGA系列通过全生产验证2010-04-24 2392

全部0条评论

快来发表一下你的评论吧 !