数字设计中常见的CDC问题

电子说

描述

①CDC中的亚稳态传播问题

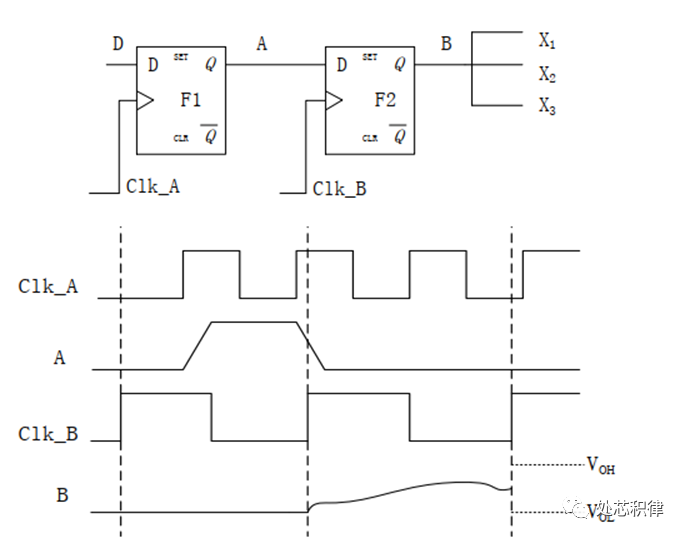

在数字系统级别的时钟域交叉(CDC)中,亚稳态传播问题是一个重要的挑战。在这个问题中,由于时序差异,信号在触发器之间的传输可能会导致亚稳态值的产生和传播。让我们来看一下模型,如图1所示。

图1 CDC 时候的亚稳态

当时钟信号Clk_B的第二个上升沿到来时,输入数据信号A正好处于变化过程中。这导致A信号未能满足触发器F2的建立-保持时间要求,从而在输出节点B处产生了亚稳态值。在B节点产生的这个亚稳态中间值,会影响后续的三个分支X1、X2、X3,但对于其所代表的逻辑状态可能存在不同的解读。

其中一个分支可能将这个亚稳态值解读为逻辑值1,而另一个分支可能将其解读为逻辑值0。这种后续电路对于前级亚稳态的自由解读可能会在系统电路运行过程中随机出现。这种现象对完整的系统时序可能会产生巨大的影响,因此在设计数字系统时需要特别注意这种亚稳态传播问题的影响。

②CDC 中异步输入数据的保持时间问题

在时钟域交叉(CDC)中,当一个数据信号从快时钟域进入慢时钟域时,可能会产生与快时钟周期等宽的脉冲信号,因为该数据信号的翻转变化严格依赖于快时钟域的信号采样。然而,对于慢时钟域的时钟采样边沿来说,很容易忽略这种短暂脉冲状的异步输入数据。

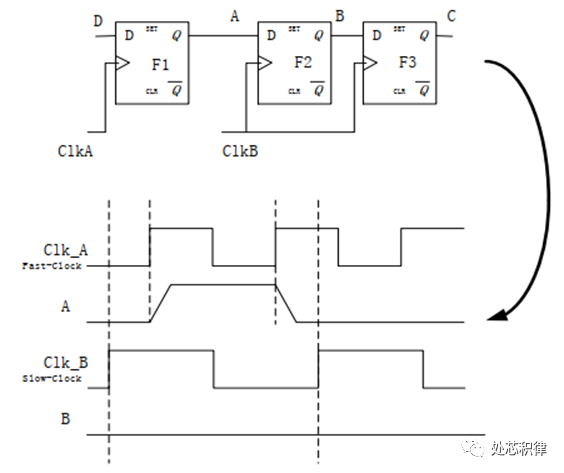

图2 数据保持时间问题电路模型与时序波形

这种情况可能导致在CDC传输过程中丢失数据,主要原因是异步输入数据的保持时间不符合目标触发器的要求。如图2所示,异步输入数据A随着源时钟域信号clk_A的一个周期变化。由于数据A的保持时间较短,小于目标时钟域的一个时钟周期,并且两个时钟域的时钟信号之间没有固定的相位关系,结果是在clk_B的两个上升采样边沿之间,类似脉冲信号的数据A被目标时钟域的同步触发器所忽略,从而导致数据丢失的现象。

为确保异步数据在不同时钟域之间的可靠传输,需要仔细考虑数据保持时间的问题,并采取适当的电路设计和时序调整措施,以避免这种数据丢失情况的发生。

③CDC 中的数据关联和竞争

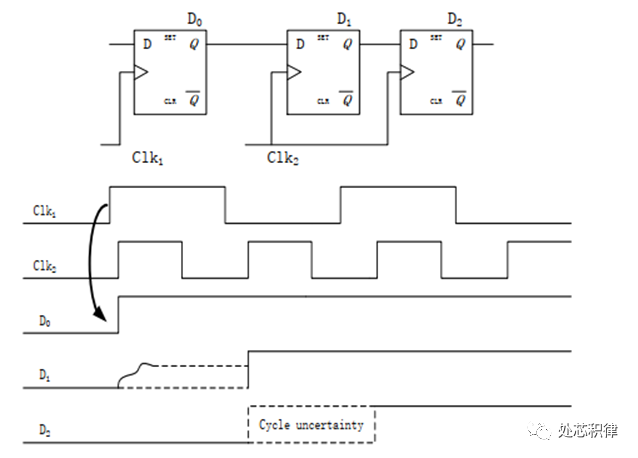

在图3中展示了一个常见的两级触发器型同步设计,其主要功能是实现同步和孤立亚稳态。然而,由于触发器亚稳态的恢复时间很难准确预测,这种同步设计具有一个重要的特性,即"周期不确定性" 。

图3 多触发器同步电路模型与时序波形

从图3的时序波形可以看出,尽管触发器D1将亚稳态孤立并禁止,但对于目标触发器D2而言,在Clk2的第二个上升沿时刻,无法确定其是否会成功翻转到稳定状态。它有可能在第二个Clk2上升沿时刻翻转为逻辑值1,也有可能不翻转,继续保持逻辑值0。直到Clk2的第三个上升沿时刻到来,目标触发器D2才能稳定输出期望的逻辑值1。这种情况被称为同步电路的"周期不确定性"。如果这个异步输入数据是单比特类型,这种CDC问题可能不会对后续电路的正常功能产生影响。然而,如果涉及多比特数据,采用这种同步方式就可能导致数据通道传输的混乱。

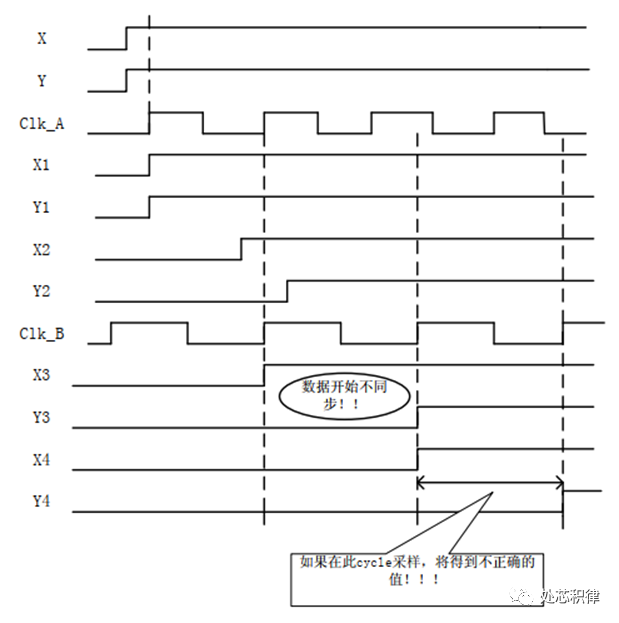

图4 多 bit 信号的汇聚问题

基于以上分析,当多比特类型的数据信号采用分别同步的方式进行处理时,一旦这个信号在跳变后发生,由于每条传输路径上的延迟不同以及同步设计的周期不确定性,很可能导致最终输出数据的不一致。这种情况可能引发目标模块逻辑中一组无法预测的数据值,从而破坏整体功能的稳定性。

通过综合考虑这些因素,在设计时必须慎重选择适当的同步策略,以确保数据的可靠传输和处理,避免因为同步问题而引发的数据竞争和不一致性。

那么问题来了,我们应该如何对存在CDC的信号进行同步处理呢?

对于时序要求较为严格的数字SOC电路,在处理时钟域交叉(CDC)同步时,简单地使用串联触发器的形式已经无法满足设计要求。必须采取更为复杂的同步设计机制。在实际工程项目中,有几种常见的方法:

异步的 FIFO

握手协议

单一使能信号

结语:

在数字系统级别的时钟域交叉(CDC)中,各种复杂的问题可能会影响设计的稳定性和性能。亚稳态传播、异步输入数据的保持时间和数据关联竞争等都是必须认真对待的挑战。为了确保设计的正确性和可靠性,我们需要采取一系列严谨的同步设计策略。

针对时序要求严格的数字SOC电路,简单的串联触发器同步已不再足够。我们需要借助更为复杂的同步设计机制来处理CDC问题。在实际项目中,常见的方法包括异步的FIFO,握手协议和单一使能信号。每种方法都有其适用的场景和特点,需要根据具体情况进行选择。

通过正确应用这些同步设计机制,我们可以有效地解决CDC问题,提高系统的可靠性和性能。同时,在设计过程中还需要注意不同方法的优缺点,综合考虑设计的复杂性、时序要求和资源消耗等因素。通过科学合理的设计,我们能够克服CDC带来的挑战,实现数字系统的稳定运行。

审核编辑:汤梓红

-

数字电路中常见组件2025-01-24 1986

-

理解STM32控制中常见的PID算法2023-10-17 3614

-

直线导轨使用中常见的问题有哪些2023-08-03 2145

-

PCB设计工作中常见的错误有哪些?2023-05-23 2363

-

XDC约束技巧之CDC篇2023-04-03 3747

-

平衡小车在移植过程中常见的问题有哪些?2021-11-10 1489

-

控制总线中常见的控制信号包括哪些2021-08-11 5098

-

HDMI I/O设计和测试中常见的问题?怎么解决?2021-06-02 1703

-

在无线移动数据接收中常见的问题2021-04-14 1643

-

嵌入式测控系统中常见的数字滤波算法有哪些?2021-04-12 1391

-

电源中常见的故障现象如何维修2021-03-11 1895

-

如何评估MEMS陀螺仪信号中常见噪声源?2021-03-08 3252

-

FPGACPLD中常见模块设计精华集锦2012-08-17 4233

-

网络设备中常见术语含义及故障分析2011-12-27 15259

全部0条评论

快来发表一下你的评论吧 !