FPGA时序约束之时序路径和时序模型

可编程逻辑

描述

2 时序路径

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

片间路径是指FPGA芯片与外围芯片的物理路径;

片内路径是指FPGA芯片内部根据设计的代码所实现的路径;

时序约束和时序分析所关注的是片间路径,如下图所示;

3 时序模型

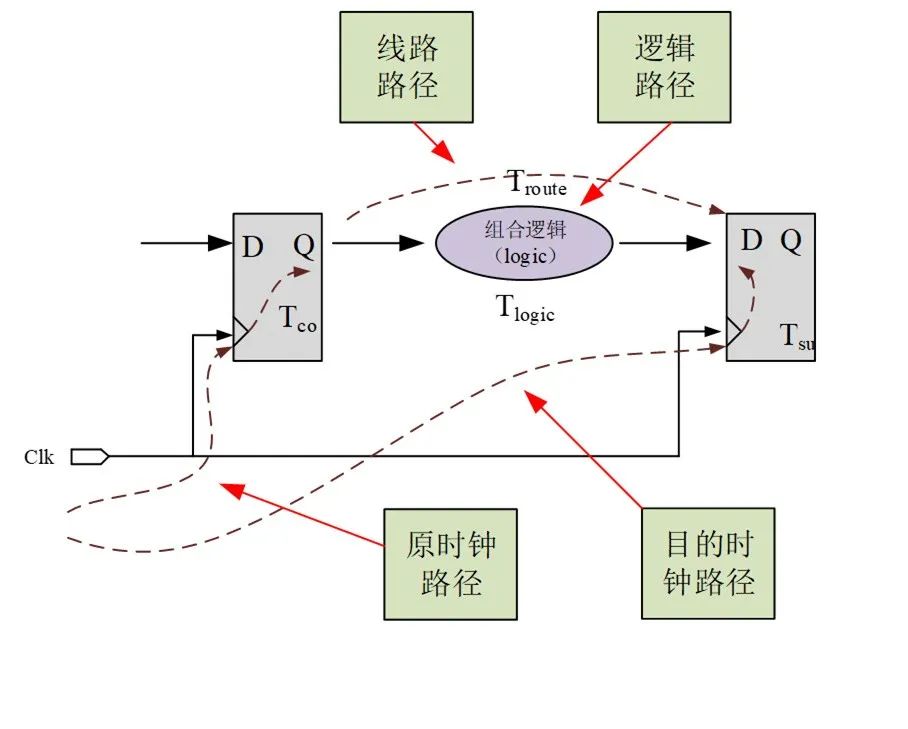

FPGA的典型的时序模型如下图所示,完整的时序路径包括包括源时钟路径、传输路径、组合逻辑和目的时钟路径,也可以表示为触发器(FF)+线路(Route)+组合逻辑(Logic)+触发器(FF)的模型。

根据上图的时序模型,在进行时序电路设计时,时序需满足一定的要求,图中该路径的建立时间时序要求为:

Tclk≥Tco+Tlogic+Troute+Tsetup-Tskew;

其中,

Tclk 为时钟周期;

Tco为发送端寄存器时钟到输出时间;

Tlogic为组合逻辑时间延迟;

Troute为两级寄存器(两个寄存器)之间的布线延迟;

Tsetup为接收端寄存器建立时间;

Tskew为两级寄存器的时钟歪斜(即到达寄存器的时间偏差),其值等于时钟同边沿到达两个寄存器时钟端口的时间差。

上述为建立时间的时序要求。下面讲述一下保持时间时序要求:

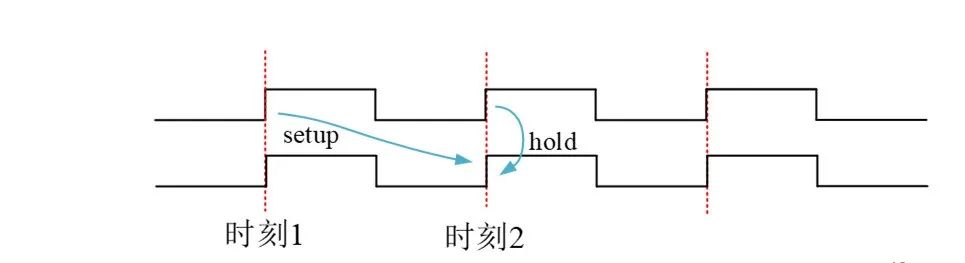

保持时间相对来说要难理解,是指数据在时钟上升沿后需保持的最小时间量,这里已经在上一篇讲解过。通俗意思是说寄存器1的数据不能太快到达寄存器2,以防止寄存器2采集新数据太快而导致原来的数据被覆盖。

NOTE:保持时间约束是对同一个时钟边沿约束,而不是对下一个时钟进行约束。

详细描述:如上图,寄存器2在边沿2时刻刚刚捕获寄存器1在边沿1时刻发出的数据,若寄存器1在边沿2时刻发出的数据过快到达寄存器2,则会冲掉前面的数据,因此保持时间约束的是同一个边沿(这里要注意,实际是同一个时钟源,所以说是同一个边沿)。

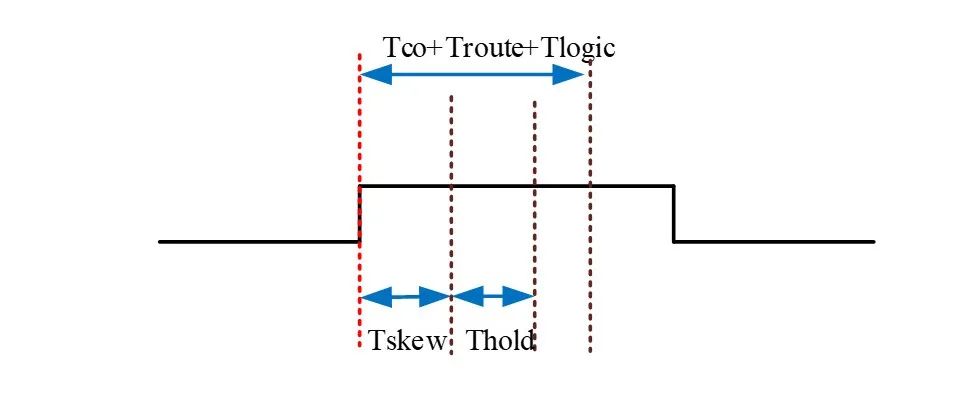

在时钟沿到达之后,数据要保持Thold的时间,如上图所示(图中为表示方便加大了时序宽度,实际上比较小),要满足以下公式:

Tco+Tlogic+Troute≥Tskew+Thold

-

FPGA时序约束之设置时钟组2025-04-23 1706

-

FPGA I/O口时序约束讲解2023-08-14 3268

-

FPGA时序约束理论篇之时序路径与时序模型2023-06-26 1226

-

FPGA时序约束之伪路径和多周期路径2023-06-12 3246

-

FPGA的IO口时序约束分析2022-09-27 2549

-

FPGA的时序input delay约束2022-07-25 4033

-

FPGA设计之时序约束2022-03-18 2380

-

FPGA设计之时序约束四大步骤2022-03-16 4138

-

FPGA案例之时序路径与时序模型解析2020-11-17 3983

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2899

-

FPGA时序约束基本理论之时序路径和时序模型2020-01-27 3457

-

FPGA中的时序约束设计2017-11-17 3102

-

FPGA时序约束方法2015-12-14 1015

-

时序约束与时序分析 ppt教程2010-05-17 952

全部0条评论

快来发表一下你的评论吧 !