FPGA时序约束之Skew讲解

可编程逻辑

1397人已加入

描述

3 Skew讲解

针对第2章节时序路径中用到skew,在本章再仔细讲解一下。

Skew分为两种情况:一是positive skew(上升沿偏斜),一是negative skew(下降沿偏斜)。

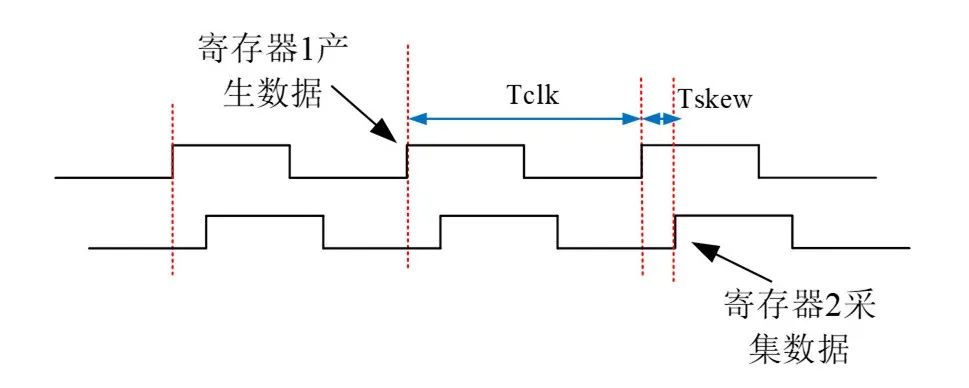

positive skew(上升沿偏斜)可以参考下图表示,实际上是增加了后一级寄存器的触发时间。比如寄存器1产生数据后,寄存器2在Tclk+Tskew后才能采集到数据。

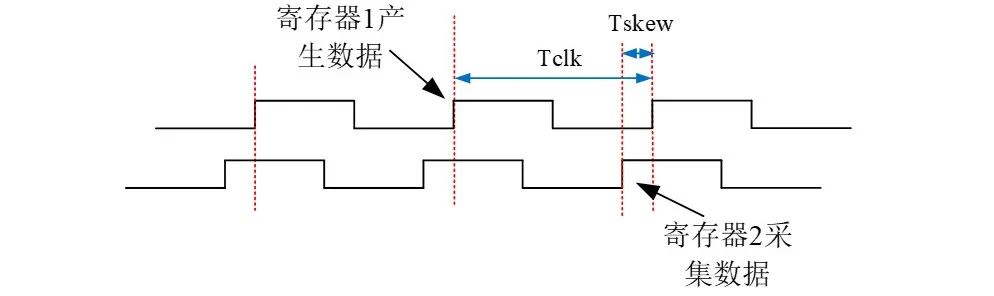

相比于positive skew(上升沿偏斜),negative skew(下降沿偏斜)相当于减少了后一级寄存器的触发时间,比如寄存器1产生数据后,寄存器2在Tclk-Tskew后就能采集到数据。可通过下图理解:

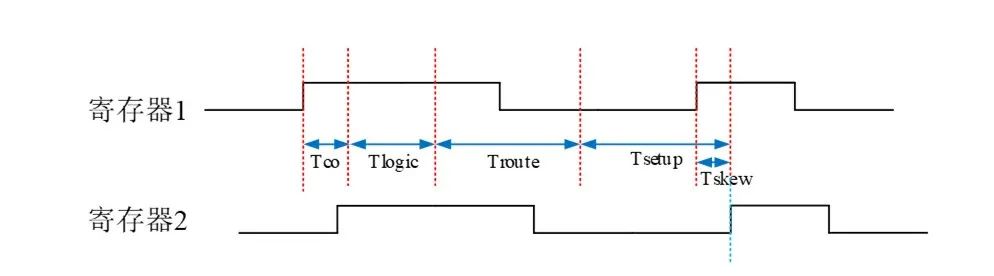

针对于第2章FPGA时序约束理论篇讲解的时序路径(包括公式计算),可以用下面这个图来表示时序关系就更加容易理解。其中直观的表现了要减去Tskew的原因。

Tclk≥Tco+Tlogic+Troute+Tsetup-Tskew

NOTE:

1.在系统稳定后,均是是positive skew的状态,但即便是positive skew,综合工具在计算时序时,也不会把多出来的Tskew算进去。相当于还是按照严格标准去满足时序;

2.对于同步设计Tskew可忽略(认为其值为0),因为FPGA中的时钟树会尽量保证到每个寄存器的延迟相同。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA时序约束--基础理论篇2023-11-15 883

-

FPGA时序约束之建立时间和保持时间2023-08-14 2429

-

FPGA时序约束的原理是什么?2023-06-26 1433

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4567

-

FPGA主时钟约束详解 Vivado添加时序约束方法2023-06-06 13067

-

FPGA的IO口时序约束分析2022-09-27 2560

-

FPGA的时序input delay约束2022-07-25 4059

-

时序约束系列之D触发器原理和FPGA时序结构2022-07-11 6632

-

详解FPGA的时序input delay约束2022-05-11 5209

-

FPGA设计之时序约束2022-03-18 2399

-

深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果2017-11-24 6160

-

FPGA中的时序约束设计2017-11-17 3120

-

FPGA时序约束方法2015-12-14 1024

全部0条评论

快来发表一下你的评论吧 !