SRAM型FPGA的抗辐照加固设计

可编程逻辑

描述

让一颗SRAM型FPGA在太空长期稳定运行的难度,就类似练成独孤九剑的难度。

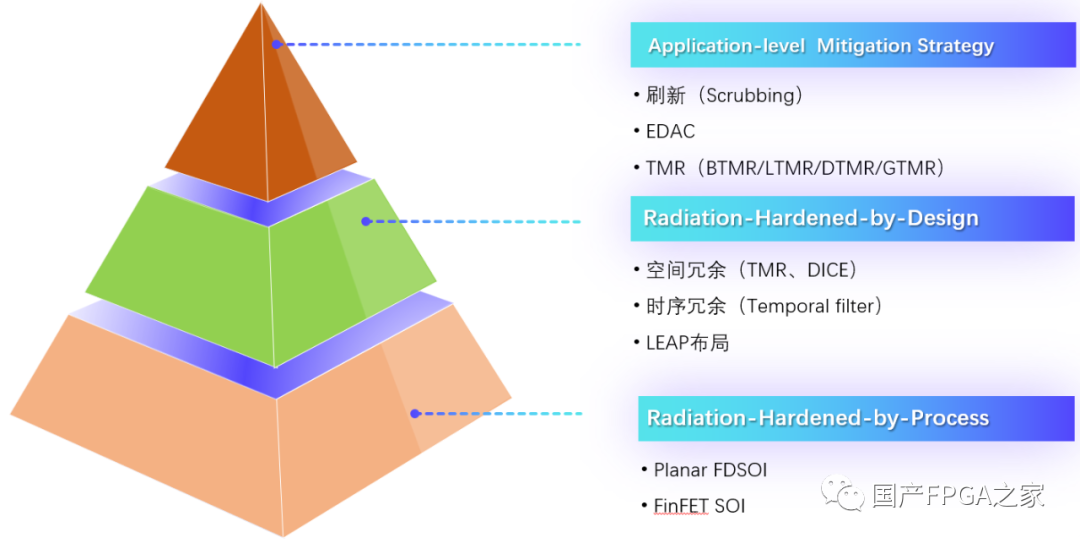

SRAM型FPGA的抗辐照加固设计包括芯片工艺、Die加固和芯片应用层面加固。本文主要讨论芯片应用层面的加固方法,包括外置刷新和FPGA内部软件抗辐加固。

今日登坛做法,贫道首先从FPGA资源角度来介绍不同资源对应的解决办法,更清楚的表明外置刷新和三模冗余是解决SEE的有效办法。然后从解决办法到解决措施,讲具体是如何去实现刷新和三模冗余。最后是介绍如何验证刷新是否有效,如何验证三模冗余是否有效。

图1 SRAM型FPGA的抗辐照加固设计

01

SRAM型FPGA的资源及其发生SEU故障分类

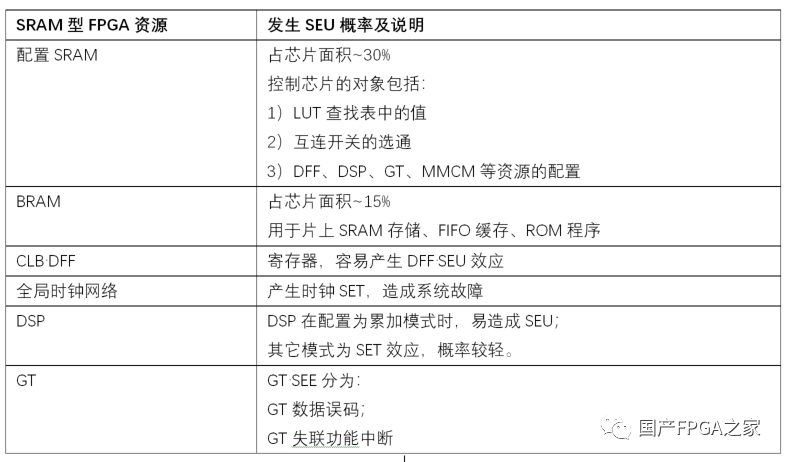

如表1所示,SRAM型FPGA资源包括配置SRAM,内部的块RAM(BRAM),触发器CLB DFF,全局时钟网络,DSP和高速串行接口GT。每种资源都有其特点和对应SEU解决办法。

表1 SRAM型FPGA的资源及其发生SEU概率说明

1.1 配置SRAM(CRAM)

CRAM的特点占芯片面积达到30%,发生SEU的概率很大。由于CRAM里面含有很多无效位,因此CRAM发生SEU可能不会导致FPGA功能异常。但是随着时间的累积,越来越多的CRAM发生SEU,那么FPGA功能一定会错。这种累积错误可以通过刷新Scrub来解决。

有两点值得注意,第一个是累积错误是在刷新周期的下一个周期解决,在用户时钟周期内该累积错误可能被时序电路捕获,提升刷新频率有助于缓解该问题。第二个是即使累积错误是在刷新周期的下一个周期解决,累积错误带来的时序逻辑错误也可能没有办法恢复。

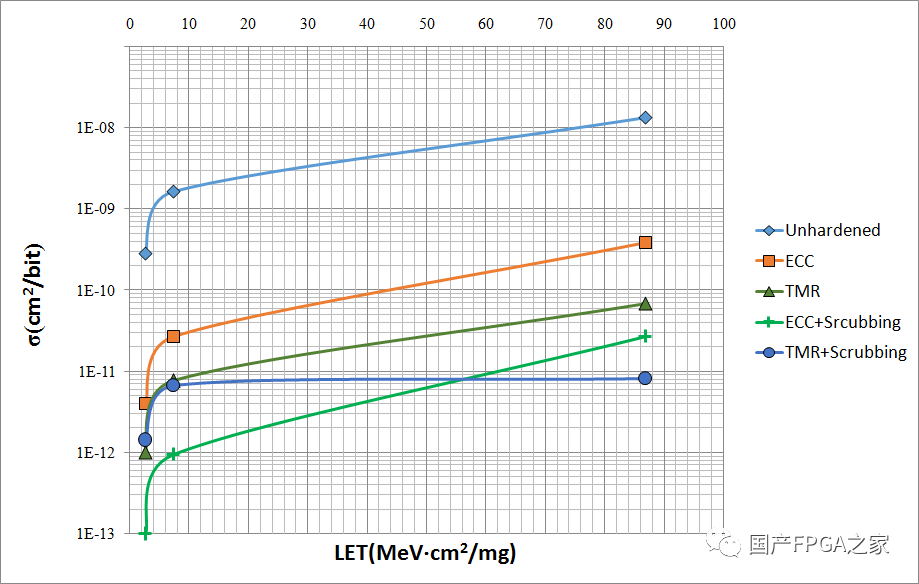

因此仅仅使用刷新的方法是不能解决CRAM的SEU所带来的功能异常问题,推荐刷新+三模冗余的方法来提升FPGA可靠性。

图2 CRAM SEU带来的时序逻辑错误

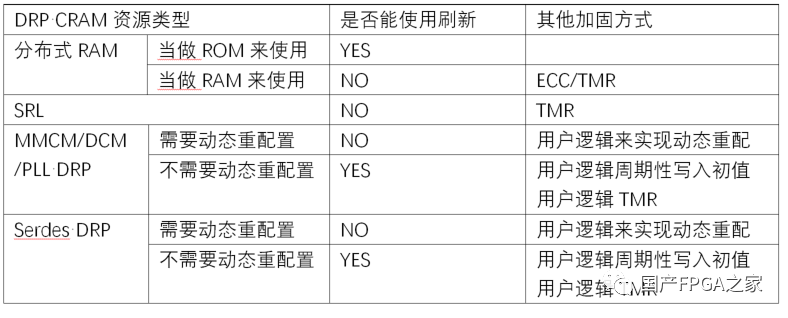

DRP CRAM指的是用户可以使用的CRAM资源,包括分布式RAM、移位寄存器SRL、MMCM/DCM/PLL DRP参数、高速串行接口Serdes DRP 参数等。DRP CRAM一般不能被刷新,因为一旦刷新就会恢复成初始值,影响用户功能。但是如果DRP CRAM的值是固定不变的,那么则可以通过刷新来进行加固。

1.2 BlockRAM

FPGA内部含有大量的BlockRAM资源,占芯片面积也比较大,而且无法刷新。如果BRAM发生了SEU那该怎么办呢?

如果BRAM用作SRAM缓存或者FIFO缓存且允许出错的情况下,那么BRAM可以不做加固,不允许出错或者可靠性有要求的情况下,BRAM也可以进行加固。如果BRAM用作储存ROM程序,那么BRAM就必须进行加固。

BRAM错误屏蔽加固的方法包括ECC和TMR,这两种方法无法修复错误本身。ECC基于SECEDC纠一检二码只能纠正SBU错误,无法纠正错误累积导致的MBU。TMR无法解决错误累积导致的TMR两份以上同一地址同一位同时失效的问题。

BRAM错误修复加固的方法包括ECC回写和TMR回写,可以部分或者完全纠正错误数据并回写正确数据。ECC回写基于Read-Modify-Write机制可纠正SBU数据并回写正确数据。TMR回写基于确定性方式扫描RAM存储空间,可纠正并修复SBU/MBU数据错误,避免数据错误累积,可靠性最高。

图3 系列FPGA BRAM不同加固方案翻转数据比较

1.3 CLB DFF

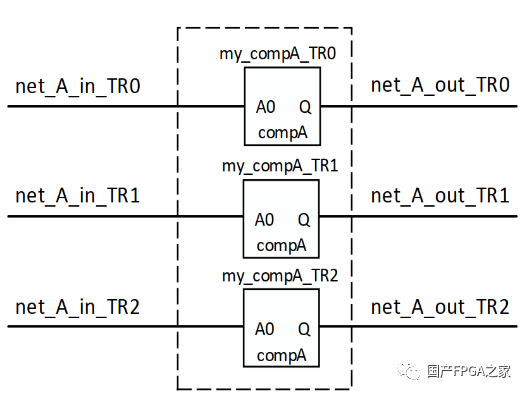

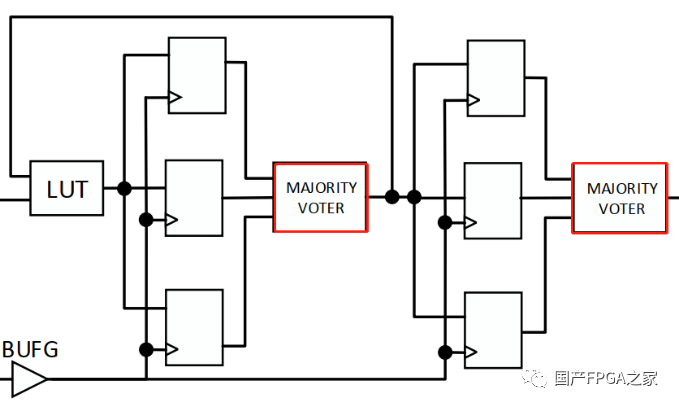

触发器的有效加固方法是三模冗余,根据可靠性高低,细分为“3Reg+3Voter”,“3Reg+1Voter”和“3Reg”三种。

流水寄出器如果允许短暂出错,那么可以不做加固,需要增强可靠性可以选择“3Reg+1Voter”或“3Reg”。

图4 TMR-“3Reg”

图5 TMR“3Reg+1Voter”

Feedback Loop Register特别是状态机,可靠性要求很高,推荐采用“3Reg+3Voter”。

图6 “3Reg+3Voter”

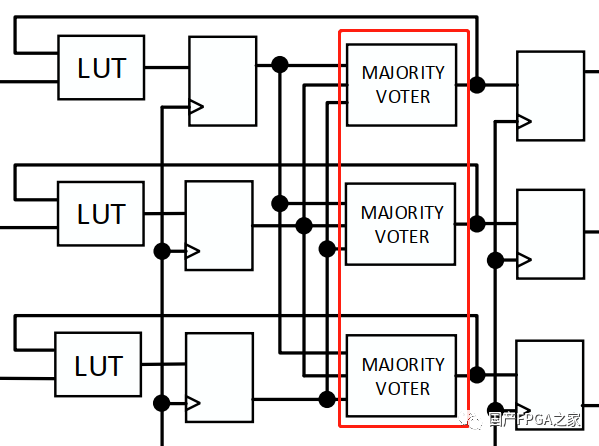

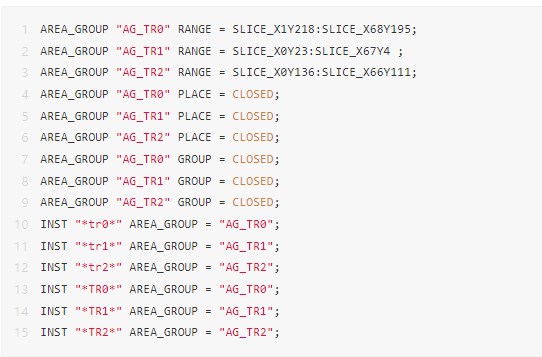

防止TMR中两路Reg同时翻转,还可以采用物理隔离的方法,简单有效的方法一是时钟网络做三模,那么两路Reg由于时钟网络不一样,会被放在不同的Slice中去。方法二是使用Area Group约束,UCF中的写法如下:

图7 Area Group约束解决MBU问题

1.4 高速串行接口SerDes

Serdes的加固方案比较复杂,篇幅有限,主要说明一下Serdes里面的参数该如何加固。Serdes里面的参数特别多,而且很多都是可动态配置的,属于DRP CRAM。

当发现Serdes功能异常的时候,设计师可以通过用户逻辑对DRP CRAM进行重配置,然后对Serdes进行复位操作来恢复功能。

02

SRAM型FPGA SEU解决措施

2.1 外置刷新芯片方案

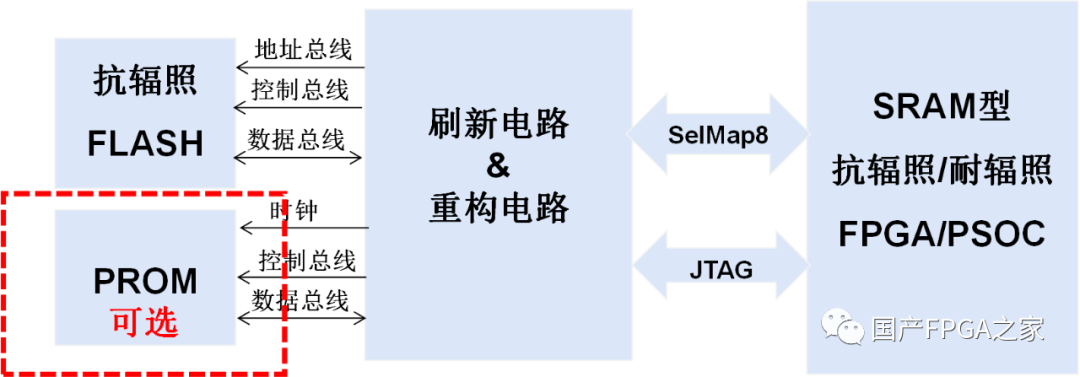

图8 外置刷新方案

刷新分为外部刷新和内部刷新,关于两者比较细节,将在后续的文章中进行描述。今天主要介绍外部刷新方案,通常用外置专用刷新芯片或者反熔丝FPGA来实现外部刷新。

专用刷新芯片必须是抗辐照的,优点是刷新和重构功能已实现、设计简单。反熔丝FPGA的优点是可以实现用户自定义的功能。反熔丝FPGA的缺点设计复杂度高,PCB面积大,而且一次烧写增加了设计风险。

值得一提的是听说最近国内出了一款专用刷新芯片,功能比较强大,支持各种系列的FPGA,支持大容量存储器,支持1553B、CAN等多种重构接口,而且还能实现用户自定义的功能,可以说是业界佼佼者。

2.2 FPGA软件抗辐照加固设计方案

抗辐照加固软件设计的主要功能是实现三模冗余,实现过程可分为代码层面和网表层面。下面就两个不同的层面进行设计的优缺点进行说明。

代码层面大体有两种具体的做法:

第一种是设计师把关键的模块代码复制三份+表决器,这种方法的优点就是简单和灵活。缺点是模块越多设计效率越低,模块越大可靠性越低以及TMR代码存在被工具优化的可能。

第二种做法是借助第三方的EDA工具,可以解决可靠性低和代码被优化的问题,能提高设计效率,但是由于面向的是代码层面,对IP的加固没有办法实现,支持的应用场景受限。第三方的EDA工具更合适的定位应该是一种辅助,帮助设计师完成最终的设计,不能完全交给其来实现。

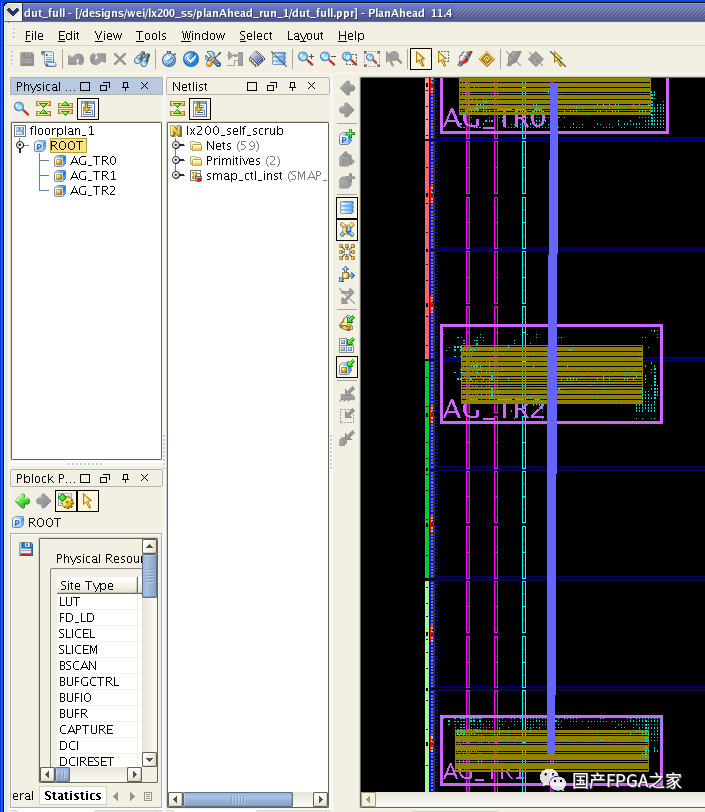

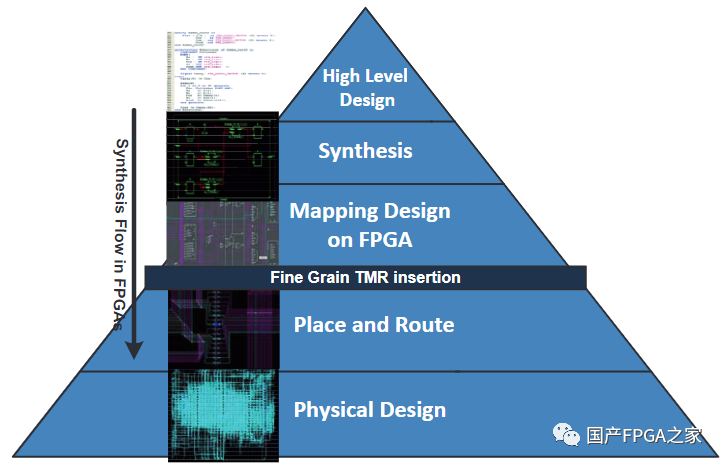

网表层面加固借助专用的高可靠设计软件,这种方法的优点是能够面向所有的应用场景。由于网表层面能够进行细粒度的三模冗余,而且加固后不会被优化掉,因此可靠性最高。高可靠设计软件的EDA效率、部分三模冗余的支持能力与主流的FPGA EDA软件的兼容程度,大体这三个方面会决定整个设计流程可实现性、效率和用户体验度。高可靠设计软件做的好的话,那整个加固设计可以完全交由其来实现,工程师会觉得福利满满。

图9 网表层面实现加固设计

03

SRAM型FPGA SEU解决措施效果验证

3.1 刷新有效性验证

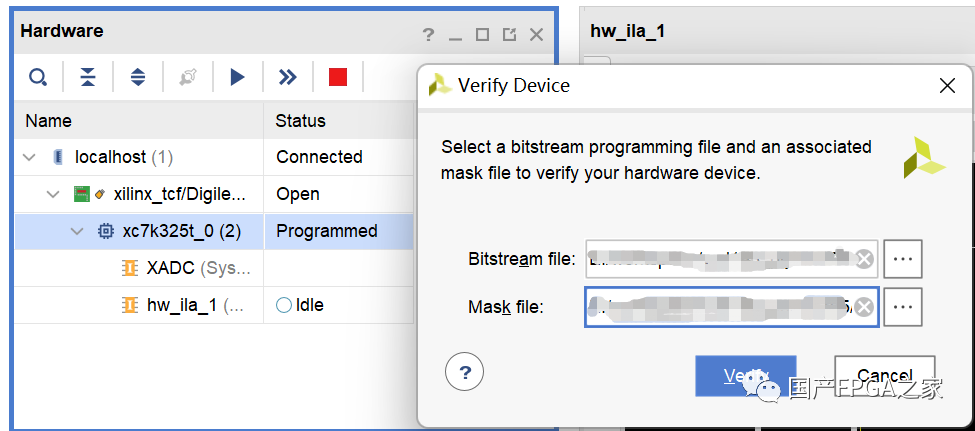

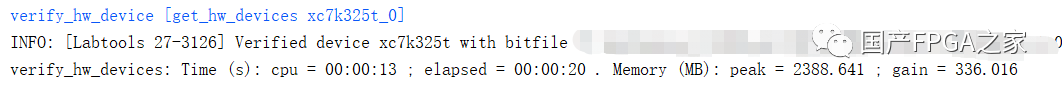

3.1.1)Verify操作:

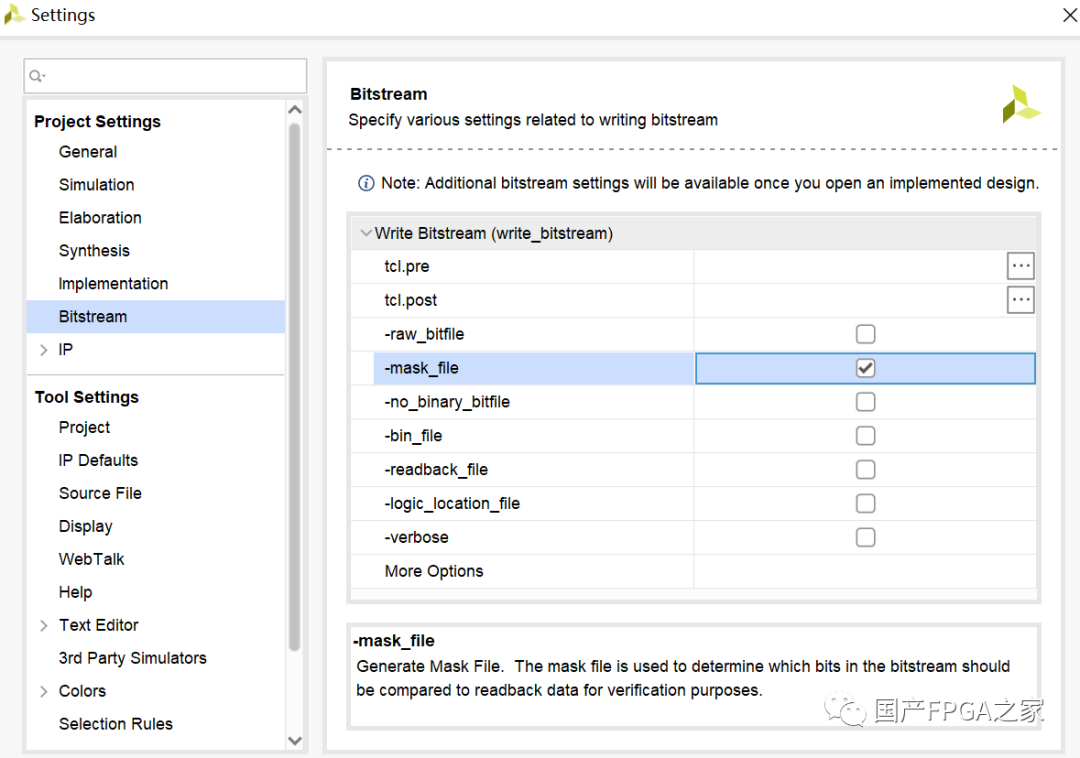

通过JTAG执行Verify操作可以知道FPGA里面的位流和Golden位流是否一样,是很常见的验证手段。要执行Verify操作,首先在生成位流的时候,得在settings里面勾选-mask_file。

图10 mask文件生成方法

选中device右键verify_device,执行完在Tcl_console看日志。

图11 执行verify device操作

图12 verify验证位流正常

图13 verify验证位流错误

完整的验证刷新有效的过程,首先执行一次verify操作确认加载是成功的。然后通过故障注入工具注入错误,执行第二次verify操作可以看到verify结果报错。接着执行完刷新操作,第三次执行verify操作可以看到verify结果正确。

3.2 三模有效性验证

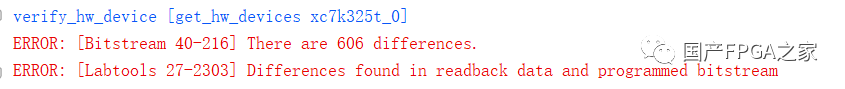

3.2.1)网表级功能仿真

三模后的网表功能仿真结果应该和三模前的网表仿真结果一样。如果结果不一样,结合仿真也可以找到出问题的地方,迭代三模设计。

高可靠设计软件会在软件层面做大量的案例测试,保证形式验证结果一样,功能仿真结果肯定也一样。

在Vivado中执行仿真的方法如下:

首先open the synthesized design,然后再tcl console中输入:

3.2.2)网表ECO功能验证

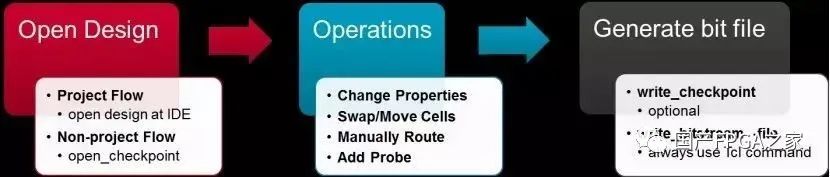

Vivado IDE ECO:

图14 Vivado ECO流程

Vivado软件的ECO功能很强大,不再一一描述了。验证三模功能是否有效,可以简单修改TR0电路里面LUT里面的值,这样行为和TR1/TR2不一样,但是通过多数表决器Voter,输出结果还是正确的。

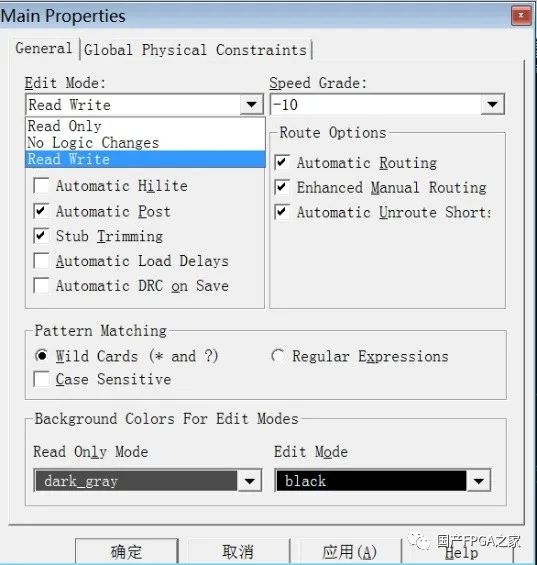

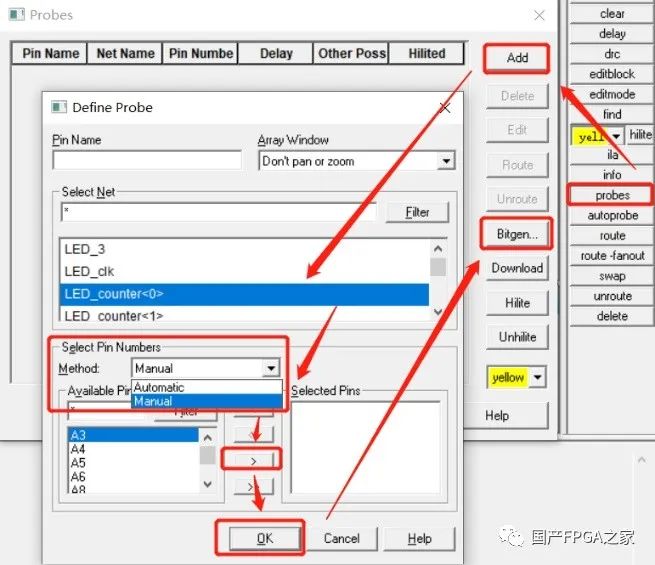

ISE: FPGA_EDITOR

修改网表编辑模式为Read Write;

通过IO观测内部信号;

通过ncd2xdl和xdl2ncd命令修改ILA观测内部信号;

快速生成bit文件,验证功能。

图12 FPGA editor的使用

战术总结

抬眼望去,对面零星的几盏烛火也熄灭了,又是连肝几个晚上,给各位兄弟姐妹分享了SRAM型FPGA加固的措施,目前从实际效果上来看,外置刷新和三模冗余仍是目前解决SRAM型FPGA SEU的有效办法。

审核编辑:刘清

-

AS32S601ZIT2型MCU:基于RISC-V架构的抗辐照设计与试验评估2025-09-25 1188

-

抗辐照加固CANFD芯片:以车规级设计提升商业航天系统可靠性2025-05-30 1309

-

芯片封装抗辐照技术研究2025-05-29 4409

-

SRAM型FPGA在轨会遇到的问题及其影响2023-08-11 3803

-

FPGA在航天领域有什么应用2020-07-07 2812

-

基于软件的空间辐照下FPGA可靠性设计方法2017-11-24 3035

-

基于TDICE单元的SRAM抗SEU加固设计2017-01-07 814

-

反熔丝型FPGA单粒子效应及加固技术研究2016-01-04 676

-

Xilinx SRAM型FPGA抗辐射设计技术研究2012-08-17 3045

-

反熔丝FPGA器件γ剂量率辐射效应规律探讨2010-04-22 2526

-

集成电路应用与抗辐射加固(上)2009-08-27 1139

全部0条评论

快来发表一下你的评论吧 !