简述无源/有源晶振的布局布线要点

描述

OSC-9---晶振的Layout

引言:晶振内部结构比较复杂,如果连接不妥当或者布线错误,就会影响晶振不起振或者EMC测试fail,从而导致产品不能使用。因此晶振电路的PCB设计非常重要,本节主要简述无源/有源晶振的布局布线要点。

1.布局

1#:主体位置

晶振内部是石英晶体,如果不慎掉落或受不明撞击,石英晶体易断裂破损,所以晶振的放置远离板边,靠近MCU/SOC的位置布局。为了安全考虑,板卡的地和金属外壳或者机械结构常常是连在一起的,如果晶振布在板卡的边缘,晶振与参考接地板会形成电场分布,而板卡的边缘常常是有很多线缆,当线缆穿过晶振和参考接地板的电场,线缆会被干扰。而晶振布在离边缘远的地方,晶振与参考接地板的电场分布被PCB板的GND分割,分布到参考接地板电场大大减小了。

2#:电容位置

有源晶振的去耦电容应尽量靠近晶振的电源管脚,如果多个耦合电容,按照电源流入方向,依次容值从大到小摆放。无源晶振的负载电容靠近晶振本体,减少寄生电容的影响。

3#:独立性

尽可能保证晶振周围的没有其他元件,建议这个距离为300mil,约为7.6mm,实际4-5mm左右也可以接受,防止器件之间的互相干扰,影响时钟和其他信号的质量,

2.布线

1#:走线短

在电路系统中,高速时钟信号线优先级最高,一般在布线时,需要优先考虑系统的主时钟信号线。时钟线是敏感信号,频率越高,要求走线尽量短,保证信号的失真度最小,与其它信号需20mil间距,最好使用Ground trace与其他信号隔离,避免时钟线干扰其他信号。

2#:外壳接地

晶振的外壳必须要接地,除了防止晶振向外辐射,也可以屏蔽外来的干扰。

3#:晶振底下铺地

晶振铺地可以防止干扰其他层,不满足铺地也需要粗走线包裹。

4#:晶振底下不要布线

晶振周围5mm的范围内不要布线和其他元器件,主要是防止晶振干扰其他布线和器件。底下尽量不要走线,一定要走线的话,不能走线进晶振pin脚周围50mil之内,尤其避免高速信号。

5#:有源晶振输出不能接长线

时钟源通常是系统中最严重的EMI辐射源,频率高,是高速电路,时钟上升沿陡高速频谱含量越多,如果接长线,其结果是长线就成了天线,这在很多应用中是不允许的,所有时钟源都必须尽量靠近相关器件,必要时用多个时钟源,不得以下可以采用多层PCB将时钟连线屏蔽。有源晶振的输出一般是标准TTL规格,至于能驱动多少芯片要看这些芯片的特性。关于晶振的选择,如果你的系统能工作在25M,就尽量不要选50M的晶振。

6#:过孔

晶振信号线尽可能不穿孔,因为一个过孔会有大约0.5pF的寄生电容,走线粗细要一致。

3.保护器件

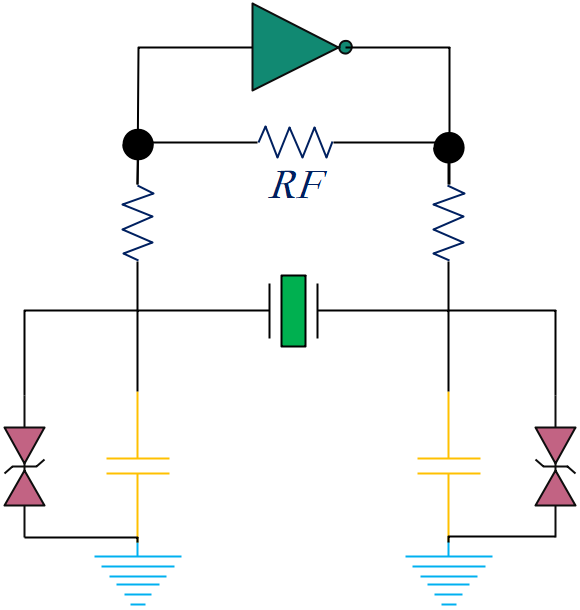

图9-1:晶振增加ESD保护器件

当使用ESD保护器件时,需要器件的寄生电容考虑在内合并计算CL,以最大限度地降低更高频带信号的衰减和频率偏移。

4.无源晶振Layout示例

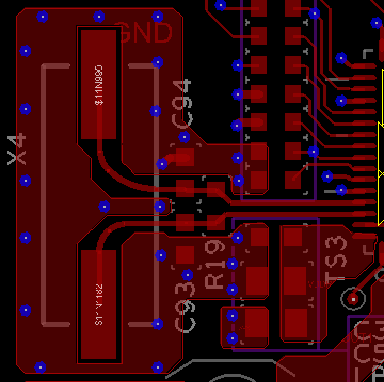

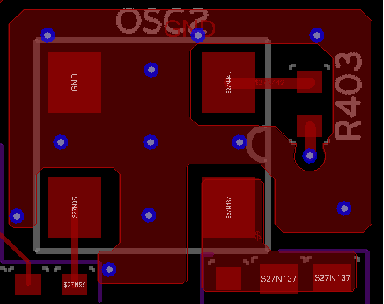

顶层:图9-2所示,晶振顶层的最好策略是铺铜包地(如果有的话也可以连接其他大面积GND铜皮,也可以独立GND铜皮),效果比走线包地效果更佳。铺铜之后,打上过孔阵列,与其它层的铜皮进行良好连接,形成一个密集的GND三维多层法拉第笼。

图9-2:无源晶振顶层走线范例

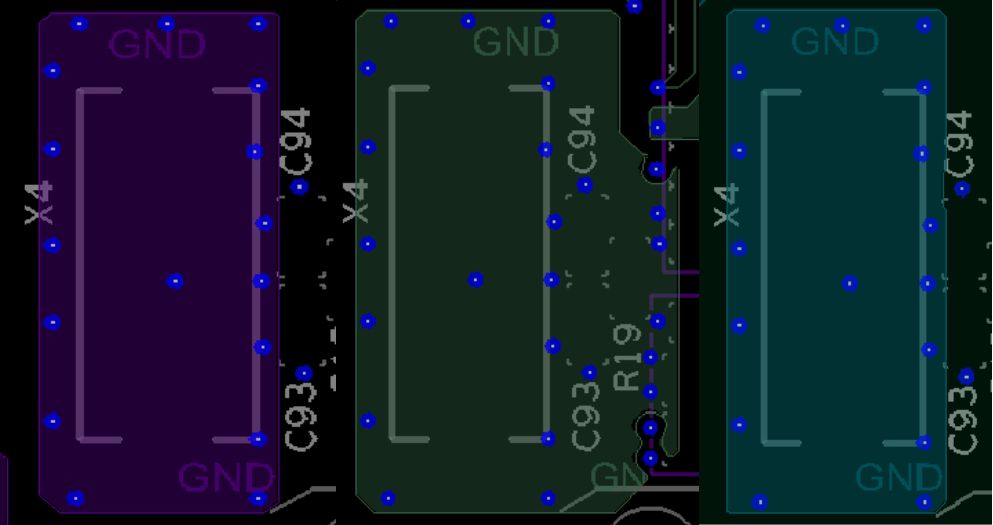

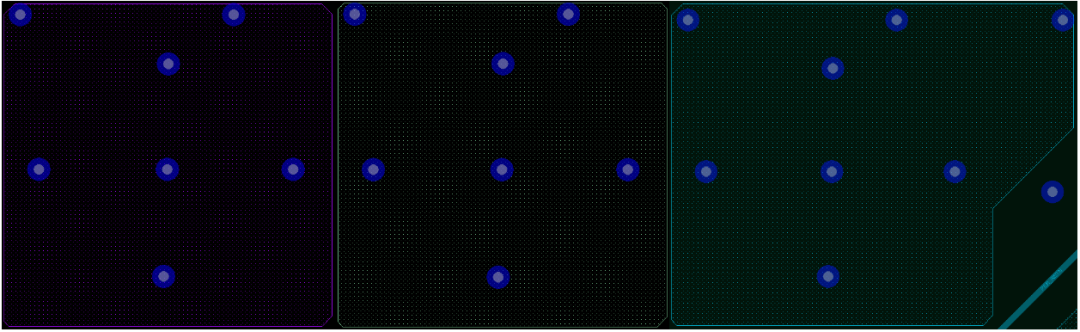

中间层和底层:因为晶振底下的投射区域不能走线,不包括GND层和POWER层(GND层完整覆盖,POWER层也完整覆盖,不用挖空),所以就将投射区域的GND过孔用铜皮连接成shape,其他层也类似如图9-3处理。

图9-3:无源晶振中间层/底层范例

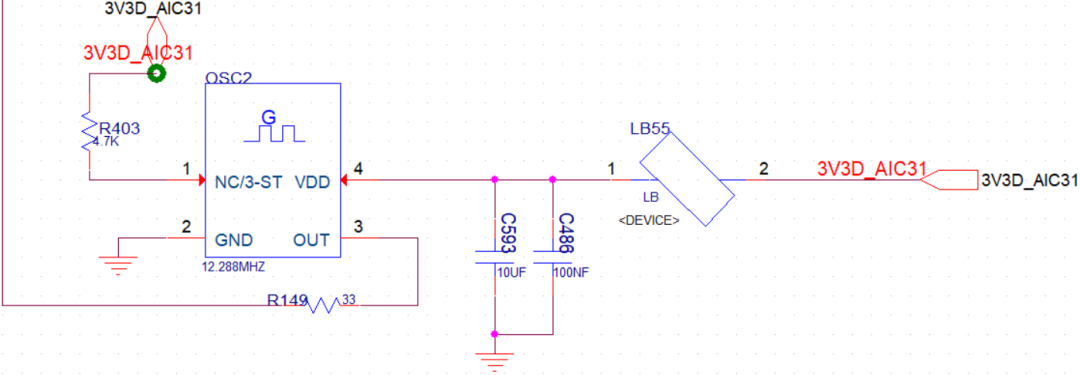

5.有源晶振Layout示例

图9-4:有源晶振电路

顶层:如图9-5,去耦电容靠近晶振的电源管脚,有源晶振同样建议使用铜皮GND包裹策略,时钟信号直连,尽量不要过孔换层。

图9-5:有源晶振顶层走线范例

中间层和底层:GND铜皮覆盖投射区域,过孔立体连通。

图9-6:有源晶振中间层/底层范例

-

晶振的两种主要类型:有源晶振和无源晶振2024-11-18 2394

-

有源晶振和无源晶振如何辨别2024-08-28 3482

-

无源晶振和有源晶振的原理?2024-05-09 3566

-

有源晶振和无源晶振的区别2024-04-15 2844

-

有源晶振和无源晶振的区别是什么2024-02-16 5808

-

有源晶振和无源晶振能够互换吗?2024-01-26 3741

-

对无源/有源晶振的疑问2022-11-04 4368

-

无源晶振与有源晶振的结构区别图解2022-07-19 7794

-

有源晶振和无源晶振可以互换吗?2022-06-17 13221

-

有源晶振与无源晶振相关资料下载2021-05-25 2073

-

如何区分有源晶振与无源晶振?区别是什么?2020-11-19 44740

-

如何区分有源晶振和无源晶振2020-01-27 18647

-

有源晶振与无源晶振2016-05-06 2227

-

无源晶振与有源晶振的比较2012-10-07 7561

全部0条评论

快来发表一下你的评论吧 !