FPGA芯片内部结构解析(1)

可编程逻辑

描述

FPGA芯片内部逻辑

a. Xilinx FPGA的可配置逻辑块

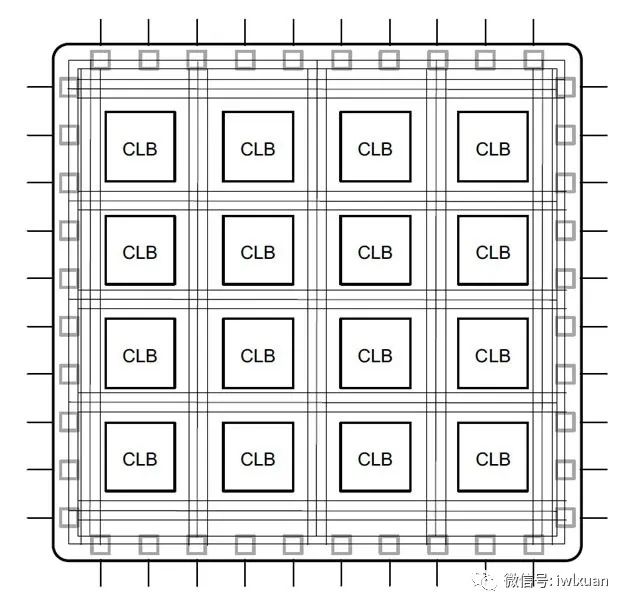

以Xilinx主流的7系列为例,一颗FPGA内部通常都会有数千到数十万不等的可配置逻辑块(Configurable Logic Block,简称CLB)

呈矩阵排布的CLB就构成了最基本的FPGA逻辑资源的架构

Xilinx 7系列的可配置逻辑块可以有效的支持以下特性

使用6输入查找表技术

可选的2个5输入查找表功能

可实现分布式RAM和移位寄存器功能

用于运算功能的专用高速进位链

支持资源高利用率的丰富复用开关

FPGA内部丰富的可编程逻辑块

a.1 Xilinx FPGA的可配置逻辑块——CLB内部结构与Slice

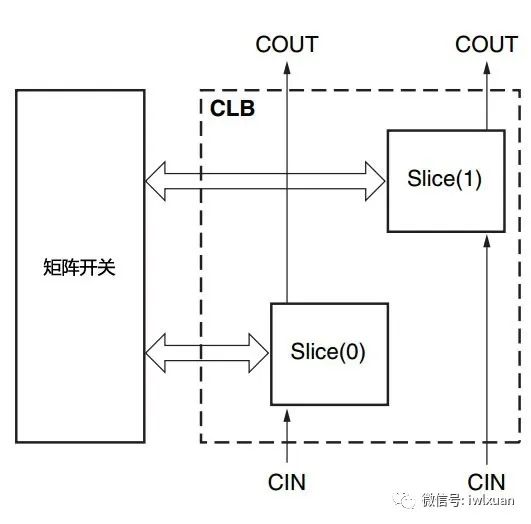

从微观角度看,CLB内部主要由2个更小的单位Slice所组成

每个Slice都有独立的高速进位链以及独立的布线通道连接到矩阵开关,通过矩阵开关可以实现Slice与FPGA大布线池之间的灵活编程

每个slice单元则包含了以下更小的功能块

4个逻辑功能发生器(或查找表)

8个存储单元(或触发器)

功能丰富的复用开关

进位链

CLB内部结构

a.2 Xilinx FPGA的可配置逻辑块——Slice内部结构单元

slice内部2个非常基本且重要的结构单元

6输入查找表(Look-up table,LUT):用于执行最基本的逻辑操作

触发器(Flip-Flop,FF):用于存储LUT操作结果的寄存器单元

对于Xilinx的7系列FPGA器件所使用的6输入查找表,通常也可以配置实现以下不同的应用功能

任何用户定义的6输入布尔运算功能

任何用户定义的2个5输入布尔运算功能,前提是2个输出分别对应的5输入是共用的

任何用户定义的2个3输入或少于3输入的布尔运算功能

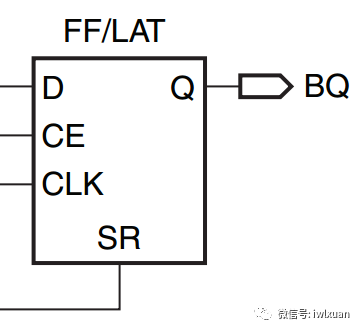

a.3 Xilinx FPGA的可配置逻辑块——触发器

触发器也是FPGA内部基本的存储单元

触发器单元通常用于配对LUT进行逻辑流水线处理和数据存储

基本的触发器结构包括了一个数据输入,一个时钟输入,一个时钟使能信号,一个复位信号和一个数据输出

触发器工作原理

数据输入端口上的任何值在每个时钟上升沿将被锁存并送到输出端口

时钟使能信号是为了使触发器能够连续多个时钟周期保持某个固定电平值

时钟使能信号拉高时,新的数据才会在时钟上升沿被锁存到数据输出端口上

触发器结构

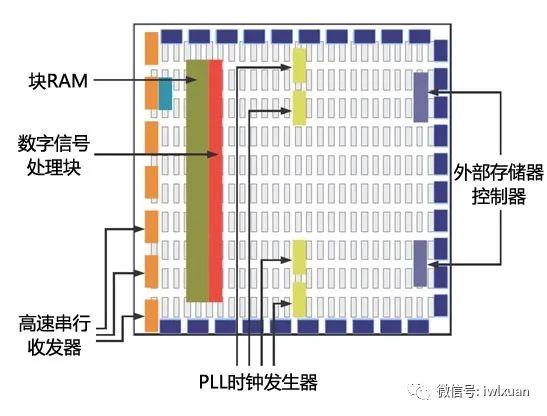

b. Xilinx FPGA的内部结构

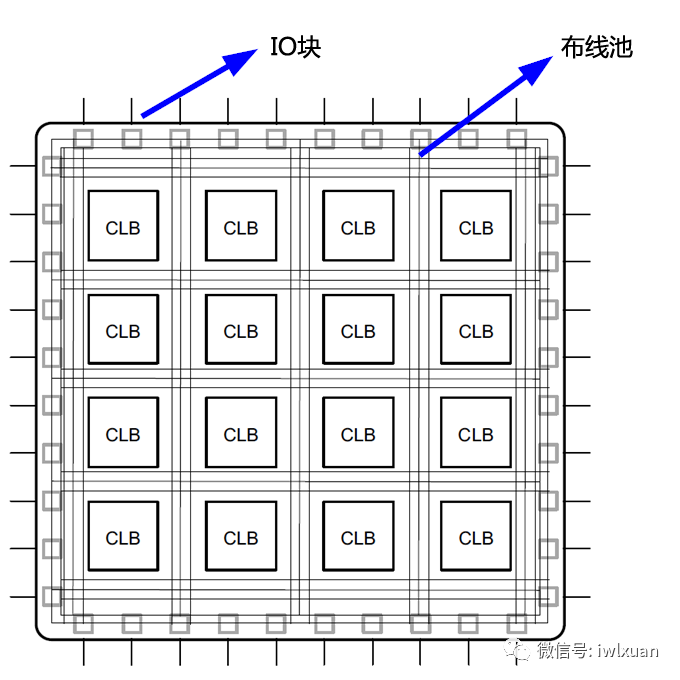

b.1Xilinx FPGA的内部结构——IO块、布线池和CLB

围绕在CLB周围丰富的行、列走线我们称之为布线池,它用于衔接FPGA的各个CLB以及其它相关的资源

在FPGA芯片四周的小矩形以及延伸出去的短线,则是FPGA和外部芯片接口的IO块的示意

IO块、布线池和CLB

b.2Xilinx FPGA的内部结构——丰富的其它FPGA资源

以成块出现的FPGA内嵌存储器(块RAM)

用于产生不同时钟频率的锁相环(PLL时钟发生器)以及相应的时钟布线资源

高速串行收发器

外部存储器控制器(硬核IP)

用于实现数字信号处理的乘累加模块(DSP Slice)

模拟数字转换模块(Xilinx FPGA器件特有的Analog-to-Digital Converter,简称XADC)

-

fpga内部主要结构及其功能分析(Kintex-7FPGA内部结构)2023-08-24 3556

-

芯片封装内部结构2008-06-11 91839

-

学fpga的内部结构和各接口实验怎么学2014-05-10 2754

-

信号在fpga内部结构上运行的最大频率是?2019-01-30 4404

-

DAC0832芯片内部结构框图2009-01-14 7622

-

CX20106内部结构框图2010-01-06 2819

-

CX20106 内部结构框图2010-01-08 3877

-

元件的内部结构2017-03-04 1411

-

详细分析半导体芯片内部结构2019-01-18 18070

-

FPGA内部结构的详细介绍2020-09-17 1401

-

STM32学习(1)-资料查找,STM32简介,STM32选型以及芯片内部结构图2021-11-26 2227

-

交叉导轨的内部结构2023-08-16 2459

-

电源芯片内部结构是什么样的2024-01-05 5114

-

集成芯片内部结构图2024-03-19 5137

-

电压调节芯片SG3525内部结构及功能2025-03-21 1566

全部0条评论

快来发表一下你的评论吧 !