如何仅使用逻辑门和寄存器产生无毛刺输出的时钟切换?

描述

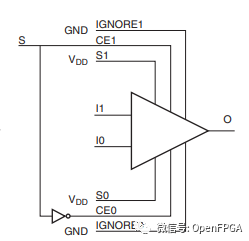

大部分开发者使用 BUFGCTRL 或 BUFGMUX进行时钟切换,它们在时钟切换上可以提供无毛刺输出。然而,了解所涉及的原理是有好处的。

当然,无论我们在同步逻辑中使用哪种技术,重要的是要确保在进行时钟切换时输出上没有毛刺。任何故障都可能导致下游逻辑的错误行为。

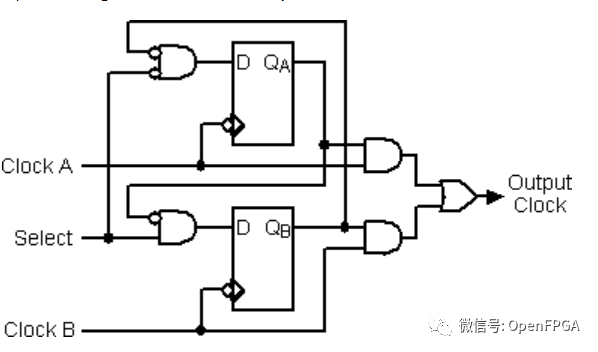

那么,让我们看看如何仅使用逻辑门和寄存器产生无毛刺输出的时钟切换。Peter 大神介绍了如下电路。

使用两个寄存器来存储选择信号的状态。这些状态在时钟的下降沿更新,并且取消选择的寄存器将其时钟保持在复位状态。由于下降沿,时钟处于低电平,并且输出时钟保持低电平。它将保持低电平,直到所选时钟变低(以更新其控制寄存器)并变高。

在 Vivado 中实现这一点很简单。只需几行代码即可创建时钟切换。

library ieee; use ieee.std_logic_1164.all; entity clk_sw is port( clk_a : in std_logic; clk_b : in std_logic; sel : in std_logic; clk_out : out std_logic); end entity; architecture rtl of clk_sw is signal clk_a_reg : std_logic :='0'; signal clk_b_reg : std_logic :='0'; begin cntrl_a : process(clk_a) begin if falling_edge(clk_a) then clk_a_reg <= (not sel) and (not clk_b_reg); end if; end process; cntrl_b : process(clk_b) begin if falling_edge(clk_b) then clk_b_reg <= sel and (not clk_a_reg); end if; end process; clk_out <= (clk_a_reg and clk_a) or (clk_b_reg and clk_b); end architecture;

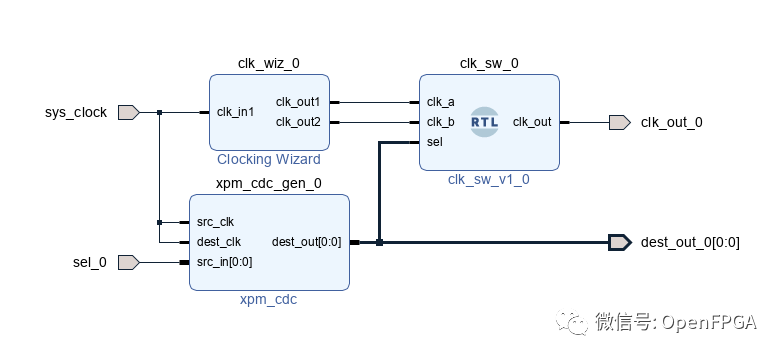

使用PLL将系统的时钟 (100MHz) 划分为两个随机且不相关的频率。输出时钟引出到GPIO 引脚 。

使用 100 MHz 的 XPM 同步器宏来对其进行去抖。XPM 宏的输出用于切换时钟并路由至 GPIO 引脚 。

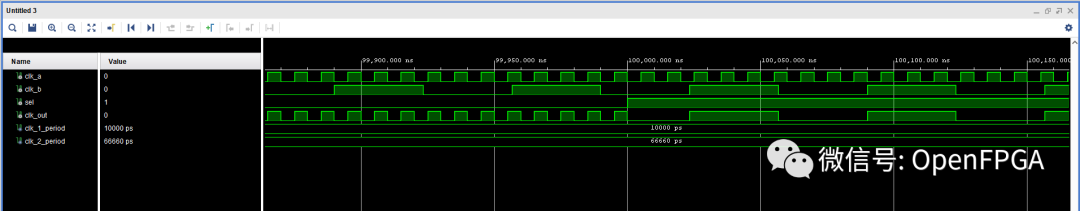

创建了一个简单的测试平台,可以在时序仿真中运行仿真,以确定实现中是否存在故障。

在上图中可以看到时序仿真中没有观察到任何故障。

下一步是对电路板进行编程,并观察在硬件中实现设计时设备中是否存在故障。

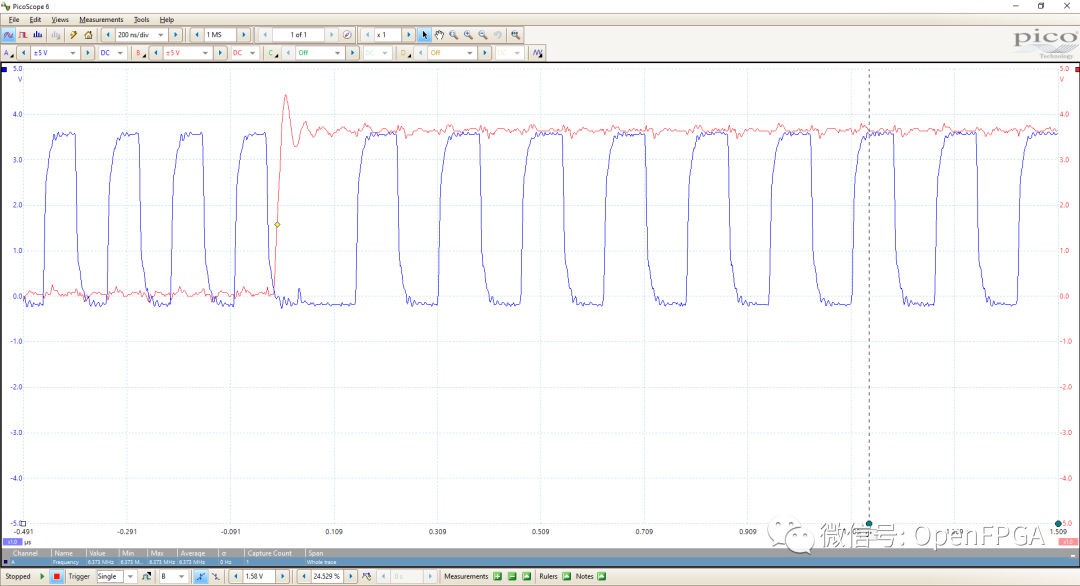

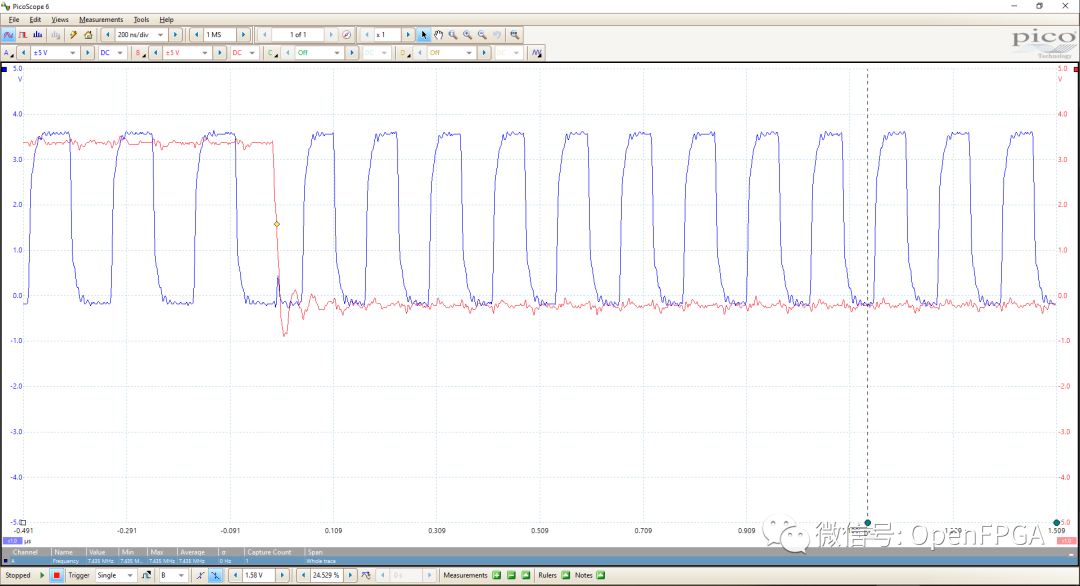

将频率设置为 6.25 MHz 和 8.125 MHz。默认情况下,当选择输入为低电平时,将输出 8.125 MHz 时钟。将其切换至高电平将输出切换至 6.25 MHz 时钟。

当然,我们需要能够确定切换发生时输出上是否存在任何毛刺。因此,使用示波器监测内部同步选择信号和时钟输出引脚。

从下面观察输出时钟时可以看出,当时钟的选择线改变时,在输出时钟线上没有观察到毛刺。

尽管现代 FPGA 包含更先进、功能更强大的时钟管理和时钟电路,但一些低端FPGA上这些电路并不存在,我们就需要自己去创建始终切换电路。

审核编辑:刘清

-

寄存器属于时序逻辑电路吗 寄存器是什么逻辑电路2024-02-18 3763

-

FPGA | 竞争冒险和毛刺问题2023-11-02 1237

-

直接修改寄存器来输出内部时钟的方法2023-09-19 388

-

简谈FPGA的竞争冒险和毛刺问题2023-05-30 1680

-

STM32寄存器点灯2021-12-08 1097

-

时钟毛刺注入攻击的研究分析综述2021-04-26 1351

-

详解移位寄存器,串行输入和串行输出的分析2020-09-24 34939

-

psoc4-4200装置是可能的CPU寄存器的输出路由到逻辑门的输入吗?2019-09-03 1896

-

MCU时钟设计方案2019-09-01 3285

-

传统的移位寄存器与光耦合器隔离移位寄存器有什么不同2019-08-12 3241

-

寄存器、锁存器和触发器的区别2018-07-03 4101

-

FPGA实战演练逻辑篇47:消除组合逻辑的毛刺2015-07-08 4277

-

寄存器与移位寄存器2010-03-12 984

-

消除组合逻辑产生的毛刺—PLD设计技巧2008-09-11 902

全部0条评论

快来发表一下你的评论吧 !