浅析UPF设计的debug过程

描述

景芯SoC用always on的power domain电压域的pwrdown_mux信号作为power switch cell的switch控制信号,但是设计里面有个小问题,不太算bug的bug,但对upf低功耗flow而言,毫无疑问就是bug!

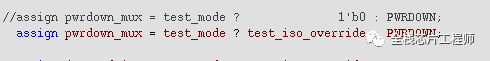

请登陆服务器追踪一下pwrdown信号,注意其负载情况,RTL代码如下:

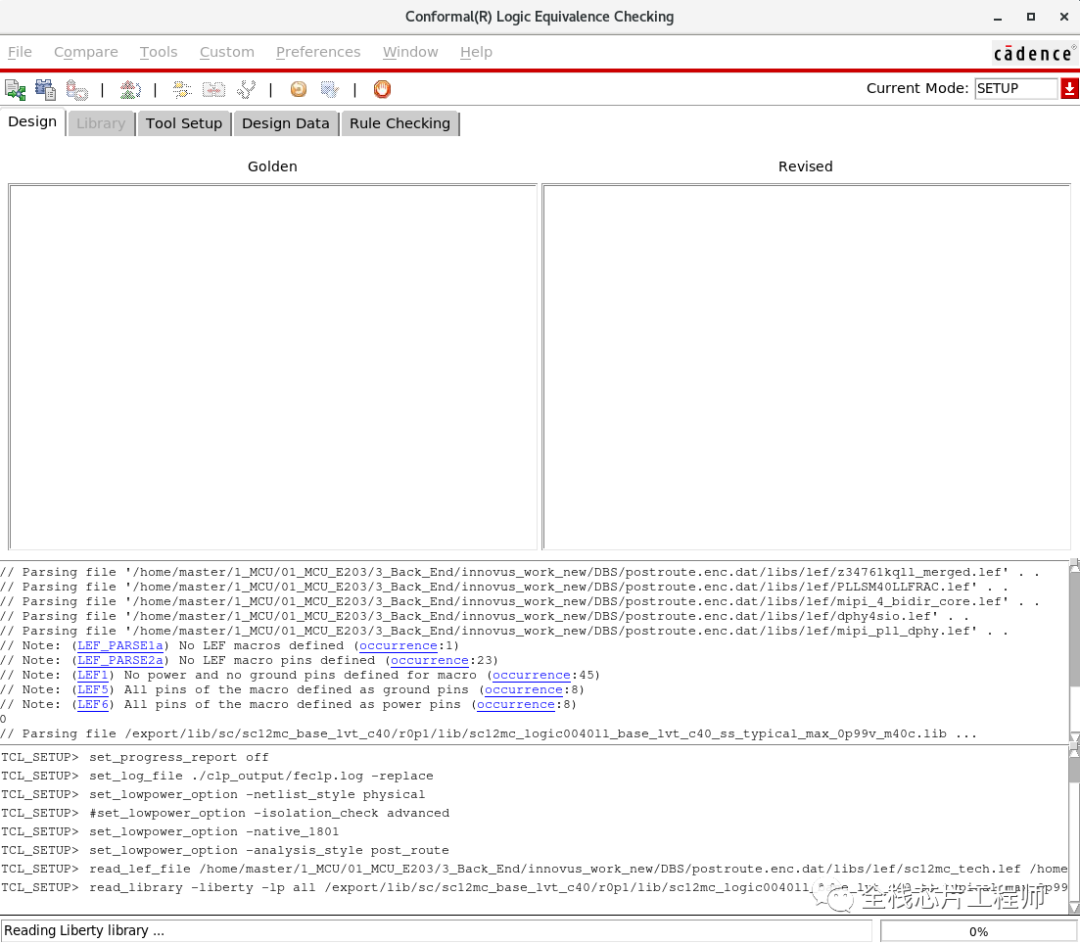

结合PR输出的netlist, 我们做个clp低功耗检查,脚本参见服务器。

可以发现,clp报错说power switch的switch控制信号找不到。不得不说,clp检查对低功耗而言多么重要,对芯片设计而言多重要!景芯SoC的价值就在把芯片设计全流程的这些细小的知识点,全部串接起来!犹豫啥?抓紧报名加入吧!

在芯片设计中端流程时,景芯SoC会插入UPF约束中的isolation等cell,但是无法插入power switch等cell,因此,作为power switch cell的控制信号pwrdown_mux在没有负载的情况下,会被裁员掉(优化掉),因此需要设置上面MUX器件为dont_touch或者使pwrdown_mux成为module的port并禁止auto_ungroup(并设置no_boundary_optimization),这样这个信号才能保留给后端,供后端实现power switch控制。

请学员完成代码修改,基于全套flow环境完成如下任务:

lint检查、前端仿真,

完成中端、后端flow,

完成clp检查, 完成后仿真

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ZXUN xGW边缘UPF BGP闪断的问题处理2024-12-23 1818

-

全球首个产线级5G工业UPF(OT-UPF)正式在汽车行业完成部署2024-05-10 3345

-

低功耗技术(三)UPF的使用2023-06-05 4855

-

double tail comparator的debug过程(一)2022-08-27 1826

-

一文解读多形态UPF2022-08-25 2700

-

小编科普一下关于低功耗UPF与CLP的使用方法2022-06-28 3719

-

浅析拉力传感器校准过程2022-03-11 3703

-

UPF流程与电源域Power Domain详解2021-10-20 9089

-

什么是UPF功率域和域边界?2021-09-29 3041

-

什么是UPF呢?2021-07-28 2739

-

浅析UPF功率域和域边界2021-07-26 2021

-

嵌入式系统内核引导启动过程浅析2017-10-30 1123

-

Mentor Graphics 使用UPF逐步求精方法推动新一代低功耗验证2015-09-14 1643

-

浅析高保真功率放大器的制作过程2014-03-25 2444

全部0条评论

快来发表一下你的评论吧 !