如何给每个RM添加约束?

描述

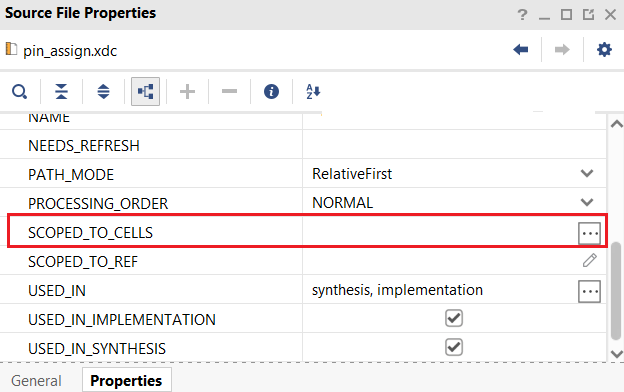

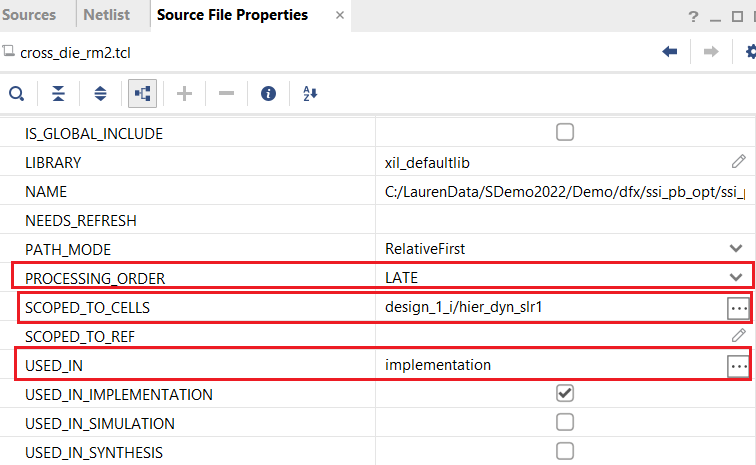

在常规非DFX(DynamicFunction eXchange)的Vivado设计中,我们可能会碰到给某一个指定的模块添加特定的约束。这时一个简单的方法就是将这些约束单独写在一个.xdc或.tcl文件中,然后将其添加到Vivado工程中,并将该约束文件的属性SCOPE_TO_CELLS设定为目标模块。如果该模块在设计中被多次实例化,不管这些实例化模块在设计中的层次如何,此时可设置该约束文件的属性SCOPE_TO_REF,如下图所示。这里我们就能理解对于一个cell其属性NAME和REF_NAME的区别:前者是实例化后的名字,后者为引用名(可以理解为Verilog的module name或VHDL的entityname)。另外,需要特别注意的是使用上述方法时,在.xdc或.tcl文件中的约束其施加的对象是以该指定模块作为顶层的而不是以实际工程的顶层作为顶层。如果采用Non-Project模式,那么可以通过read_xdc读入约束文件,然后通过set_property命令指定约束文件的属性SCOPE_TO_CELLS或者SCOPE_TO_REF。

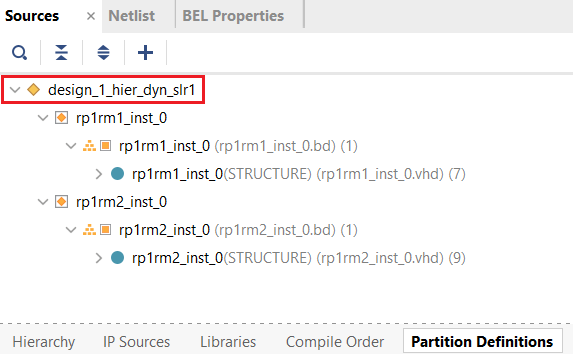

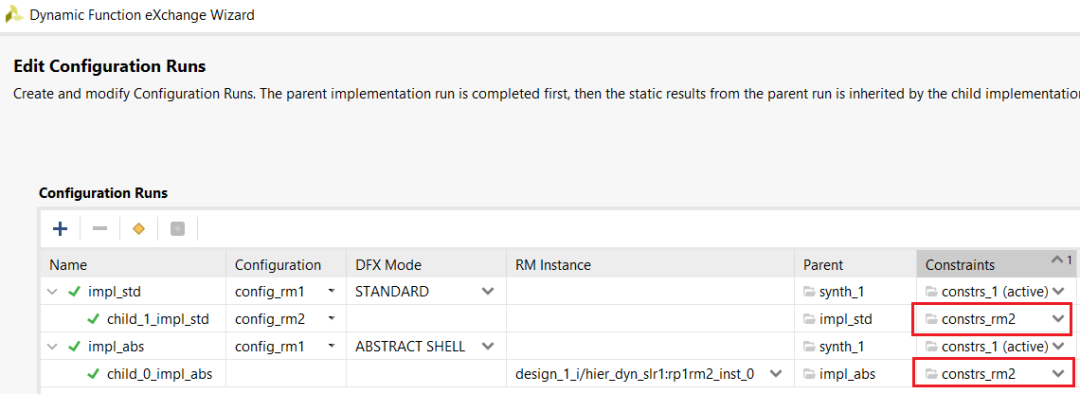

在DFX设计中,我们也会碰到类似的情形,即给同一个RP(Reconfigurable Partition)下的不同RM(Reconfigurable Module)添加不同的约束。这时要考虑几个因素:同一个RP下不管有几个RM,在设计中均对应同一个实例化的名字。这意味着不能仅仅通过SCOPE_TO_CELLS将这些约束对应到不同的RM上。另外,每个RM只有在自身对应的configuration上才有效,所以要保证在这个configuration上对应的RM的约束也要有效。从下图可以看到,当前这个DFX设计中有一个RP,名字为图中红色方框所示,该RP下有两个RM,分别为rp1rm1和rp1rm2。

基于上图所示DFX设计,现在我们要分别对rp1rm1和rp1rm2添加不同的约束。这里我们先介绍一下DFX设计的约束管理模式。在DFX设计中,约束是按configuration分组的。这是因为不同的configuration对应不同的RM。但不管有几个configuration,都会有主约束,也就是ParentRun对应的约束,默认在constrs_1下。主约束包括:顶层IO约束(管脚分配/电平设置/input delay/output delay)、全局时钟周期约束和每个RP的Pblock信息。主约束在运行Parent Run时生效,并在运行结束之后锁定静态区时一同被锁定,因此,后续的ChildRun会直接获得这些约束信息不需要重写一遍。默认情况下,Child Run并没有单独的ConstraintSet,也就没有单独的约束文件。如果要针对RM施加约束,而RM又出现在Child Run,就要建立新的Constraint Set,这需要如下几个步骤完成。

第一步:创建与指定RM相关的约束,这些约束应放在单独的.xdc文件中。

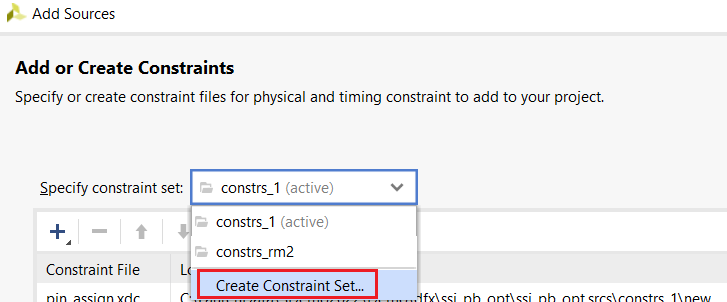

第二步:创建新的Constraint Set,并将第一步创建的约束文件添加到该Constraint Set下。

除了Parent Run之外,有几个ChildRun,如果这些Child Run里的RM又需要单独约束,那么就要创建几个Constraint Set。创建ConstraintSet的方法如下图所示。

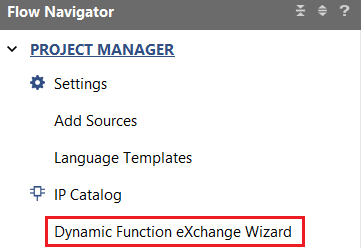

第三步:运行DFX Wizard到EditConfiguration Runs界面,如下图所示。在对应的Constraints列选择相应的Constraint Set,如图中红色方框所示。

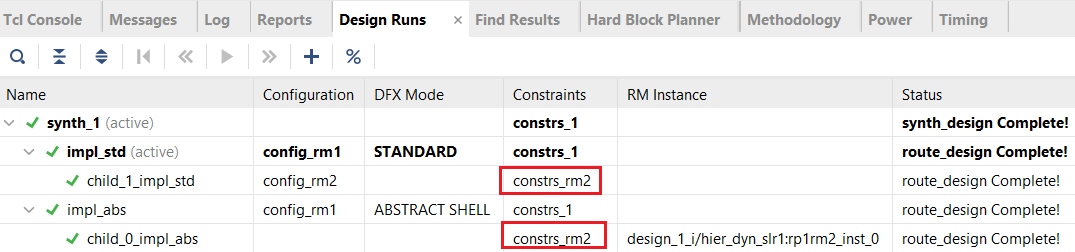

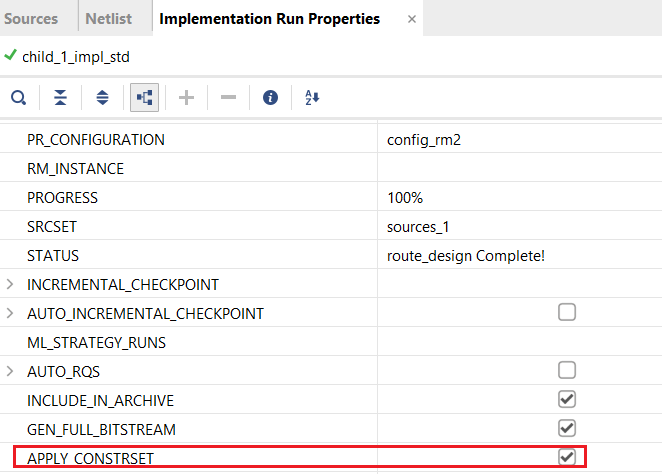

在Design Run窗口中就能看到相应的ChildRun对应的Constraint Set,如下图中的红色方框所示。如果没生效,要确保ChildRun的Property APPLY_CONSTRSET被勾选。

上述过程针对的是Vivado Project模式。在Non-Project模式下,当运行rp1rm2对应的Configuration时,要先打开锁定静态区布线信息的dcp(在这个dcp中,RP均为黑盒子),然后加载对rp1rm2OOC综合生成的dcp,这个过程结束之后即可通过read_xdc读入针对rp1rm2的约束文件。

针对RM的约束文件,通常要设定以下几个属性:PROCESSING_ORDER,SCOPED_TO_CELLS和USED_IN,如图中红色方框所示。

-

时序约束实操2024-04-28 3767

-

FPGA主时钟约束详解 Vivado添加时序约束方法2023-06-06 13011

-

如何给每个RM添加约束?对RM添加约束的步骤有哪些呢?2023-08-17 1750

-

一文详解Vivado时序约束2025-03-24 5102

-

时序约束2013-08-08 1757

-

怎么才能删除自动添加的时序约束?2019-11-04 2250

-

FPGA上设计系统应该添加任何约束吗?2020-05-22 2056

-

怎样给FPGA逻辑电路添加约束标签呢2022-07-22 2156

-

FPGA开发之时序约束(周期约束)2017-02-09 941

-

添加时序约束的技巧分析2017-11-25 3230

-

混合搜索的含逻辑“与”“或”的RM优化算法2017-12-25 982

-

如何理解和使用做FPGA设计时的过约束?2021-03-29 7155

-

如何在Vivado中添加时序约束2023-06-23 4435

-

如何在Vivado中添加时序约束呢?2023-06-26 6496

-

如何给TPU-MLIR添加新的算子2023-08-18 1825

全部0条评论

快来发表一下你的评论吧 !